용량성과 유도성 섭동구조를 함께 갖는 초고주파 전송선로의 설계

초록

본 논문에서는 용량성과 유도성 섭동구조를 함께 갖는 초고주파 전송선로 구조를 제시하였다. 용량성과 유도성 섭동구조를 얻기 위하여 각각 가유전체 기판구조와 결함 마이크로스트립 구조를 사용하였다. 표준형 전송선로에 비해, 가유전체 기판구조는 다수의 비어홀에 의하여 단위길이당 추가적인 커패시턴스를, 결함 마이크로스트립 구조는 패턴상에 삽입된 결함에 의하여 단위길이당 추가적인 인덕턴스를 제공하므로, 각각 등가적으로 유효유전율과 유효투자율을 증가시켜 전송선로의 길이 축소를 가져온다. 본 연구에서는 비유전율 2.2, 두께 31mils와 5mils인 기판으로 36mils 두께의 전송선로를 구성하여, 표준형 전송선로에 비하여 동일한 전기적 길이일 때 물리적 길이가 크게 줄어든 전송선로를 설계하고, 시뮬레이션과 측정을 통하여 비교 및 검증하였다.

Abstract

The structure of a microwave transmission line having both capacitive and inductive perturbation structures is proposed in this work. The substrate integrated artificial dielectric (SIAD) and defected microstrip structure (DMS) are adopted for the capacitive and inductive perturbation structures, respectively. Compared to the standard transmission line, the SIAD produces the additional capacitance due to the lots of metalized via-holes, and the DMS increased inductance caused by the inserted defective pattern. These structures provide the increased effective permittivity(εr) and permeability(μr), and result in the size-reduced transmission line. In this work, the dielectric substrates with the εr of 2.2 and thickness of 5 mils and 31 mils are adopted for 36-mil-thick SIAD and DMS structures. The length-reduction of the proposed transmission line is verified and compared from the simulation and measurement.

Keywords:

SIAD, DMS, transmission line, periodic structureⅠ. 서 론

다양한 형태의 마이크로파 대역용 전송선로가 사용되고 있는데, 마이크로스트립 선로, 스트립 선로, 동평면 도파관 및 선로, 슬롯 선로, 동축케이블, 사각형 및 원형도파관 등이 포함된다. 이중에서 성능은 상대적으로 뒤지지만, 설계 및 제작이 간단하고 비용이 저렴한 마이크로스트립 선로가 초고주파 대역용 회로나 시스템 제작에 널리 사용된다. 따라서 오랜 기간 동안 마이크로스트립 전송선로에 대한 연구가 많이 이루어져 왔다[1]. 한편 마이크로스트립 전송선로의 성능을 유지하면서도 길이를 줄여서 결과적으로 회로의 크기를 줄이는 연구도 많이 이루어져 오고 있다. 주어진 유전체 기판 조건하에서 어떤 특성 임피던스(Zo)에 대한 표준형 마이크로스트립 전송선로의 선폭, 유효유전율, 유효투자율은 당연히 어떤 고정된 값을 갖는다. 여기에 외부 섭동구조(Perturbation Structure)를 삽입하면, 단위 길이당 등가 인덕턴스나 커패시턴가 추가되므로 결과적으로 주어진 선폭에 대하여 특성 임피던스, 유효유전율, 유효투자율이 변하게 된다[2]-[5]. 또는 섭동구조가 삽입되면 주어진 선폭에 대하여 특성 임피던스가 변한다고 표현할 수도 있다. 어느 경우이든 외부 섭동구조에 의하여 전송선로의 물리적 길이는 줄어드는 방향으로 변하게 된다. 따라서 길이나 크기를 줄일 수 있다는 강력한 단서를 제공한다[4][6]-[8]. 종래에 마이크로스트립 선로에 삽입되었던 섭동구조의 대표적인 형태로 주기적 밴드갭 구조(PBG, Periodic Band Gap), 결함접지구조(DGS, Defected Ground Structure), 기판집적 가유전체(SIAD, Substrate Integrated Artificial Dielectric) 구조, 결함 마이크로스트립 구조(DMS, Defected Microstrip Structure) 등이 있으며, PBG, DGS, DMS는 주로 마이크로스트립의 단위 길이당 등가의 인덕턴스를 증가시키고, 기판집적 가유전체(SIAD, Substrate Integrated Artificial Dielectric)는 커패시턴스를 증가시킨다는 것이 선행 연구에서 밝혀졌다[2]-[4][9]. 어느 경우이든 등가의 인덕턴스 또는 커패시턴스를 증가시키므로 유효유전율 또는 유효투자율을 증가시켜서 동일한 전기적 길이일 때 물리적 길이를 감소시키는 결과를 얻을 수 있다.

본 연구에서는 마이크로스트립 선로의 단위 길이당 등가의 인덕턴스를 증가시키는 방법으로 DMS를 채택하고, 여기에 등가의 커패시턴스 증가 효과를 동시에 얻기 위하여 SIAD를 결합한 전송선로 구조를 제안한다. 단위 길이당 인덕턴스 증가방법으로 종래에 많이 사용되었던 PBG, DGS는 성능이 우수하다는 장점이 있는 반면에, 구현 방법이 까다롭거나 기판의 바닥 접지면에 구현하기 때문에 구현과정이 불편하다는 단점이 지적되었다. 이를 해결하기 위한 방편으로 본 연구에서는 PBG, DGS와 유사한 특성을 얻으면서도 구현방법이 상대적으로 쉬운 DMS 구조를 등가 인덕턴스 증가 구조로 채택한다. DMS 구조는 마이크로스트립 선로의 윗면 패턴상에 구현되므로 바닥의 접지면을 건드리지 않아서 종래의 단점을 극복할 수 있다. 본 연구에서 설계될 전송선로 구조의 상면과 하면에는 각각 등가의 인덕턴스와 커패시턴스를 증가시키는 섭동구조인 DMS와 SIAD가 함께 삽입된다. 두 개의 섭동구조가 삽입되므로 어느 하나의 섭동구조만 삽입되는 경우보다 선로의 길이를 더욱 감소시킬 수 있다. 또한 등가의 인덕턴스와 커패시턴스를 동시에 증가시키는 구조이므로 유효투자율과 유효유전율이 함께 증가하게 되어, 표준형 전송선로의 선폭과 비교할 때 Zo에 따른 선폭의 변화가 어느 하나의 섭동구조만을 삽입하는 경우보다 완만하다. 그러므로 실제 회로에 적용할 경우 크기가 줄어들면서도 선폭 변화가 크지 않으므로 구현의 편리성이 더욱 좋아진다.

Ⅱ. 등가 커패시턴스형 섭동 구조: SIAD

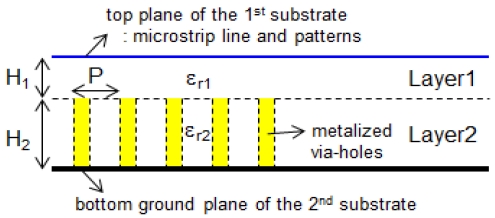

SIAD 구조는 선행연구를 통하여 제안되고 설명된 바 있다[4][10]. 그림 1은 SIAD 구조를 이해하기 쉽게 그림으로 표현한 것이다. 기판의 상면 전송선로 패턴은 두께가 H1인 유전체 기판에 구현된 표준형 선로구조와 같다(Layer1) SIAD의 특징은 두께가 H2인 제 2의 유전체 기판 층에 다수의 도금된 비어홀(Metalized via-holes)을 주기적으로 형성시킨다는데 있다(Layer2).

전송선로의 단위 길이당 등가의 인덕턴스와 커패시턴스를 각각 L,C라 할 때, 식 (1)은 특성 임피던스의 표현식이다. SIAD 구조에서는 다수의 비어홀에 의하여 단위 길이당 등가 커패시턴스의 중가가 우세하므로 유전체만 있는 경우에 비하여 특성 임피던스가 낮아지고 된다. 만약에 SIAD 구조를 삽입한 이후에 이전과 동일한 값의 특성 임피던스를 유지하려면 선폭을 증가시켜야 할 것이다.

| (1) |

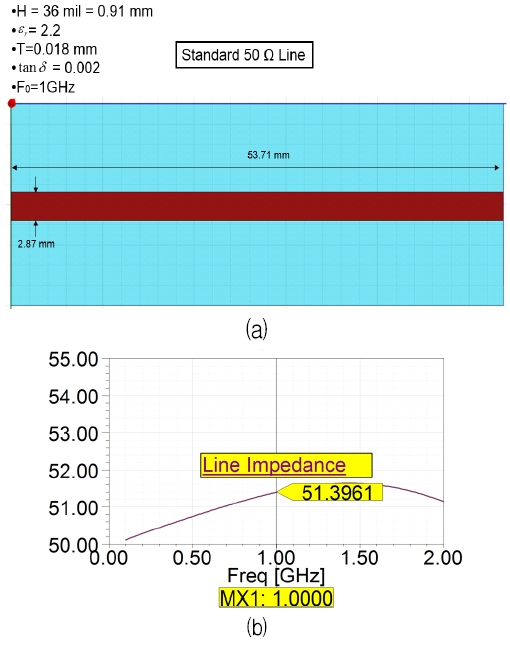

설계 결과를 비교하기 위하여 표준형 50Ω 선로와 SIAD 구조를 적용한 50Ω 선로를 설계하여 비교해 보았다. 그림 2(a)는 50Ω 표준형 마이크로스트립 전송선로이다. 설계에 사용된 기판은 비유전율이 2.2이고 두께가 36mils이다. 비교의 편의상 중심주파수를 1GHz로 설정하였다. 1GHz에서 50Ω 선로의 선폭과 λ/4의 물리적 길이는 각각 2.87㎜, 53.71㎜이다.

회로 설계 시뮬레이터인 ADS(Advanced Design System)의 전송선로 계산 툴을 이용하여 선로의 폭과 길이를 결정하였다. 그리고 설계의 정확성을 높이기 위하여 전자기 시뮬레이터인 HFSS(High Frequency Structure Simulator)로 검증하였다. 그 결과 그림 2(b)에 제시한 것처럼 51.396Ω의 특성 임피던스가 계산되었다. 50Ω에 근접한 특성 임피던스가 계산되었는데, 이를 50.0Ω으로 맞추기 위한 추가적인 수고는 하지 않았음을 밝힌다.

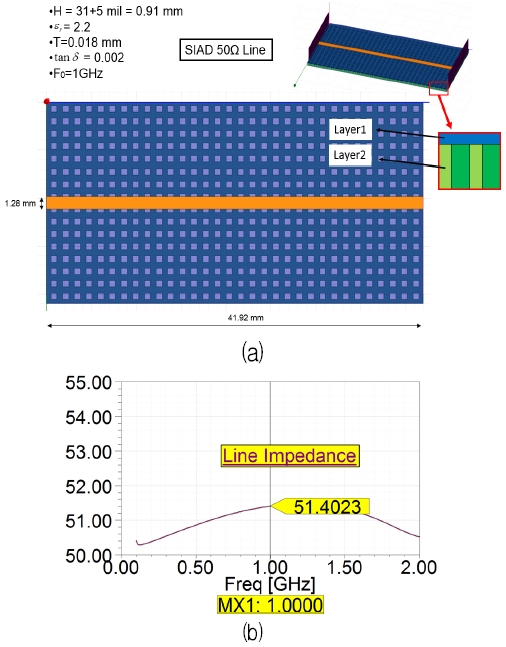

그림 3(a)는 기판집적 가유전체 구조를 이용하여 설계한 마이크로스트립 전송선로를 보여주고 있다.

그림 2에서와 같은 2.2의 비유전율 조건하에서 동일하게 36mils 두께를 갖도록 기판1과 기판2의 두께를 각각 5mils, 31mils로 취했다. 여기에 사용된 비어홀의 지름과 간격은 각각 0.8㎜, 1.3㎜이다. 설계 결과 1GHz에서 50Ω SIAD 마이크로스트립 전송선로의 선폭과 λ/4의 물리적 길이는 각각 1.28㎜, 41.92㎜이다. HFSS로 검증한 결과 설계된 선로의 실제 특성 임피던스는 51.402Ω으로 계산되었다. 그림 3의 SIAD 전송선로는 그림 2의 표준형 선로에 비하여 현저하게 선폭과 길이가 줄어드는 것을 알 수 있다.

Ⅲ. 등가 인덕턴스형 섭동 구조: DMS

본 장에서는 등가의 인덕턴스를 증가시켜주는 구조인 DMS를 채택한 전송선로에 대하여 기술한다.

본 연구에서 사용하는 DMS는 그림 4(a)에 보인 것처럼 마이크로스트립 전송선로의 상면 선로상에 직접 결함패턴(Defect Pattern)을 삽입하는 구조를 갖는다. 결함을 삽입하면 신호의 전송경로가 길게 늘어나는 효과를 갖게 되므로 결과적으로 단위길이당 등가 인덕턴스와 전기적 길이가 늘어나게 된다. 따라서 동일한 전기적 길이를 유지하기 위하여 물리적 길이를 줄일 수 있게 된다.

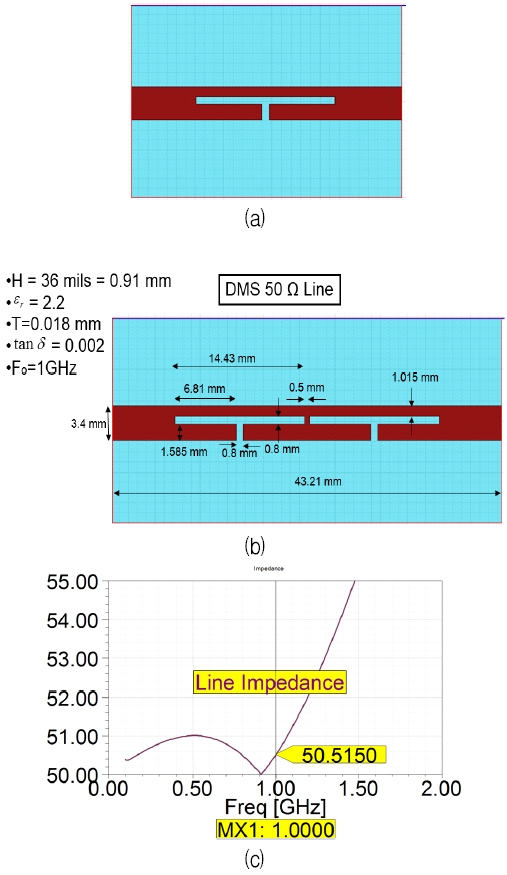

(a) Pattern of the DMS microstrip line, (b) Design of a 50Ω DMS microstrip line, (c) Calculated characteristic impedance

PBG나 DGS와 같은 종래의 인덕턴스 증가형 섭동 구조에서는 기판의 바닥 접지면에 섭동 구조를 삽입하기 때문에 기판의 구현 및 패키징 과정에서의 접지 접촉 문제가 심각하게 제기되었다[11]. 그러나 본 연구에서의 DMS 구조는 회로 패턴면에 삽입되므로 종래의 문제가 발생하지 않아서 회로의 구현이 훨씬 간편하다. 그림 2에서와 동일하게 2.2의 비유전율과 36mils의 두께를 갖는 유전체 기판에 대하여 그림 4(b)와 같이 50Ω DMS 마이크로스트립 전송선로를 설계하였다. 1㎓에서 선폭과 λ/4의 물리적 길이는 각각 3.4㎜, 43.21㎜였고, 특성 임피던스를 HFSS로 검증한 결과 50.515Ω으로 매우 유사한 결과를 얻었다. 이제 설계 결과를 그림 2, 그림 3의 결과와 비교해 보자. 표준형에 비하여 선로의 길이는 SIAD 구조에서든 DMS 구조에서든 모두 줄어들었다. 그런데 50Ω 선로의 선폭은 표준형 2.87㎜에서 SIAD 구조에서는 1.28㎜로 감소하였고, 그리로 DMS 구조에서는 반대로 3.4㎜로 증가하였다. 따라서 커패시턴스와 인덕턴스 증가형 섭동구조로 SIAD와 DMS구조를 함께 사용하면 (1)보다 우수한 선로의 길이 축소 가능성, (2)표준형 전송선로의 선폭과 유사하게 전송선로의 선폭 가능성이라는 장점을 얻을 수 있을 것으로 예측할 수 있다.

Ⅳ. 등가 커패시터스형과 인덕턴스형 섭동구조가 함께 사용된 선로 : SIAD-DMS

제 2, 3장을 통해 표준형 전송선로에 SIAD나 DMS 구조가 결합될 때 단위길이당 등가의 커패시턴스나 인덕턴스가 증가하여 전송선로의 특성 임피던스가 감소 또는 증가하는 특징이 있음을 설명하였다. 만일 SIAD나 DMS 구조를 삽입한 이후에 애초의 특성 임피던스 값을 유지하려면 선폭을 줄이거나 늘리는 조치를 취해야 한다. 따라서 섭동구조의 삽입에 따른 길이 감소의 효과는 있으나, 동시에 전송선로의 선폭에 큰 변화가 있다는 문제가 발생한다.

따라서 본 장에서는 SIAD나 DMS 구조를 동시에 삽입하여 설계된 전송선로에 대하여 설명한다. 이미 살펴보았다시피 두 섭동구조는 전송선로의 특성 임피던스를 감소 또는 증가시키는 상보적인 특징을 가지고 있으면서도 공통적인 효과로는 동일한 전기적 길이 대비 물리적 길이를 크게 감소시키는 특징을 가지고 있다. 따라서 두 구조를 동시에 사용하면 표준형 전송선로와 비교할 때 어떤 특성 임피던스에 대한 선폭을 비슷하게 유지하면서도 물리적 길이를 크게 줄이는 장점을 얻을 수 있다.

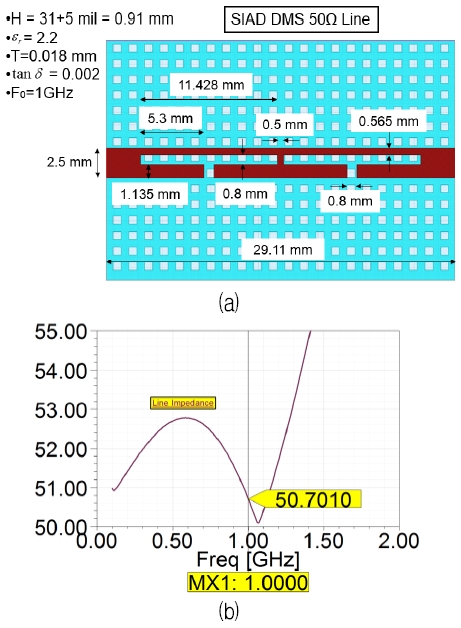

그림 5(a)는 SIAD와 DMS 구조를 모두 표준형 마이크로스트립 전송선로에 삽입하고 특성 임피던스가 50Ω이 되도록 설계한 결과를 보여주고 있다. 선폭은 2.5㎜인데, 그림 2(a)에서 보인 2.87㎜와 가장 근접한 수치를 지닌다. 또한 그림 3(a)와 그림 4(a)에서 보인 50Ω 선로들의 선폭들과도 비교될 만한 수치이다. 설계한 50Ω SIAD-DMS 전송선로를 HFSS로 검증한 결과 50.701Ω이라는 특성 임피던스 값을 얻었다. 1GHz에서 λ/4의 물리적 길이는 29.11㎜인데, 이 역시 상기에 설명한 값들보다 현저하게 짧은 치수이다. 두 섭동구조의 길이 감소 효과가 더해져서 같은 λ/4에 대해 더욱 짧은 선로를 얻은 것이다. 따라서 제안한 전송선로 구조를 초고주파 대역용 회로 설계에 응용하면 현저하게 길이가 줄어든 회로를 얻을 수 있다는 것을 예상할 수 있다. 상기에서 설명한 전송선로들의 몇 가지 치수들을 쉽게 비교하기 위하여 표 1에 정리하였다.

Ⅴ. SIAD-DMS 전송선로의 제작 및 측정

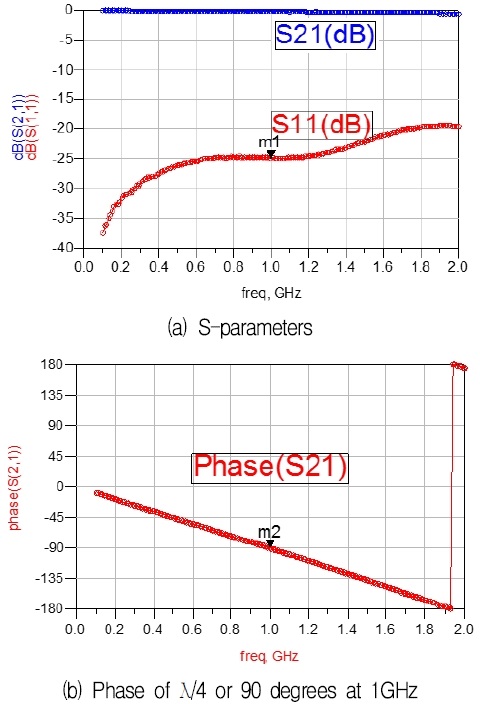

본장에서는 그림 5(a)처럼 설계한 기판집적 가유전체와 결함 마이크로스트립 섭동 구조(SIAD-DMS)를 지난 전송선로를 실제로 제작하고 측정한 결과를 기술하고자 한다. 그림 6은 제작을 위한 전송선로의 레이아웃과 실제 제작 사진을 보여주고 있다. 사진에는 Layer1에 해당하는 DMS 패턴만 보이지만, Layer2에 해당하는 SIAD 부분이 아랫면에 존재한다. 실제 측정을 위하여 초고주파 신호용 컨넥터를 연결하였다. 그림 7(a)는 실제로 측정한 S-파라미터 특성을 보여준다. 중심주파수 1㎓에서 S21과 S11이 각각 0dB 근처와 –25dB 근처로 측정되었다. 두 가지의 섭동구조를 삽입하였음에도 불구하고 전송선로로서 손실이 매우 적고 반사계수도 낮다는 것을 알 수 있다. 따라서 초고주파 대역 전송선로로의 전달특성은 검증되었다고 할 수 있다.

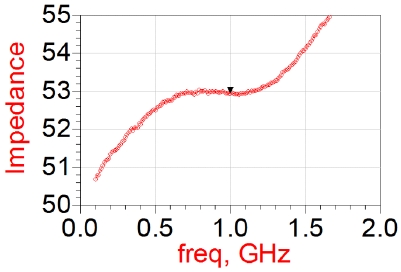

그림 7(b)는 측정한 S21의 위상값을 보여주고 있는데, 1GHz에서 90도를 지니므로 정확하게 λ/4임을 보여주고 있다. 따라서 그림 5(a)에 보인 29.11㎜의 길이를 다른 전송선로 구조와 비교하면, 현저하게 짧은 길이를 가지면서도 정확하게 λ/4를 구현하고 있음을 알 수 있다. 특성 임피던스 관점에서 보면, 단자(Port) 임피던스가 50Ω으로 연결되어 있으므로 전송선로가 완벽한 50Ω에 가까우면 S11은 -∞에 가까운 값을 가져야 한다. 그러나 실제로는 –25dB 정도로 측정되었으므로 이상적인 50Ω에서 약간 벗어났음을 알 수 있다. 이를 종래에 알려진 특성 임피던스 계산법으로 구해 보았다[12]. 그림 8은 제작한 전송선로의 특성 임피던스가 실제로 53Ω임을 보여주고 있다. HFSS를 이용한 전자기적 시뮬레이션 결과 50.7Ω으로 예측되었는데, 실제로 측정한 결과는 이로부터 크게 벗어나지 않았음을 알 수 있다. 회로의 제작 과정을 수작업에 의한 대학실험실 수준의 프로토타입(In-house Prototype) 제작 설비에 의존한 결과이지만, 매우 유의미한 측정 및 계산 결과라 할 수 있다. 본 연구에서는 50Ω 선로뿐만 아니라, 초고주파 대역 회로 설계에 널리 쓰이는 특성 임피던스인 35Ω과 70Ω 선로에 대해서도 동일한 설계 방법을 적용하여 설계하고 그 결과를 표 2에 정리하였다.

Calculated characteristic impedance from the measured S-parameters of the 50Ω SIAD-DMS microstrip line

그 결과 50Ω에서와 마찬가지로 두 가지 섭동구조를 모두 삽입한 경우에 표준형 전송선로의 선폭과 가장 유사하면서도 전송선로의 실제 길이는 현저하게 짧아짐을 알 수 있다.

따라서 본 연구에서 제안한 전송선로를 실제 초고주파 대역 회로 설계에 적용하면 동일한 특성에 크기가 현저하게 줄어든 소형화된 회로를 얻을 수 있을 것으로 기대할 수 있다.

Ⅵ. 결 론

본 연구에서는 초고주파용 전송선로의 단위길이당 등가 커패시턴스와 인덕턴스를 부가시키는 섭동구조인 기판집적 가유전체(SIAD)와 결함 마이크로스트립 구조(DMS)를 동시에 적용한 전송선로에 대하여 기술하였다. 두 구조를 적용하면 동일한 주파수에서 어느 한 가지 섭동구조만을 결합하는 경우보다 현저히 길이가 줄어든 전송선로를 얻을 수 있음을 시뮬레이션과 측정을 통하여 확인하였다. 그러면서도 제안하는 전송선로의 선폭은 섭동구조를 삽입하지 않는 표준형 마이크로스트립 전송선로의 선폭과 가장 유사한 치수를 가진다는 것을 알 수 있었다. 이는 등가의 커패시턴스와 인덕턴스 효과를 제공하는 두 섭동구조가 서로 상보적으로 특성 임피던스의 감소와 증가를 견제하기 때문에 얻어지는 장점이다. 제안하는 전송선로의 실제 특성 임피던스를 전자기적 시뮬레이션 및 측정을 통해서 얻은 결과, 예로써 50.7Ω 전송 선로의 경우 53Ω 특성을 보였는데, 이는 제작과정에서 발생하는 오차와 다소 정밀도가 떨어지는 공정기술임을 감안해도 S11이 –25dB 수준이어서 회로 설계시 사용이 가능한 값이다. 또한 본 연구과정에서는 초고주파 대역용 전송선로로 널리 사용되는 35Ω과 70Ω 선로에 대해서도 설계를 하여, 유사한 정밀도의 전송선로를 얻었다. 어느 임피던스의 경우에서든 두 가지 섭동 구조를 모두 사용한 경우가 어느 한 가지만을 사용한 경우보다 현저하게 전송선로의 길이라 짧았다. 제안하는 전송선로를 이용하여 향후에 초고주파 대역에서의 무선통신용 회로 설계시 종래의 전송선로를 이용한 경우보다 현저하게 크기가 작은 회로를 설계할 수 있을 것으로 기대된다. 저자들은 이 분야의 연구를 계속하여 향후에 얻는 연구 결과를 지속적으로 발표할 예정이다.

Acknowledgments

본 연구는 2016년도 정부(미래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 기초연구사업임.(No. NRF-2016R1C1B1013862)

References

- K. C. Gupta, R. Garg, I. Bahl, and P. Bhartia, "Microstrip Lines and Slotlines, 2nd edition", Ch. 1 and Ch. 2, Artech House, Boston, p83-85, (1996).

-

V. Radisic, Y. Qian, R. Coccioli, and T. Itoh, "Novel 2-D Photonic Bandgap Structure for Microstrip Lines", IEEE Microwave Guide Wave Letters, 8(2), p69-71, Feb.), (1998.

[https://doi.org/10.1109/75.658644]

- C. S. Kim, J. S. Park, D. Ahn, and J. B. Lim, "A Novel 1-D Periodic Defected Ground Structure for Planar Circuits", IEEE Microwave Guide Wave Letters, 10(4), p131-133, Apr.), (2000.

-

M. Coulombe, H. V. Nguyen, and C. Caloz, "Substrate Integrated Artificial Dielectric (SIAD) Structure for Miniaturized Microstrip Circuits", IEEE Antennas and Wireless Propagat. Lett., 6, p575-579, Dec.), (2007.

[https://doi.org/10.1109/lawp.2007.910959]

-

T. Y. Yun, and K. Chang, "Uniplanar One-Dimensional Photonic-Bandgap Structures and Resonators", IEEE Trans. Microwave Theory Tech., 49(3), p549-553, Mar.), (2001.

[https://doi.org/10.1109/22.910561]

- F. R. Yang, K. P. Ma, Y. Qian, and T. Itoh, "A Uniplanar Compact Photonic-Bandgap (UC-PBG) Structure and its Applications for Microwave Circuits", IEEE Trans. Microwave Theory Tech., 47(8), p1509-1514, Aug.), (1999.

-

J. Lim, S. M. Han, W. S. Yoon, and K. Choi, "Design of a 4-Way Power Divider Using the Multi-Layered Stripline and Defected Ground Structure", Journal of KIIT, 14(1), p11-18, Jan.), (2016.

[https://doi.org/10.14801/jkiit.2016.14.1.11]

-

J. Lim, W. S. Yoon, H. Choi, S. M. Han, and D. Ahn, "Design of a Branch Line Coupler Using Stripline and Common Defected Ground Structure", Journal of KIIT, 16(4), p87-93, Apr.), (2018.

[https://doi.org/10.14801/jkiit.2018.16.4.87]

- G. Chaudhary, Y. Jeong, J. Lim, C. Kim, D. Kim, J. Kim, and J. Park, "DMS harmonic termination load network for high efficiency power amplifier applications", Proceedings of the 40th European Microwave Conference, Paris, p946-949, Sep.), (2010.

-

J. Lim, K. Kwon, S.M. Han, D. Ahn, and Y. Jeong, "Design of A Branch Line Coupler Using Double-Sided Artificial Dielectric Substrate Structure", Journal of KIIT, 13(4), p45-52, Apr.), (2015.

[https://doi.org/10.14801/jkiit.2015.13.4.45]

- J. Lim, D. Ahn, S.M. Han, Y. Jeong, and H. Liu, "A Defected Ground Structure without Ground Contact Problem and Application to Branch Line Couplers", International Journal of Antennas and Propagation, 2013, Article ID 232317.

- J. Lim, J. Lee, J. Lee, Y. Jeong, S.M. Han, K. S. Choi, and D. Ahn, "Calculation of Characteristic Impedance of Transmission Lines with Substrate Integrated Artificial Dielectric Structures", in Proc. IEEE TENCON 2010, p1632-1635, Nov. 2010, Japan.

1991년 2월 : 서강대 전자공학과(공학사)

1993년 2월 : 서강대 대학원 전자공학과(공학석사)

2003년 2월 : 서울대 대학원 전기컴퓨터공학부(공학박사)

1993년 2월 ~ 2005년 2월 : 한국전자통신연구원 선임연구원

2005년 3월 ~ 현재 : 순천향대학교 전기공학과 재직중

관심분야 : 초고주파 무선 회로/부품 설계, 능동/수동 소자 모델링 및 회로 응용, 주기 구조의 모델링 및 회로 응용 등

1997년 2월 : 고려대 전파공학과(공학사)

1999년 2월 : 고려대 대학원 통신시스템공학과(공학석사)

2010년 8월 : 고려대 대학원 컴퓨터·전파통신공학과(공학박사)

1999년 3월 ~ 2015년 8월 : 한화탈레스(現 한화시스템) 통신연구소 수석연구원

2015년 9월 ~ 현재 : 호서대학교 전자디스플레이공학부 재직중

관심분야 : RF transceivers, Reconfigurable antenna systems, RF sensor systems 등

1996년 2월 : 고려대 전파공학과(공학사)

1998년 8월 : 고려대 대학원 전파공학과(공학석사)

2003년 8월 : 고려대 대학원 전파공학과(공학박사)

2003년 10월 ~ 2004년 11월 : UCLA Post Doctoral Research Fellow

2005년 1월 ~ 2007년 8월 : 삼성종합기술원 전문연구원

2007년 9월 ~ 현재 : 순천향대학교 정보통신공학과 재직중

관심분야 : RF 시스템, Low power RF transceivers, Active integrated antenna systems 등

1984년 2월 : 서강대 전자공학과(공학사)

1986년 2월 : 서강대 대학원 전자공학과(공학석사)

1990년 8월 : 서강대 대학원 전자공학과(공학박사)

1990년 8월 ~ 1992년 8월 : 한국전자통신연구원 선임연구원

1992년 9월 ~ 현재 : 순천향대학교 전기공학과 재직중

관심분야 : RF, 마이크로파 수동소자 해석 및 설계