패키지 구조에 따른 PIN 다이오드 특성 분석

초록

본 논문에서는 PIN 다이오드의 패키지 구조 및 재질에 따른 기생 성분의 차이와 이로 인한 PIN 다이오드의 전기적 특성의 변화에 대해 분석한 결과를 기술하였다. PIN 다이오드는 전력 제한기를 구성하는 핵심 소자이며, 일반적으로 낮은 삽입손실 특성이 요구된다. 하지만, PIN 다이오드 칩을 패키징할 때 발생하는 기생 커패시턴스에 의해 삽입손실 특성이 저하된다. 패드의 구조와 기판의 유전율이 서로 다른 3종류의 패키지를 제안하고, 각 패키지에서 기생 성분의 차이가 발생하는 것을 시뮬레이션과 실험 결과를 통해 제시하였다. 제작된 PIN 다이오드의 기생 커패시턴스 값은 75.825~127.259 fF로 나타났으며, PIN 다이오드의 기생 커패시턴스 값과 전력 제한기의 삽입손실이 비례하는 것을 확인하였다.

Abstract

This paper presents an analysis of the effects of package structure and material on the parasitic elements and electrical characteristics of PIN diode. PIN diodes are essential components in limiters and are required to have low insertion loss. However insertion loss of PIN diode can be degraded due to parasitic capacitance that occurs during the packaging of PIN diode chips. We demonstrated through simulation and experimentation differences in parasitic components occur in three types of packages with different substrate dielectric constants and pad structures. The measured parasitic capacitance of the proposed PIN diodes were from 75.825 to 127.259 fF, and it was shown that the parasitic capacitance value of the PIN diode is proportional to the insertion loss of the limiter.

Keywords:

PIN diode, power limiter, parasitic element, package, insertion lossⅠ. 서 론

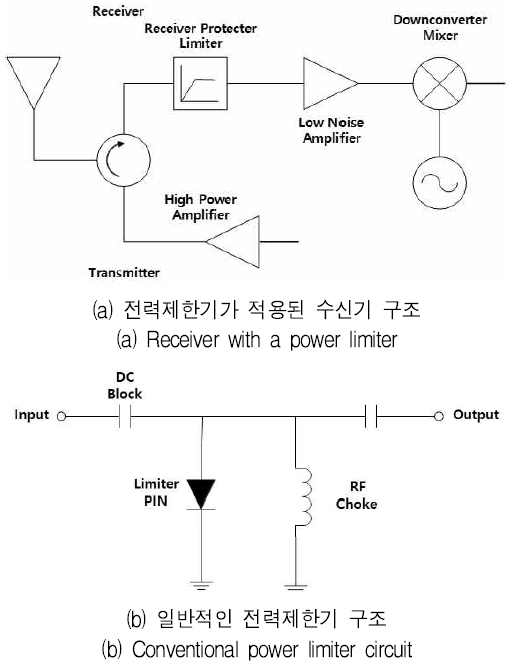

PIN 다이오드는 P-N 접합으로 구성된 다이오드와 달리 P층과 N층 사이에 진성 영역(Intrinsic region) 층이 삽입된 P-I-N 형태로 구성된다. PIN 다이오드는 P-N 접합 다이오드에 비해 고속으로 동작하며 낮은 손실 특성을 가지므로 RF/Microwave 시스템에 사용된다[1]-[5]. RF/Microwave 수신기는 무선 채널을 거치며 감쇄된 작은 신호를 입력받아 증폭을 통해 적정한 신호 레벨을 만들게 되므로 저전력 소모를 줄이기 위해 1dB 이득 억압점이 낮은 소자를 사용하게 된다. 따라서 외부로부터 원하지 않는 큰 신호가 수신기에 유입되거나 고출력 송신 신호가 수신기로 입력될 경우 수신기의 저전력 증폭기 등이 손상될 수 있다. 이를 방지하기 위하여 그림 1(a)와 같이 수신기의 입력단에 전력 제한기를 사용하게 된다[6]. 일반적으로 전력 제한기는 PIN 다이오드를 이용하여 그림 1(b)에 나타낸 것과 같은 형태로 구성한다. 이때 PIN 다이오드는 입력 전력에 의해 직렬 저항값 RS가 변하는 소자로 동작하게 된다. 낮은 전력이 입력되는 조건에서는 PIN 다이오드의 저항값이 매우 커지게 되어 전력이 통과되며, 높은 입력 전력이 인가되면 저항값이 작아지게 되어 입력 전력을 반사하게 된다.

전력 제한기에서 가장 중요한 성능 요소인 전력 제한 특성은 PIN 다이오드의 크기, 재질 등에 의해 결정된다. 정상적인 상황 즉, 낮은 전력이 입력되는 상황에서는 입력 전력이 수신부에 잘 전달되어야 하므로, 수신부의 잡음지수 및 G/T 성능을 높이기 위해 전력 제한기는 낮은 삽입 손실이 요구된다. 삽입손실 특성은 PIN 다이오드 칩의 직렬 저항 RS 및 접합 커패시턴스 CJ 등에 의해 결정되나, PIN 다이오드 칩을 패키징하여 사용할 때는 패키지의 구조 및 재질에 의해 기생 성분도 발생하므로 이에 의한 영향도 필수적으로 고려해야 한다[7][8].

본 논문에서는 패키지 구조 및 재질에 따른 PIN 다이오드의 기생 성분의 차이를 모델링 통하여 분석하고, 이로 인한 RS , 삽입손실 등을 측정한 다음 비교 분석하였다. 이를 통하여 PIN 다이오드의 RF 시스템 적용 시 주의점들을 분석해 보았다.

Ⅱ. 패키지 구조에 따른 기생성분 분석

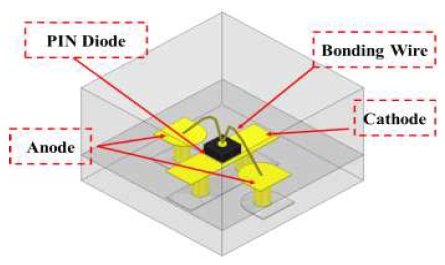

본 논문에서 제안하는 PIN 다이오드의 SMD(Surface Mount Device) 패키지 구조를 그림 2에 나타내었다.

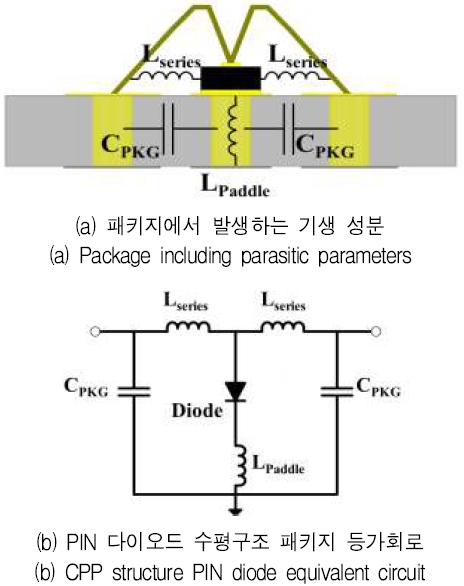

PIN 다이오드 패키지는 그림 3(a)에 모델로 나타낸 것과 같이 2개의 애노드(Anode) 패드와 1개의 캐소드(Cathode) 패드로 구성된다. PIN 다이오드 Bare chip의 캐소드 전극은 패키지의 캐소드 패드 위에 위치하며, 패키지의 애노드 패드와 PIN 다이오드의 애노드 전극은 본딩 와이어(Bonding wire)로 연결된다. 이로 인해 발생하는 패키지 내부의 기생 성분들은 그림 3(b)의 등가회로로 나타낼 수 있다. 애노드 패드와 본딩 와이어에 의해 Lseries, 캐소드 패드의 비아 홀(Via hole)에 의해 Lpaddle이 발생하며, 애노드 패드와 캐소드 패드 사이에 커패시턴스 Cpkg가 형성된다. 일반적으로 식 (1)~(3)에 의해 나타낸 것과 같이 본딩 와이어에 의한 인덕턴스 Lwire는 본딩 와이어의 투자율(μw), 반지름(r), 길이(l)에 의해 결정되며, 비아 홀에 의한 인덕턴스 Lvia는 비아 홀의 투자율(μv), 직경(D), 길이(L)에 의해 결정된다. 애노드와 캐소드 패드 간 커패시턴스 Cpad는 패드 간 거리(d), 마주 보는 면적(A), 패키지의 유전율(ε)에 의해 달라지게 된다.

| (1) |

| (2) |

| (3) |

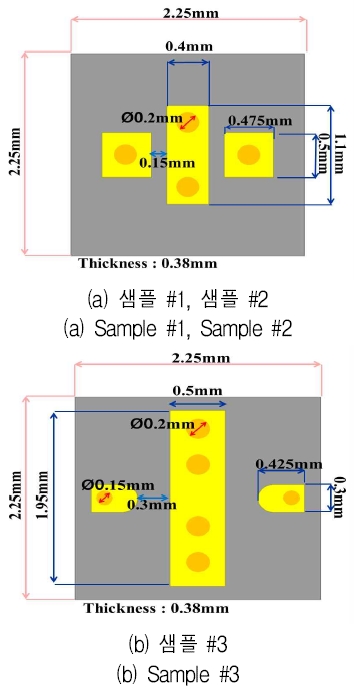

그림 4에 나타낸 3종류의 각기 다른 패키지에 대하여 패키지 구조 및 재질에 따른 기생 성분들의 차이를 Ansys사의 Q3D Extractor를 사용하여 분석하였다. 제안한 패키지는 3종류 모두 2.25⨯2.25 mm2의 면적을 가지며, 패키지 높이는 0.38 mm이다. 샘플 #1과 샘플 #2는 애노드 패드와 캐소드 패드의 형태와 패드 간 거리는 0.15 mm로 동일하나 패키지에 사용한 기판의 재질을 서로 다르게 설정하였다. 샘플 #1은 상대 유전율(εr)이 9.8인 Al2O3를 기판으로 적용하였으며, 샘플 #2는 상대 유전율이 4.4인 FR4를 적용하였다. 샘플 #3은 샘플 #1, #2와 달리 캐소드 패드와 애노드 패드 간 거리를 0.3 mm로 늘리고, FR4를 기판으로 사용하였다. 본딩 와이어는 각 패키지 구조에서 0.2 mm로 동일한 굵기를 적용하였으나, 패드 간 거리에 따라 본딩 와이어의 길이에 차이가 발생하였다. 각 구조별로 발생하는 기생 성분들에 대한 시뮬레이션 결과를 표 1에 나타내었다.

Cpkg는 샘플 #1이 0.199 pF, 샘플 #2는 0.163 pF, 샘플 #3은 0.134 pF으로 나타났으며, 기판의 상대 유전율이 작을수록, 또한 캐소드 패드와 애노드 패드 간 거리가 멀수록 기생 커패시턴스가 작아지는 것을 확인할 수 있었다. 그러나 패드 간의 거리가 너무 멀어지면 인덕턴스 성분도 늘어나고 패키지도 커지게 된다. 기생 인덕턴스 성분은 샘플 3개 모두 Lseires는 0.892 ~1.07 nH로, Lpaddle은 0.096~0.109 nH로 패키지 구조 및 재질에 크게 관계없이 소폭의 차이가 발생하는 결과를 얻을 수 있었다.

Ⅲ. 다이오드 구현 및 전기적 특성 측정

II장에서 제안한 3종류의 패키지 구조를 이용하여 PIN 다이오드를 제작하고 전기적 특성을 측정한 다음 시뮬레이션 결과와 비교 분석하였다. 구현된 패키지의 내부에는 Skyworks 사의 CLA4605 PIN 다이오드 칩을 장착하여 다이오드를 제작하였다.

3.1 CJ 및 CT 측정

제작된 다이오드의 CJ(Junction capacitance), CT(Total capacitance)와 패키지의 기생 커패시턴스 Cpkg를 측정하기 위하여 그림 5에 나타낸 것과 같이 프로브 스테이션과 Agilent 사의 반도체소자 분석기인 B1500A를 사용하여 측정 환경을 구성하였다. 커패시턴스 측정을 위해 DC 바이어스를 –100 mV부터 100 mV까지 인가하고 AC 주파수는 1 MHz를 인가하며 0 V에서의 커패시턴스를 측정하여 그 결과를 표 2에 나타내었다. 다이오드 칩만을 이용하여 CJ를 측정하였을 때 282.808 fF의 측정값을 얻을 수 있었으며, 패키지된 다이오드의 CT는 각각 358.633~410.087 fF으로 측정되었다. 패키지의 기생 성분 Cpkg는 CJ와 CT의 차이 값으로 구할 수 있으며, 75.825~127.259 fF로 나타나는 것을 알 수 있다. 시뮬레이션을 통해 얻은 결과와 같이 기판의 유전율이 큰 샘플 #1의 CT 및 Cpkg가 가장 큰 것을 확인하였으며, 구조는 같으나 기판의 유전율이 작은 샘플 #2의 커패시턴스가 두 번째로 큰 것을 확인하였다. 또한, 패키지의 패드 간 거리가 0.15 mm인 샘플 #1, 샘플 #2에 비해 0.3 mm의 패드간 거리를 갖는 샘플 #3에서 가장 작은 CT 및 Cpkg 값을 얻을 수 있었다. 따라서 같은 크기의 패키지에서는 유전율이 작고 패드와 패드 사이의 거리가 먼 패키지가 작은 CT 및 Cpkg 를 나타낸다는 것을 알 수 있다. 다만 시뮬레이션과 측정 결과에 대한 Cpkg 값의 차이는 본딩 와이어의 길이, 형태 등에 대한 정확한 정보가 반영되지 않았기 때문에 나타나는 결과로 해석된다.

3.2 RS 측정

그림 1을 통해 설명한 것과 같이 전력 제한기에 높은 전력이 입력되면 PIN 다이오드가 on 상태로 변하며, 직렬 저항 RS가 낮아지므로 입력된 신호를 반사하고 수신부로 전달되는 전력을 제한하게 된다.

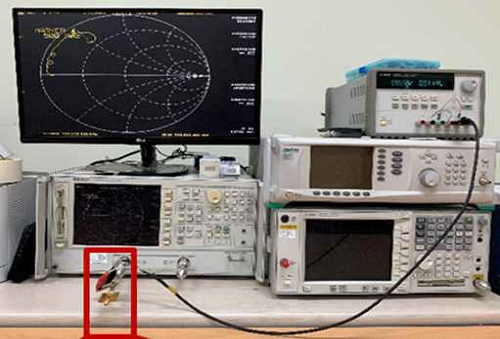

따라서 RS의 크기에 의해 반사되는 신호의 크기가 결정되게 된다. 패키지된 PIN 다이오드 종류에 따른 on 상태에서의 직렬 저항값 RS 차이를 측정하기 위하여 그림 6과 같이 측정 환경을 구성하였다. 네트워크 분석기로는 HP사의 8720D를 사용하여 500 MHz RF 신호를 인가하였으며, 동시에 PIN 다이오드를 on 상태로 만들기 위하여 DC 전원공급기와 바이어스 티(Bias tee)를 이용하여 DC 10 mA 전류를 인가하였다. RS 측정결과는 표 3에 나타내었다. 패키지에서 애노드 패드와 캐소드 패드의 거리에 따라 본딩 와이어의 길이가 달라지기 때문에 RS에 약간의 영향을 미치기는 하나, 3종류의 패키지에 의한 RS의 차이는 0.07 Ω 이내로 거의 동일하게 나타나는 것을 확인할 수 있었다.

3.3 삽입손실 측정

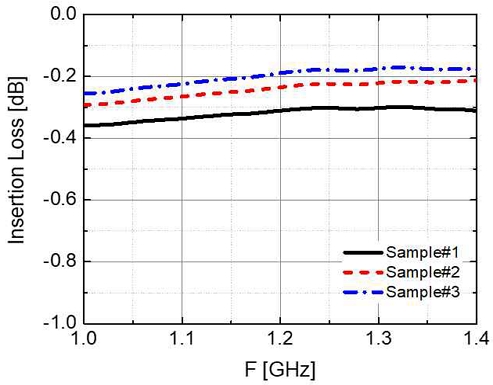

낮은 전력이 입력되는 정상적인 상황에서 전력 제한기의 가장 중요한 성능 지표 중 하나인 삽입손실은 PIN 다이오드 칩의 CJ와 패키지에서 발생하는 기생성분인 Cpkg가 합쳐진 CT에 의해 큰 영향을 받는다. 따라서 패키지 구조별로 변화하는 기생 성분에 의해 삽입손실을 네트워크 분석기를 이용하여 측정한 다음 비교 분석한 결과를 그림 7에 나타내었다. 1.0 ~ 1.4 GHz 범위에서 삽입손실을 측정하였을 때 중심주파수인 1.2 GHz에서 샘플 #1은 -0.31 dB, 샘플 #2는 –0.24 dB, 샘플 #3은 –0.19 dB의 삽입손실을 나타내었다. 측정 결과를 통하여 분석한 결과 동일한 PIN 다이오드 칩을 사용하여 패키지를 하였을 때, 기판의 유전율이 작고 패드의 간격이 가장 먼 샘플이 Cpkg가 가장 작으므로 삽입손실 또한 가장 낮게 나오는 것을 확인할 수 있었다. 따라서 일반적으로 삽입손실을 줄이기 위해서는 특히 Cpkg가 작은 패키지를 사용할 필요가 있다.

본 연구에서 사용된 각종 측정 조건들은 표 4에 정리하였다.

Ⅳ. 결 론

본 논문에서는 PIN 다이오드의 패키지 구조 및 재질에 따른 기생 성분의 차이와 PIN 다이오드로 전력 제한기를 구현하였을 때 동작 특성에 발생하는 차이에 대해 비교 분석한 결과를 기술하였다. Q3D Extractor를 이용하여 3종류의 패키지 구조 및 재질에 의해 발생하는 기생 성분을 시뮬레이션하였으며, 그 결과를 실제 측정값과 비교 분석하였다. 이를 통해 패키지를 구성하는 패드의 크기 및 위치, 본딩 와이어의 굵기 및 길이 등에 따라 기생 성분인 Lseries, Lpaddle, Cpkg가 달라지는 것을 확인하였다. 그중에서도 특히 Cpkg는 유전율을 결정하는 패키지의 재질이나, 애노드 패드와 캐소드 패드의 서로 마주 보는 면적과 거리에도 영향을 받는 것을 확인하였다. PIN 다이오드를 이용한 전력 제한기의 특성 중 중요한 삽입손실은 패키지의 기생 커패시턴스 Cpkg에 의해 영향을 받으며, 같은 크기의 패키지에서는 Cpkg가 작을수록 삽입 손실도 감소하는 것을 확인할 수 있었다. 따라서 삽입손실을 줄이기 위해서는 Cpkg가 작은 패키지를 사용할 필요가 있다.

Acknowledgments

본 연구는 민군기술협력사업(Civil-Military Technology Cooperation Program; No. 19CM5079)의 지원에 의한 것임

본 연구를 위하여 도움을 주신 IDEC와 (주)블루웨이브텔에 진심으로 감사드립니다.

References

- Microsemi-Watertown "The PIN Diode Circuit Designers’ Handbook", pp. 3-9, Oct. 2013.

-

P. Sum, L. Peng, P. Upadhyaya, D. H. Jeong, and D. Y. Heo, "Enhancement technique of insertion loss and linearity for PIN diode switches", Microwave and Optical Technology Letters, pp. 1430-1435, Vol. 53, No. 6, Jun. 2011.

[https://doi.org/10.1002/mop.26022]

- Skyworks, "Design with PIN Diodes", Application note, Aug. 2021.

-

J. Zhao, Q. Chen, Z. Chen, C. Chen, Z. Liu, and G. Zhao, "Impact of the structure on the thermal burnout effect induced by microwave pulses of PIN limiter diodes", Scientific Reports 3230, Feb. 2022.

[https://doi.org/10.1038/s41598-022-07326-w]

-

J.-S. An, "A study on implementation of high power tunable bandpass filter using PIN diode", Journal of KIIT, Vol. 11, No. 12, pp. 13-19, Dec. 2013.

[https://doi.org/10.14801/kiitr.2013.11.12.13]

-

K.-W. Yeom, P.-S. Im, D.-H. Lee, J.-S. Park, and B.-K. Kim, "Design of a s-band transfer-type SP4T using PIN diode", The Journal of Korean Institute of Electromagnetic Engineering and Science, Vol. 27, No. 9, pp. 834-843, Sep. 2016.

[https://doi.org/10.5515/KJKIEES.2016.27.9.834]

- S. J. Kim, S. J. Yun, and H. Y. Lee, "Reduction of the bondwire parasitic effect using dielectric materials for microwave device packaging", Proc. of the IEIE, Vol. 34, No. 2, pp. 55-63, Feb. 1997.

- S. J. Yun and H. Y. Lee, "Parasitic analysis of a grounded bondwire for low-cost plastic packaging of microwave devices", Proc. of the IEIE. Vol. 34, No. 2, pp. 75-80, Feb. 1997.

2018년 3월 ~ 현재 : 호서대학교 전자융합공학부(학석사 통합과정)

관심분야 : 전력분배/결합기, 초고주파 발진기, CDMA

2022년 2월 : 호서대학교 전자디스플레이공학부(공학사)

2022년 3월 ~ 현재 : 호서대학교 전자융합공학부 석사과정

관심분야 : 5G 안테나, RF 전력제한기, LED 조명시스템

1997년 2월 : 고려대 전파공학과(공학사)

1999년 2월 : 고려대 대학원 통신시스템공학과(공학석사)

2010년 8월 : 고려대 대학원 컴퓨터·전파통신공학과(공학박사)

1999년 3월 ~ 2015년 8월 : 한화탈레스(現 한화시스템) 통신연구소 수석연구원

2015년 9월 ~ 현재 : 호서대학교 전자융합공학부 부교수

관심분야 : RF/Microwave transceivers, Reconfigurable antenna systems, Wireless sensor systems, RF/Microwave components

1981년 2월 : 경북대학교 전자공학과(공학사)

1983년 2월 : 부산대학교 전자공학과(공학석사)

1992년 2월 : 부산대학교 전자공학과(공학박사)

1983년 3월 ~ 1997년 8월 : 한국전자통신연구원 반도체연구단 책임연구원

2004년 9월 ~ 2006년 8월 : University of Florida 연구교수

1997년 9월 ~ 현재 : 호서대학교 전자융합공학부 교수

관심분야 : RF 아날로그 ASIC 설계, 전력소자 설계 및 공정, LED 조명시스템, RF 전력제한기, 5G 안테나