문턱전압 폐곡선을 이용한 AC PDP에서 인가전압에 의한 기입방전 특성의 연구

초록

교류형 플라즈마 디스플레이에서의 기입 방전의 특성은 셀 내부에 형성된 벽전압과 인가전압의 합에 의해 결정된다. 만약 높은 벽전압 조건에서 인가전압을 상승시키면 셀 내부에서 방전이 발생되는 전체 전압보다 높아지므로 원하지 않는 셀에서도 오방전이 발생한다. 그러므로 셀 내부에서 발생되는 전체 전압의 크기는 동일해야 하므로 벽전압의 크기는 줄이고 인가전압의 크기를 증가시키는 방법을 제시하였다. 본 연구에서는 인가전압의 크기가 벽전압보다 낮을 때와 높을 때의 기입 방전 특성을 실험하였고 문턱전압 폐곡선을 이용하여 셀 내부의 인가전압과 벽전압을 측정하였다. 그 결과 외부인가전압이 벽전압보다 높을 때 기입 방전의 시간을 1.5에서 1.15 μs로 단축시킬 수 있었다.

Abstract

The characteristics of the write discharge in the AC plasma display panel are determined by the sum of the wall voltage and the applied voltage formed inside the cell. If the applied voltage is increased under the high wall voltage condition, since the voltage is higher than the total voltage at which the discharge is generated in the cell, the misfiring discharge occurs in the unwanted cell. Therefore, as the total voltage generated inside the cell should be the same, the method of reducing the wall voltage and increasing the applied voltage is proposed. In this study, the write discharge characteristics of the applied voltage when the applied voltage was lower than the wall voltage and high were measured. The applied and the wall voltages were measured using the threshold voltage closed curve. As a result, the write discharge time can be shortened from 1.5 to 1.15μs when the applied voltage is higher than the wall voltage.

Keywords:

wall voltage, applied voltage, write discharge, threshold voltage, AC PDPⅠ. 서 론

교류형 플라즈마 디스플레이 패널(AC PDP)의 구동방법에서 그레이 레벨은 TV 프레임 전체 시간동안 휘도가 다른 여러 개의 부-프레임을 만들어서 그것들의 조합에 의해 결정된다[1]. 그리고 각각의 부-프레임은 또한 초기화(Reset), 기입(Write), 유지(Sustain) 기간으로 나눠진다[2]. 그 중에서 기입 시간의 비중이 전체 시간동안에 차지하는 비율이 70 % 이상이 되기 때문에 AC PDP의 휘도를 높이는데 한계가 있다[3]. AC PDP의 패널에서는 세 개의 전극이 있는데 수평으로 두 종류의 전극이 교대로 있고, 수직으로 다른 전극이 셀마다 나열되어 있다. 화면에서 영상을 표현하기 위해서는 초기화 기간에서 셀 내부에서 벽전하를 쌓고, 기입기간 동안 두 전극에 전압이 인가되어 방전이 발생되고, 선택된 셀에서 유지 방전이 발생되어야 한다. 기입기간 동안 수직 방향으로 하나의 셀 당 하나의 펄스가 인가되고 해상도에 따라 수백 개의 펄스가 순차적으로 인가되므로 기입 시간이 길어질 수밖에 없다. 그러므로 만약 하나의 셀에 인가되는 각각의 시간을 단축시킬 수 있다면 수백 개의 펄스폭을 줄일 수 있으므로 전체시간이 획기적으로 줄어들 수 있다. 셀 내부에 발생되는 방전은 내부에서 생성된 벽전하와 외부에서 인가되는 전압의 합으로 결정된다.

기입 방전을 펄스폭 내에서 안정적으로 발생시키고 방전을 빠르게 발생시키기 위해서는 초기화 기간에 많은 벽전하를 쌓아서 셀 내부에 벽전압을 높여야 한다[4]. 한편, 초기화 기간에서 양의 전압을 높여서 많은 양의 벽전하를 쌓을 수 있지만, 초기화 전압이 낮아지면서 벽전하가 일부 소거되기 때문에 일정양의 벽전하만 쌓을 수 있다. 소거되는 벽전하의 양을 최소화 시키는 방법이 이전에 연구되었지만, 방전 전압마진이 줄어들기 때문에 그 한계가 있었다[5][6]. 반면에 기입기간에서 셀 외부에서 인가되는 전압을 상승시키면 선택된 셀뿐만 아니라 선택되지 않은 셀에서도 방전을 유발한다. 앞에서 설명하였듯이 셀 내부에서의 안정적인 방전 전압은 벽전하에 의해 형성된 벽전압과 셀 외부 전극에 인가된 전압에 의해 결정된다. 만약 벽전압이 높으면 인가전압은 낮아야하고, 반대로 벽전압이 낮으면 인가전압은 높아야 안정적인 기입 방전이 발생한다[7].

본 논문에서는 셀 내부의 전체 전압은 고정인 상태에서 인가전압에 비해 벽전압이 높은 경우와 벽전압에 비해 인가전압이 높은 경우에 대해 기입 방전특성을 실험하였고, 각각의 경우를 문턱전압 폐곡선(Vt closed curve)을 이용하여 셀 내부의 인가전압과 벽전압을 측정하였다[8][9]. 그 결과 벽전압이 높은 경우보다 외부 인가전압이 높은 경우에 방전지연시간을 단축시킬 수 있었다. 또한 인가전압이 높은 경우 벽전압은 낮아지기 때문에 초기화 기간에 많은 벽전하를 쌓을 필요가 없기 때문에 초기화 전압도 낮출 수 있고 각각의 경우에 대해 배경광도 측정하였다.

Ⅱ. 패널의 구조 및 구동파형

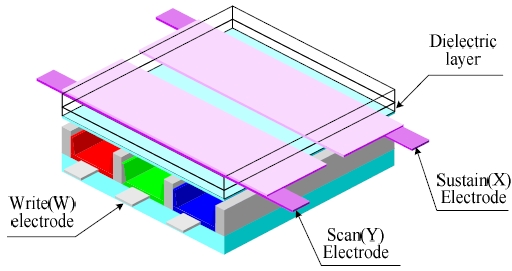

그림 1은 실험에 사용된 세 개의 RGB 셀을 가진 6인치 AC PDP에서 구조를 보이고 있다. 그림에서 각각 유지(X) 및 주사(Y) 전극으로 구성된 상판에는 두 개의 전극이 나란히 배열되어 있으며, 이 전극들은 버스(Bus) 전극이라고도 불린다. 그리고 각 버스 전극부터 셀 중앙까지는 투명 전극인 ITO(Indium Tin Oxide)가 넓게 도포되어있다. 버스 전극은 전류를 잘 흐르게 하지만 불투명하므로 셀 내에서 발생된 빛이 차단되지만, 투명한 ITO 전극은 셀 내에서 발생된 빛을 통과시킨다. 그러므로 셀 중앙에 위치시킬 수 있으며 상판에서 두 전극 사이에 방전이 쉽게 발생하도록 전극의 간격을 가깝게 설계할 수 있다.

상판에서 셀 내부에서 발생하는 방전에 직접 노출되는 부분인 유전체 층은 전극을 방전으로부터의 손상을 방지하는 역할을 한다. 하판에는 기입 전극(A)이 상판의 두 전극과 비교해서 수직 방향으로 배열되어 있으며 격벽이 각 색상마다 분리시킨다. 하판의 기입 전극 위에 빛의 삼원색인 빨강, 초록, 파랑색의 형광체가 도포되며 셀 내부의 방전 공간에는 일반적으로 Ne-Xe 혼합 가스가 사용된다.

표 1에서 본 실험에 사용된 패널의 사양을 나타낸다. 상판에서는 버스전극의 폭, ITO 전극의 폭, 두 ITO 전극 사이의 간격이 기록되었으며, 하판에는 기입 전극의 폭, 격벽의 높이, 격벽의 폭이 나타내었다. 패널 내부에서는 Ne(93%)-Xe(7%)의 함량을 갖는 혼합 가스가 사용되었다.

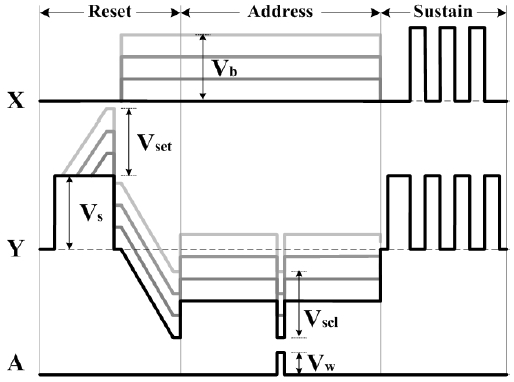

그림 2는 TV 프레임 시간 중에서 하나의 부 프레임 시간 동안에 AC PDP의 세 전극에 인가된 본 실험에 사용되는 구동 파형을 나타낸다.

AC PDP는 하나의 TV 프레임 시간 동안에 밝기가 다른 선택된 부-프레임의 조합으로 밝기의 레벨을 표시하고, 부-프레임은 각각 초기화, 기입, 유지 기간으로 구성된다. 초기화 기간에서는 높은 경사파 전압이 인가되어 셀 내부에 남아있는 벽전하들을 소거하고 다시 벽전하를 쌓아주는 역할을 한다. 초기화 기간에 쌓여진 벽전하에 의해 기입 방전이 낮은 전압으로도 발생시킬 수 있다. 그림 2의 기입 기간에서는 펄스 파형을 하나만 그렸지만, 실제로는 셀마다 순차적으로 펄스가 인가되므로 시간이 매우 많이 걸린다. 또한 각각의 펄스폭은 안정적인 방전이 보장되는 시간을 가져야한다. 만약 펄스폭을 줄인다면 방전이 약화되어 유지 기간에서도 방전이 발생하지 않기 때문에 쉽게 줄일 수 없으나 기입 방전이 빠르게 형성된다면 펄스폭의 시간을 줄일 수 있다. 유지 기간에서는 X와 Y전극에 교대로 인가된 사각파형에 의해 선택된 셀에서만 강한 방전이 발생되어 빛을 볼 수 있다.

표 2는 그림 2에서의 기준 및 실험 전압 레벨을 나타낸다. 실험 전압은 기준 전압과 비교하여 초기화 전압(Vset), 바이어스 전압(Vb), 주사전압 (Vscl)이 동시에 50V 간격으로 동시에 변화한다.

Ⅲ. 기입방전 특성

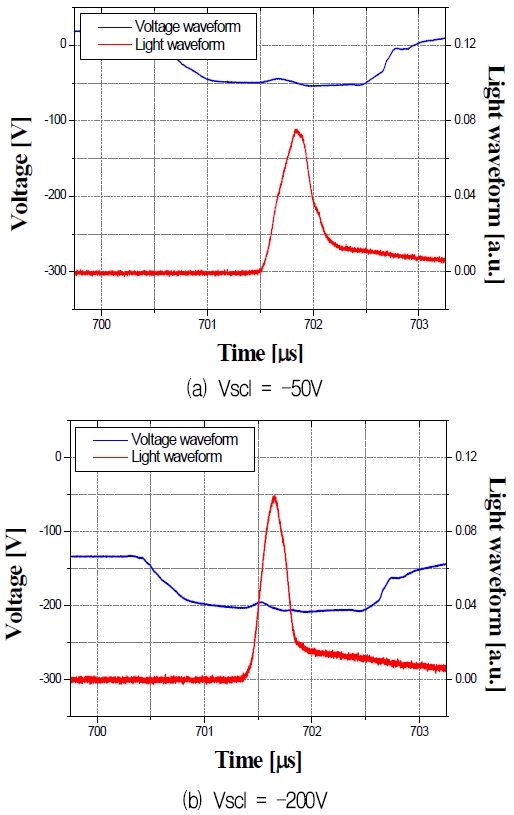

그림 3은 기입 기간에서 인가된 주사 전압과 그의 광파형의 변화를 나타낸다. 그림 3(a)에서 기준 전압 즉, 기입 기간에서 인가된 주사 전압이 -50V, 초기화 전압이 150V, 바이어스 전압이 150V의 주사 전압과 광 파형을 보이고 있다. 그림 3(b)는 실험에 사용된 조건 중에서 가장 변화가 큰 조건 즉, 인가된 주사 전압이 -200V, 초기화 전압 및 바이어스 전압이 0V 일 때 측정된 주사 전압과 광 파형을 보이고 있다. 측정된 시간은 기입기간 중에서 중간 부분이다.

그림 3의 (a)와 (b)를 비교해볼 때, 인가전압이 -200V일 때의 광파형이 기준 전압이 인가될 때보다 더 빠르고 높게 형성됨을 알 수 있었다. 그러므로 단축된 시간만큼 하나의 기입 펄스폭을 줄일 수 있기 때문에 기입 기간 동안 수백 개의 펄스폭을 동시에 줄일 수 있다. -100V와 -150V의 주사파형과 광파형의 그림은 여기서 생략되었지만 광파형의 변화 경향은 동일하였다.

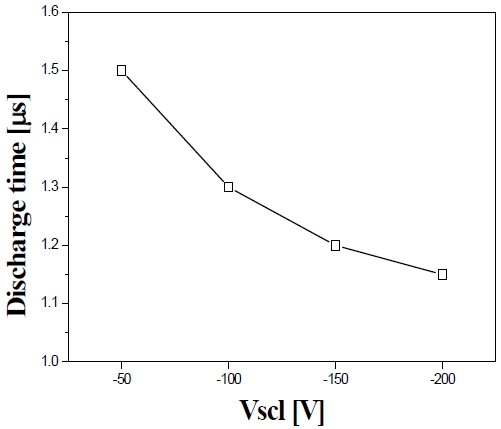

주사 전압의 변화에 의한 기입 방전의 지연시간을 측정한 것은 그림 4에서 나타내었다. 주사 전압이 낮아질수록 기입 방전의 지연시간은 -50V에서 1.5μs였으나 -200V에서 1.15μs으로 단축되었음을 확인할 수 있다. 일반적으로 HD급 해상도를 갖는 AC PDP는 세로방향으로 768개의 셀을 가지게 되므로 한 부프레임에서 기입동작에 걸리는 시간은 768×1.5μs=1152μs이고, 프레임이 8개의 부프레임으로 구성되었다고 가정하면 기입 시간은 16.7ms 중에서 약 9.2ms의 시간으로 약 55%를 차지하였다. 그러나 -200V일 경우 7ms 정도의 시간을 차지하므로 약 41%로 줄일 수 있었다.

한편, 그림 2에서 보듯이 세 개의 전압이 동시에 변화되기 때문에 셀 내부에서의 벽전압 및 외부 인가전압의 합인 전체 전압은 같을 것이다. 만약 셀 내부의 전체 전압이 동일하다면 기입 방전의 지연시간은 이론적으로는 동일해야 한다. 그런데 그림 4에서의 결과에서 볼 때 기준 전압인 –50V보다 -200V일 때 기입 방전의 지연시간이 단축되었다. 주사 전압이 -50V인 경우에는 초기화 기간에 많은 벽전하가 쌓여서 기입 기간에 많은 벽전하가 남아 있기 때문에 낮은 주사 전압으로도 방전이 발생할 수 있었다. 반면에 주사전압이 -200V인 경우에는 초기화 기간의 낮은 전압에 의해 벽전하를 쌓지 않기 때문에 벽전압보다는 주사 전압이 기입 방전에 더 큰 영향을 준다. 그러므로 셀 내부에서 기입 방전의 특성향상에 벽전압보다는 외부 인가전압이 더 큰 영향을 준다고 확인된다.

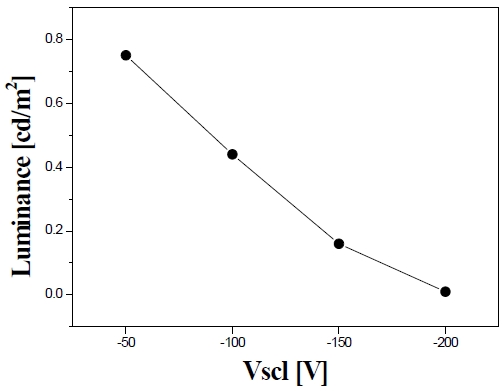

그림 5는 주사 전압의 변화에 의한 배경 휘도를 측정한 것이다. 주사 전압이 더 낮아질수록 그림 2에서의 다른 초기화 파형과 바이어스 파형의 전압도 같이 낮아지기 때문에 초기화 기간의 방전의 세기는 낮아질 수밖에 없고 휘도도 낮아질 것이다. 주사전압이 -200V인 경우에는 초기화 전압이 없기 때문에 초기화 방전이 발생되지 않으며 벽전하도 생성되지 않는다.

Ⅳ. 벽전압과 인가전압의 영향

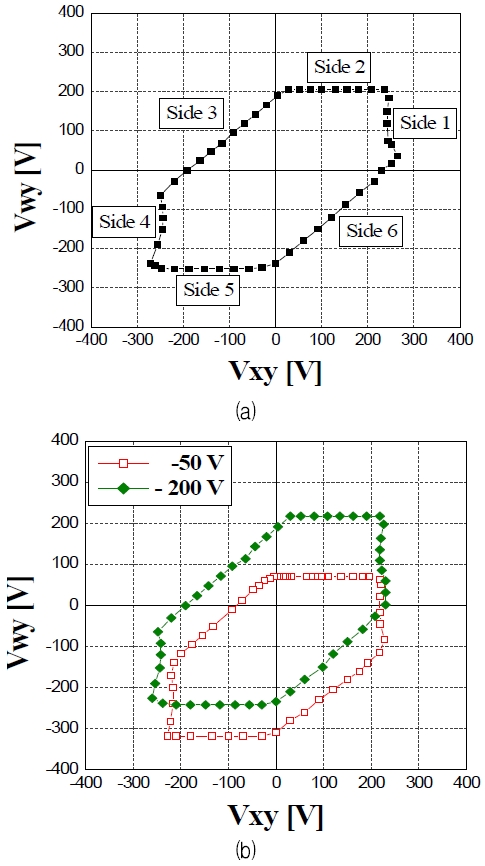

주사 전압의 변화에 따른 벽전압과 인가전압의 크기를 비교하기 위하여 문턱전압 폐곡선이 사용되었다. 그림 6(a)에서 보여지듯이 문턱 전압 폐곡선은 세 전극 사이의 방전이 발생하기 시작하는 전압을 2차원으로 측정한 곡선이다. 수평축은 X와 Y 전극 사이의 전압이고 수직축은 W와 Y 전극 사이의 방전개시 전압을 의미한다. 즉, side 1은 W 전극의 전압이 변화할 때마다 X와 Y 전극 사이의 방전개시 전압을 측정한 것이고, side 2는 X 전극의 전압이 변화할 때마다 W와 Y 전극 사이의 방전개시 전압을 측정한 값들이다. 측정된 값들을 모두 다 모으면 그림 6(a)처럼 육각형 모양이 된다. 그러므로 그림 6(a)에서 육각형 모양의 선의 내부 영역은 방전이 발생되지 않는 세 전극의 전압의 상태를 가리키고, 외부는 방전이 발생되는 전압의 상태를 의미한다. 그림 6(a)에서의 문턱전압 폐곡선은 셀 내부에 벽전압이 없는 경우에 방전 개시 전압을 측정한 것이며 그림 6(b)는 주사 전압이 각각 –50V와 -200V일 때 초기화 기간이후에 측정된 문턱전압 폐곡선이다.

Measured of threshold voltage closed curves when no wall charge in cell (a) and scan voltage is changed

그림 6(a)에서 벽전하가 없는 경우의 문턱전압 폐곡선과 비교해보면 –50V일 경우의 문턱전압 폐곡선이 많이 변한 것은 셀 내부에 벽전하가 많이 쌓였다는 것을 의미한다. 반면에, -200V일 경우의 문턱전압 폐곡선이 그림 6(a)와 큰 차이가 없다는 것은 셀 내부의 벽전하의 양이 아주 적다는 것을 의미한다. 다시 말하면, -200V일 경우에는 벽전압은 거의 없으며 외부 인가전압 만에 의해 방전이 발생했음이 확인된다. 그러므로 -200V의 경우 벽전하보다는 외부 인가전압에 의해 방전이 발생하므로 방전에 더 빠르게 발생하는 효과가 있으나 –200V까지 사용할 수 있는 구동회로의 부품이 사용되어야 하므로 제조단가가 상승할 수 있다.

표 3에서는 그림 6(a)와 (b)의 결과를 비교하여 벽전압과 인가전압의 크기를 계산하였다. 벽전압은 문턱전압 폐곡선의 차이를 측정한 값이고, 인가전압은 W와 Y 전극 사이의 실제 전압차를 나타낸다. 표 3에서 주사전압이 –50V와 -200V일 때 벽전압과 인가전압의 차이는 발생하지만 전체전압은 거의 같음을 볼 수 있다. 이것은 동일한 셀 내부의 전체전압에서 주사전압의 변화에 의한 외부 인가전압이 벽전압보다 클수록 방전 지연시간은 단축시킬 수 있음을 알 수 있다. 그 이유는 벽전압은 각 전극에 붙어있는 벽전하를 공간전하로 변화시키는데 시간과 손실이 발생하지만 외부 인가전압은 곧바로 셀의 전위에 영향을 주기 때문이라고 생각된다.

Ⅴ. 결 론

교류형 플라즈마 디스플레이 패널에서 초기화 기간에서 형성된 벽전압과 기입기간에 인가되는 전압에 따른 기입 방전 특성의 변화를 측정하기 위하여 초기화 및 기입 기간에 인가되는 전압의 크기를 변화시켰다. 주사 전압을 기준 레벨보다 음의 방향으로 낮출수록 벽전압은 적어지고 외부 인가전압은 증가하였기 때문에 기입 방전특성이 향상되었다. 기입 방전에 크게 기여하는 W와 Y 전극 사이의 벽전압을 알기 위하여 문턱전압 폐곡선이 측정되었으며, W와 Y 전극사이에서의 벽전압과 인가전압의 합인 전체 전압은 비슷한 것으로 계산되었다. 그러므로 기입 방전특성에 큰 영향을 주는 것은 벽전압이 아니라 외부 인가전압임이 알 수 있었다. 그 결과, 하나의 펄스폭에서 기입 방전의 시간은 1.5에서 1.15 ms로 크게 단축시킬 수 있었다.

References

- S. Kanagu, Y. Kanazawa, T. Shinoda, K. Yoshikawa, and T. Nanto, "A 31-in.-Diagonal Full-Color Surface-Discharge ac Plasma Display Panel", Society for Information Display, pp. 713-716, May 1992.

- S. Mikoshiba, "Color Plasma Displays", Society for Information Display Seminar Lecture Note, Vol. I, M-2, May 2000.

-

M. Ishii, K. Igarashi, S. Mikoshiba, H. Asai, and S. Sago, "Reduction of Data Pulse Voltage to 20V by Using Address-while-Display Scheme for AC PDP", SID Symposium Digest of Technical Papers, Vol. 30, No. 1, pp. 162-166, May 1999.

[https://doi.org/10.1889/1.1833985]

-

K. Sakita, K. Takayama, K. Awamoto, and Y. Hashimoto, "Analysis of a Weak Discharge of Ramp-Wave Driving to Control Wall Voltage and Luminance in AC PDPs", SID Symposium Digest of Technical Papers, Vol. 31, No. 1, pp. 110-113, May 2000.

[https://doi.org/10.1889/1.1832859]

-

J. Y. Kim, Y. T. Jeong, and B. G. Cho, "Study on Address Discharge Characteristics by Changing Ramp-down Voltage in AC PDPs", IEICE Transactions on Electronics, Vol. 94, No. 9, pp. 1483-1485, Sep. 2011.

[https://doi.org/10.1587/transele.E94.C.1483]

-

J. Y. Kim, Y. T. Jeong, and B. G. Cho, "Study on High Speed Address Driving Method Using Two-Step Address Pulses in AC Plasma Display Panel", Molecular Crystals and Liquid Crystals, Vol. 651, No. 1, pp. 196-202, Oct. 2017.

[https://doi.org/10.1080/15421406.2017.1338085]

-

B. G. Cho and H. S. Tae, "High-speed driving waveform based on reset and address discharge analysis using Vt closed curve in ACPDPs", Journal of the Society for Information Display, Vol. 16, No. 1, pp. 47-53, Jan. 2008.

[https://doi.org/10.1889/1.2835034]

-

H. J. Kim, J. H. Jeong, K. D. Kang, J. H. Seo, I. H. Son, K. W. Whang, and C. B. Park, "Voltage Domain Anyaysis and Wall Voltage Measurement for Surface-Discharge Type AC PDP", SID Symposium Digest of Technical Papers, Vol. 32. No. 1, pp. 1024-1029, Jun. 2001.

[https://doi.org/10.1889/1.1831732]

- K. Sakita, K. Takayama, K. Awamoto, and Y. Hashimoto, "Analysis of Cell Operation at Address Period Using Wall Voltage Transfer Function in Three-electrode Surface-Discharge AC PDPs", International Display Workshops, pp. 841-844, Dec. 2001.

1979년 2월 : 경북대학교 전자계산전공(공학사)

1984년 2월 : 일본 니혼대학교 전자공학과(공학석사)

1992년 2월 : 일본 도호쿠대학교 정보공학과(공학박사)

1986년 ~ 현재 : 부경대학교 컴퓨터공학과 교수

관심분야 : 컴퓨터네트워크, 네트워크관리, IPv6, IPTV, 컴퓨터시스템

2001년 2월 : 경북대학교 전자전기공학부(공학사)

2003년 2월 : 경북대학교 전자공학과(공학석사)

2006년 8월 : 경북대학교 전자공학과(공학박사)

2008년 3월 ~ 현재 : 부경대학교 융합디스플레이공학과 교수

관심분야 : 디스플레이 시스템, 고전압 회로, 영상정보시스템