GHz-대역 저잡음 증폭기의 선형성 향상에 관한 연구

초록

본 논문은 GHz 대역 저잡음 증폭기의 선형성 향상에 관한 연구 결과를 제안한다. 선형성 향상을 증명하기 위해 제안하는 회로는 TSMC 0.13-µm 혼성신호/고주파 BiCMOS SiGe 공정(fT/fMAX=120/140GHz)으로 제작하였다. 또한, 제작한 증폭기는 1.2볼트 전원전압에서 동작하며, 2.4GHz의 동작주파수에 동작하도록 구현되어 있다. 높은 선형성을 확보하기 위해 MBDS 기법을 이용하였다. 선형성 향상에 영향을 미치는 2차 비선형 트랜스컨덕턴스 계수를 감소시키기 위해 바이폴라 트랜지스터의 에미터에 병렬로 LC 탱크 회로를 연결하였다. 또한, 바이폴라 및 MOS 트랜지스터의 3차 비선형 계수의 위상을 조절하기 위해 베이스-콜렉터와 게이트-드레인에 각각 두 개의 귀환 커패시턴스를 연결하였다. 제안하는 저잡음 증폭기는 최근 발표된 연구결과와 비교해볼 때 27.6dBm의 가장 우수한 IIP3 특성을 보였다.

Abstract

This paper presents study results for linearity improvement of GHz-band low noise amplifier(LNA). To verify this linearity improvement, we fabricated the proposed circuit using TSMC 0.13-µm mixed signal/RF BiCMOS SiGe process(fT/fMAX=120/140GHz). The fabricated amplifier also operates at the power supply of 1.2V, and it is implemented to operate at the frequency of 2.4GHz. We used the MOS-BJT derivative superposition(MBDS) technique to achieve high linearity. To reduce the second-order nonlinear transconductance coefficient related to the enhancement of linearity, the LC tank circuit is paralleled in the emitter of bipolar transistor. We also connected two feedback capacitances in the base-to-collector and gate-to-drain capacitances to adjust the phase of third-order nonlinear coefficients of bipolar and MOS transistors, respectively. The proposed LNA showed excellent IIP3 of 26.7dBm compared to recently published results.

Keywords:

GHz-band, low noise amplifier(LNA), linearity, MOS-BJT derivative superposition(MBDS)Ⅰ. 서 론

최근 CMOS 공정의 급속한 발전으로 인해 소자의 소형화가 가능하게 되었다. 특히 고주파 집적회로는 개선된 고주파 특성으로 단일칩화와 저 가격이 요구되는 LTE, 지그비, 블루투스, 5G 시스템, 차량용 레이더, 무선랜 등의 시스템에 다양하게 적용되고 있다[1]-[7]. 그러나 RF CMOS 트랜지스터는 낮은 항복전압과 높은 문턱전압으로 인해 큰 동적 범위(DR, Dynamic Range)와 큰 전압 스윙을 갖는 저잡음 증폭기나 전력 증폭기의 적용에는 몇 가지 해결해야 할 문제점을 갖고 있다[4]-[10]. 특히 불규칙 포락(Non-constant envelope) 특성을 갖는 QPSK와 GFSK 등과 같은 변조방식을 사용하는 시스템의 저잡음 증폭기는 높은 선형성(linearity)이 요구된다. 선형성은 고주파 회로 설계에서 가장 중요한 지표 중의 하나이다.

선형성 향상시키기 위한 연구가 활발히 진행되고 있다[1]-[10]. 이러한 증폭기의 선형성을 개선시키기 위해 사용되는 방법으로는 feed-forward, 귀환(Feedback), 선 왜곡(Pre-distortion), DS(Derivative Superposition) 등이 연구되고 있으나 회로의 크기와 추가적인 직류 전력 소모로 인하여 단일칩 BiCMOS 저잡음 증폭기의 적용에는 다양한 어려움을 갖고 있다.

본 논문에서는 MBDS(MOS-BJT DS) 기법을 이용하여 GHz 대역의 저잡음 증폭기에 대해 선형성을 개선하고자 한다. 선형성 향상을 증명하기 위해 TSMC 0.13µm 혼성신호/고주파 BiCMOS 공정으로 2.4GHz 저잡음 증폭기를 제작하고자 한다. 선형성을 향상시키기 위해 2차 비선형 트랜스컨덕턴스 계수를 감소시키는 방법과 3차 비선형 계수의 위상을 조절하는 방법을 연구하고자 한다.

Ⅱ. 선형성 및 회로 설계

2.1 선형성 개요

이득 억압(Gain compression)은 저잡음 증폭기의 전력 취급 능력을 나타내는 특성으로 증폭기 입력 신호가 포화점에 도달하면, 이득이 점차 떨어지는 비선형적 현상(낮은 입력 전력 레벨에서는 출력 전력이 선형적으로 비례하나, 높은 입력 전력 레벨에서는 전력 이득이 선형적이지 못한 현상)을 말한다[11][12].

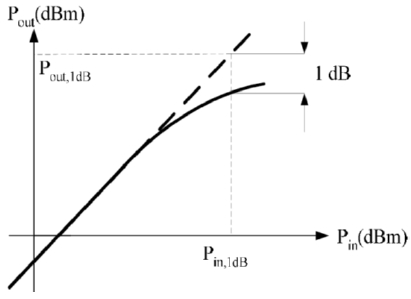

그림 1은 이러한 현상과 함께 1dB 억압점(P1dB, 1dB gain compression point)을 나타낸 것이다. 1dB 억압점은 식 (1)과 같이 소신호 증폭기의 선형적인 전력 이득 특성과 1dB 차이가 나는 점으로 정의하며, 낮은 신호 전력에서는 출력 전력은 입력 전력에 선형적으로 비례하나, 어떤 포화 임계점을 지나면 전력 이득이 감소하고 포화에 이르게 된다[11][12].

| (1) |

여기서 G0는 선형 소신호 이득을 말한다.

1dB 억압점과 관련하여 또 다른 중요한 변수로서 동적 범위는 일반적으로 수신기에서 신호 왜곡없이 깨끗하게 검파할 수 있는 입력신호 전력레벨의 범위로 정의할 수 있다[11][12]. 증폭기의 동적 범위는 는 P1dB와 증폭된 신호의 검파 가능한 최소레벨과의 비율로 정의된다[11][12]. 만약 입력신호 레벨이 noise floor보다 XdB 높은 경우, 검파 가능한 동적 범위는 식 (2)와 같이 표현할 수 있다.

| (2) |

여기서 T=300K라고 가정하고, B는 신호 대역폭, NF는 잡음지수(Noise figure), G는 소신호 이득을 말한다.

저잡음 증폭기의 입력 신호는 나노 전압(nV) 또는 마이크로 전압(μV) 범위를 가지기 때문에 주변의 강한 왜곡(Distortions)이 존재할 경우 선형성을 유지하기 위해 큰 동적 범위를 가져야 한다[2]. 초고주파에서 수신기 체인(Chain)에 있는 증폭기는 수신기 누설(Leakage) 또는 블로커(Blocker)에 의한 많은 수의 밴드 내 간섭(Interferences)과 상호 변조(Inter- modulation)/교차 변조(Cross-modulation) 등과 같은 다양한 영향을 최소화하거나 제거할 수 있어야 한다[2][11][12].

2.2 귀환 커패시턴스에 의한 위상 제어 회로

고주파 블록을 구성하는 트랜지스터가 비선형 동작을 하는 주요 원인은 비선형 전압-전류 관계 때문이며, 공정이 향상될수록 비선형 특성이 뚜렷하게 발생한다[2]-[5]. 트랜지스터의 전압-전류 관계는 식 (3)과 표현할 수 있다.

| (3) |

여기서 gmi (i = 1, 2, 3)는 i차 비선형 계수(트랜스 컨덕턴스)를 말한다.

저잡음 증폭기에서 gm3는 비선형 특성을 초래하는 주요 계수이며, 그 항을 제거함으로써 선형성을 향상시킬 수 있다. 바이폴라 트랜지스터에 대한 Taylor expansion series 표현은 식 (4) 및 (5)로 근사화할 수 있다.

| (4) |

| (5) |

여기서 VBEQ는 베이스-에미터 바이어스 전압, IS0는 포화전류, ϕt는 열(Thermal) 전압을 나타낸다.

또한, 식 (4)에서 3차 계수는 식 (6)과 같이 표현할 수 있다.

| (6) |

식 (6)에 따르면 α3은 컬렉터 전류와 베이스-에미터 전압 간의 지수함수적인 관계로 인해 양의 값을 가진다. 음의 3차 계수를 가진 MOS 트랜지스터에 대해 전압-전류 관계는 식 (7)~(10)으로 표현이 가능하다.

| (7) |

| (8) |

| (9) |

| (10) |

여기서 는 전자 또는 정공 이동도, Cox는 단위 면적당 게이트 커패시턴스, θ는 수직 장 이동도 축퇴(Degeneration) 계수, Veff = Vgs0 - Vth 및 Vgs0는 게이트-소스 직류 바이어스 전압을 말한다.

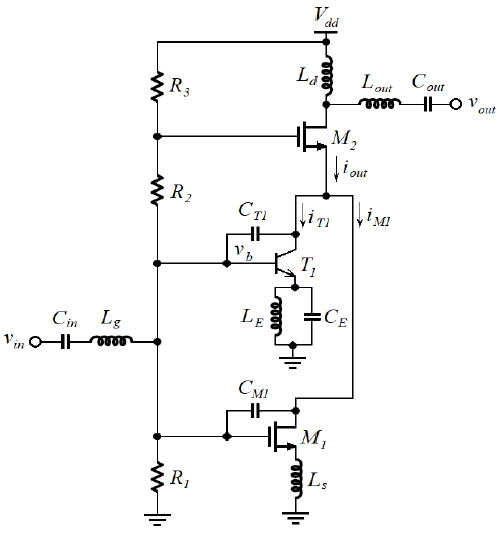

그림 2는 본 연구에서 제안하는 MBDS(MOS-BJT Derivative Superposition) 기법을 이용한 선형성이 개선된 회로를 나타낸 것이다. 그림 2로부터 알 수 있듯이 출력 전류 iout은 식 (11)과 같이 표현할 수 있다.

| (11) |

식 (6) 및 (10)으로부터 알 수 있듯이 α3와 β3는 서로 다른 부호를 가진다. 식 (11)에서 3차 항 gm3를 제거하기 위해 α3와 β3의 크기는 같아야 하지만, 일반적으로 α3는 β3보다 큰 값을 가진다[2]-[5]. 따라서 선형성을 향상시키기 위해 3차 항 gm3가 최소가 되도록 α3와 β3의 위상 조절이 필요하다. 또한, 식 (11)에서 gm3의 크기 및 위상은 바이어스 전압과 트랜지스터 크기(W/L)에 영향을 받기 때문에 일 위한 세심한 설계조건이 필요하다.

바이폴라 트랜지스터는 베이스 접합 부분에서 큰 2차 고주파 항(Harmonic term)을 초래하는 높은 비선형 커패시턴스를 가진다[5]. 베이스 커패시턴스의 감소현상을 극복하기 위해 그림 2와 같이 병렬로 연결된 LC 탱크회로(LE, CE)를 사용하였다. 인덕터 LE는 저전력에 영향을 미치는 기본 톤을 축퇴시키고, 선택도(Quality factor) Q에 영향을 미치기 때문에 충분히 적은 값을 선택하였다[5]. LC 탱크회로는 공진주파수에서 저항 성분만 남게 되는데, 이러한 저항 성분을 이용하여 α3의 값을 최적화하였다.

또한 IIP3(3rd-order Input Intercept Point)에 대한 gm2의 효과를 제거하기 위해 바이폴라 트랜지스터의 에미터에 연결하였다.

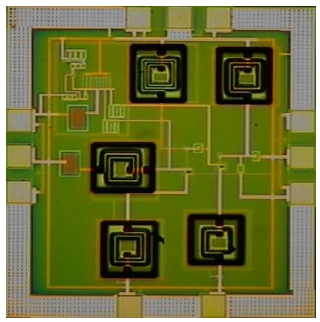

그림 3은 본 연구에서 제안하는 2.4GHz 저잡음증폭기의 칩 사진을 나타낸 것이다. 이러한 회로는 TSMC 0.13-µm 혼성신호/고주파 BiCMOS SiGe 공정(fT/fMAX=120/140GHz)으로 제작하였다. 패드를 포함한 물리적인 다이(Die) 면적은 대략 1.1m2×1.1m2였다.

높은 출력전력에서 T1의 비선형 베이스-에미터 커패시턴스(CBE)는 α3와 β3의 위상을 변화시킨다. 선형성은 이러한 위상 변화에 의해 감소된다. 따라서 병렬로 귀환 커패시턴스를 연결함으로써 α3와 β3의 위상 조절이 가능하다. T1의 베이스에 비선형 커패시턴스가 존재하기 때문에 T1의 베이스 전압 Vb, 전류 iT1과 iM1, 출력전압 vout 및 AIIP3는 식 (12)~(16)으로 표현할 수 있다.

| (12) |

| (13) |

| (14) |

| (15) |

| (16) |

여기서 ZL은 출력단의 임피던스를 나타낸다.

식 (16)으로부터 알 수 있듯이 α3와 β3의 위상차는 병렬로 귀환 커패시턴스를 연결함으로써 보상할 수 있으며, 3차 상호 변조 성분의 제거가 가능하다. 또한, gm3의 위상을 조절하기 위해 게이트-드레인 커패시턴스(CM1)와 베이스-콜렉터 커패시턴스(CT1)를 사용하였고, 이를 통해 저잡음 증폭기의 IIP3가 개선됨을 확인할 수 있다.

Ⅲ. 결과 및 분석

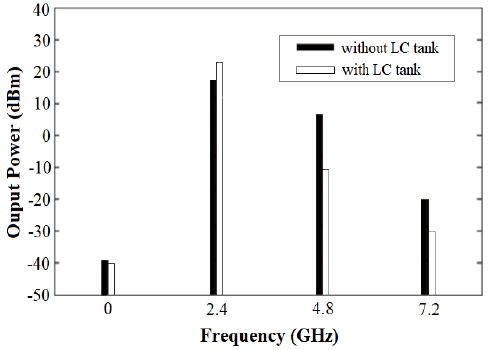

그림 4는 그림 2의 회로에서 T1의 에미터 단에 병렬로 LC 탱크회로를 연결한 경우와 연결하지 않은 경우에 대한 출력 전력 특성을 비교한 것이다. 앞에서도 언급했듯이 바이폴라 트랜지스터는 베이스 접합 부분에서 큰 2차 고주파 항을 초래하는 높은 비선형 커패시턴스를 가지기 때문에 베이스 커패시턴스의 감소현상을 보상하기 위해 병렬로 LC 탱크회로를 연결하였다. 그림 4로부터 알 수 있듯이 2.4GHz의 동작주파수에서 LC 탱크회로를 연결한 경우가 가장 높은 출력 전력을 보였고, 그 이외의 주파수대에서는 전력이 감소함을 알 수 있다. 이러한 효과는 IIP3의 개선에 영향을 준다.

표 1은 2.4GHz의 동작주파수에서 LE와 CE 값에 따른 IIP3 특성 변화를 나타낸 것이다. IIP3에 대한 gm2의 효과를 제거하기 위해 바이폴라 트랜지스터의 에미터단에 연결하였다. 표 1로부터 알 수 있듯이 LC 탱크회로에 사용한 LE와 CE의 값에 따라 IIP3가 개선됨을 확인할 수 있다.

표 2는 2.4GHz의 동작주파수에서 CT1 및 CM1 값에 따른 IIP3 특성 변화를 나타낸 것이다. 본 연구에서 선형성 향상을 위해 제안하는 MBDS 기법은 식 (13)~(16)으로부터 알 수 있듯이 gm3의 위상을 조절한다. 이를 위해 CM1과 CT1을 사용하였고, 0.53pF의 CM1과 0.11pF의 CT1에 대해 26.7dBm의 가장 우수한 IIP3를 보였다.

표 3은 본 연구에서 제안하는 저잡음 증폭기에 사용한 부품 값을 요약한 것이다. 앞에서 언급했듯이 선형성은 위상 천이에 따라 감소될 수 있다. 식 (6)~(16), 그림 4 및 표 1~2로부터 알 수 있듯이 각 부품의 값은 IIP3에 큰 영향을 준다.

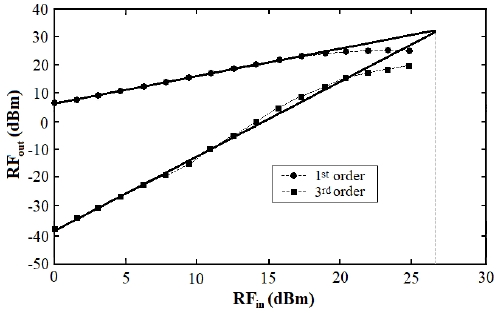

그림 5는 입력전력(RFin)에 따른 출력전력(RFout) 특성을 나타낸 것이다. 100MHz의 간격으로 2.4GHz의 동작주파수에서 투 톤(Two-tone) 성능 평가를 수행하였다. 그림 5로부터 알 수 있듯이 MBDS 기법과 식 (16)을 이용하여 제안한 저잡음 증폭기는 26.7dBm의 가장 우수한 IIP3 값을 보였다.

표 4는 최근 발표된 연구 결과와 본 연구 결과를 비교한 것이다. 높은 선형성을 확보하기 위해 T1은 활성영역에 바이어스 되도록, M1은 강한 반전 영역에서 바이어스 되도록 각각 설계하였다. MBDS 기법 및 식 (6)~(16)을 이용하여 3차 출력전류의 크기 및 위상을 조절하였고, α3와 β3의 크기는 같고 위상이 반대가 되어 서로 상쇄되도록 설계하였다. 표 4로부터 알 수 있듯이 본 연구에서 제안하는 저잡음 증폭기는 최근 발표된 기존 연구 결과[2][5][9][10]에 비해 26.7dBm의 가장 우수한 IIP3 특성을 보였다.

Ⅳ. 결 론

본 논문에서는 GHz 대역 저잡음 증폭기의 선형성 향상에 관한 연구 결과를 제안하였다. 선형성 향상을 증명하기 위해 TSMC 0.13µm BiCMOS SiGe 공정을 이용하여 2.4GHz의 동작주파수에 동작하는 저잡음 증폭기를 제작하였다. MBDS 기법을 이용하여 3차 비선형 계수의 위상을 조절하고 2차 비선형 트랜스컨덕턴스 계수를 감소시켜 선형성을 향상시켰다. 제안하는 저잡음 증폭기는 최근 발표된 연구결과와 비교해볼 때 27.6dBm의 가장 우수한 IIP3 특성을 보였다. 향후 MBDS 기법을 이용하여 GHz 대역 전력 증폭기와 믹서의 선형성 향상에 관한 연구를 수행할 계획이다.

Acknowledgments

이 논문은 안동대학교 기본연구 지원사업에 의하여 연구되었음

References

-

S. H. Noh and J. Y. Ryu, "Design of 24GHz CMOS Mixer for Automotive Collision Avoidance Radar", Journal of Korean Institute of Information Technology, Vol. 12, No. 11, pp. 31-37, Nov. 2014.

[https://doi.org/10.14801/kitr.2014.12.11.31]

- S. H. Noh and J. Y. Ryu, "Linearity Enhancement Technique for GHz-Band LNA", International Journal of Applied Engineering Research, Vol. 12, No. 19, pp. 9116-9119, Oct. 2017.

-

H. Rastegar and J. Y. Ryu, "An Integrated High Linearity CMOS Receiver Frontend for 24-GHz Applications", Journal of Semiconductor Technology and Science, Vol. 16, No. 5, pp. 595-604, Oct. 2016.

[https://doi.org/10.5573/JSTS.2016.16.5.595]

-

H. Rastegar and J. Y. Ryu, "A broadband Low Noise Amplifier with built-in linearizer in 0.13-μm CMOS process", Microelectronics Journal, Vol. 46, No. 8, pp. 698-705, Aug. 2015.

[https://doi.org/10.1016/j.mejo.2015.05.006]

- H. Rastegar, J. H. Lim, and J. Y. Ryu, "A 2GHz 20dBm IIP3 Low-Power CMOS LNA with Modified DS Linearization Technique", Journal of Semiconductor Technology and Science, Vol. 16, No. 4, pp. 443-450, Aug. 2016.

-

S. H. Noh and J. Y. Ryu, "Design of 24GHz Low Noise Amplifier for Short Range Radar of Automotive Collision Avoidance", Journal of Korean Institute of Information Technology, Vol. 11, No. 10, pp. 23-28, Oct. 2013.

[https://doi.org/10.14801/kiitr.2013.11.10.23]

- S. W. Kim and J. Y. Ryu, "Design of 24GHz Low Noise Amplifier for Automotive Radar", Journal of Korean Institute of Information Technology, Vol. 10, No. 7, pp. 41-47, Jul. 2012.

-

N. Nojima and T. Konno, "Cuber Predistortion Linearizer for Relay Equipment in 800 MHz Band Land Mobile Telephone System", IEEE Transactions on Vehicular Technology, Vol. VT-34, No. 4, pp. 169177, Nov. 1985.

[https://doi.org/10.1109/T-VT.1985.24057]

- C. Xin and S. Sinencio, "A linearization technique for RF low noise amplifier", ISCAS, Vol. 4, pp. 31-40, May 2004.

-

H. Rastegar and A. Hakimi, "A High Linearity CMOS Low Noise Amplifier for 3.66 GHz Applications using Current-Reused Topology", Microelectronics Journal, Vol. 44, No. 4, pp. 301-306, Apr. 2013.

[https://doi.org/10.1016/j.mejo.2013.01.013]

- B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, New York, NY, USA, 2001.

- B. Razavi, "RF Microelectronics", Prentice-Hall, Inc., New Jersey, pp. 11-98, 1998.

1982년 : 한양대학교 전자공학과(공학사)

1990년 : 일본 동경공업대학교 물리정보공학 졸업(공학석사)

1993년 : 일본 사이다마대학교 생산정보공학 졸업(공학박사)

1993년 ~ 1998년 2월 : 한국전자통신연구소 위성방송시스템연구실 선임연구원

1998년 3월 ~ 현재 : 안동대학교 전자공학과 교수

관심분야 : 디지털방송시스템, DSP, 반도체회로설계 및 검사

1993년 2월 : 부경대학교 전자공학과(공학사)

1997년 2월 : 부경대학교 전자공학과(공학석사)

2004년 12월 : 애리조나 주립대학교 전기공학과(공학박사)

2009년 3월 ~ 현재 : 부경대학교 정보통신공학과 교수

관심분야 : 시스템-온-칩 설계, 고주파 회로 설계, 임베디드 시스템 설계