이산 루프필터를 이용한 시그마-델타 변조기 Fractional-N 위상고정루프

초록

위상고정루프는 넓은 대역폭을 가지기 위해 Fractional-N 분주기를 사용한다. 넓은 대역폭을 확보하는 대신, Fractional-N 위상고정루프는 Fractional 스퍼의 문제점을 가지게 된다. 본 논문은 Fractional 스퍼를 줄이기 위해 시그마-델타 변조기와 이산 루프필터를 사용하였다. 시그마-델타 변조기는 신호를 무작위로 생성하고, 잡음정형이 되도록 하여 작은 크기의 스퍼 값을 가지는 Fractional-N 위상고정루프를 구현 할 수 있도록 해준다. 3개의 스위치로 제어되는 이산 루프필터는 ΔΔVLPF 전압 크기를 줄여 칩의 면적은 비슷하고 Fractional 스퍼 크기는 감소시킨다. 제안된 회로는 Hspice를 사용하여 시뮬레이션 하였으며, 기존의 Fractional-N 위상고정루프 보다 우수한 특성의 결과를 얻을 수 있었다.

Abstract

PLL have used a fractional-N divider to achieve wide bandwidth. Fractional-N PLL can achieve a wide bandwidth but it causes fractional spurs. In this paper, the sigma-delta modulator is used to reduce fractional spur in divider. But it need to use the large size of loop filter. To reduce the fractional spurs, sigma-delta modulator and a discrete loop filter are used in the proposed PLL. The sigma-delta modulator generates random signal and does a noise shaping to reduce fractional spur. The discrete loop filter which is controlled by three switches reduces the magnitude of ΔΔVLPF resulting in the reduction of fractional spur. The proposed PLL has been designed with Hspice. The simulation results show that the proposed PLL is better than conventional fractional-N PLL.

Keywords:

fractional-N PLL, sigma-delta modulator, discrete loop filter, frequency synthesizer, small size chipⅠ. 서 론

위상고정루프(Phase-locked Loop)는 통신 시스템, 디지털 회로, 디스크 드라이브 회로 등들이 필요로하는 다양한 주파수를 가진 신호를 만들 수 있다. 무선통신에서 채널간의 협소한 대역폭 때문에 위상고정루프는 저잡음과 낮은 스퍼를 가지는 어떤 특정 주파수 신호를 생성해야한다[1]. 시그마-델타 변조기를 사용한 Fractional-N 위상고정루프는 협소한 채널 대역폭의 무선 통신 시스템에 사용되는 위상고정루프도 넓은 대역폭을 가질 수 있도록 해준다[2][3]. 시그마-델타 변조기를 사용한 Fractional-N 위상고정루프는 넓은 대역폭을 가질 수 있지만, Fractional 분주기 사용으로 인한 “Fractional 스퍼”가 발생하게 된다. “Fractional 스퍼”를 줄이기 위해서 많은 구조가 제안되었다. 높은 차수의 시그마-델타 변조기를 사용하거나 디지털-아날로그 변환기(DAC)를 사용하여 구현하였다[4]-[6]. 일반적인 시그마-델타 변조기를 사용하게 되면 대역폭 바깥영역에서 잡음이 증가하게 되는 문제점이 생기게 된다. 이를 억제하기 위해 사용되는 면적이 큰 루프필터를 사용함으로 인해 전류소모와 면적이 증가하는 문제가 생기게 된다. 적응적 위상잡음 상쇄기를 활용한 Fractional-N 위상고정루프를 구현하여 넓은 대역폭과 저전력의 위상고정루프를 구현하였다. 하지만 제안된 구조는 4차 루프필터를 사용해야 한다는 점과 복잡한 구조의 디지털 블록으로 만들어지기 때문에 칩의 전체적인 크기가 커지게 된다[7]. Integer-N 분주기의 단점을 보완하고 Dual Modulus 전치분주기를 사용하여 높은 주파수에서도 저전력으로 동작하는 Fractional-N 위상고정루프는 제한적인 주파수에서 적용되고, 복잡한 구조로 인한 면적 문제가 생기게 된다[8].

본 논문은 높은 차수의 시그마-델타 변조기와 넓은 면적의 루프필터를 사용하지 않은 Fractional-N 위상고정루프를 구현하였다. 이산 루프필터를 사용하여 같은 크기의 면적을 가지더라도 낮은 Fractional 스퍼를 가지는 Fractional-N 위상고정루프를 구현하였다.

Ⅱ. 제안된 Fractional-N 위상고정루프

2.1 시그마-델타 변조기

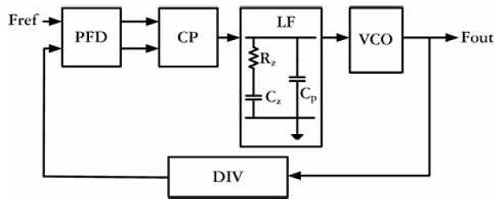

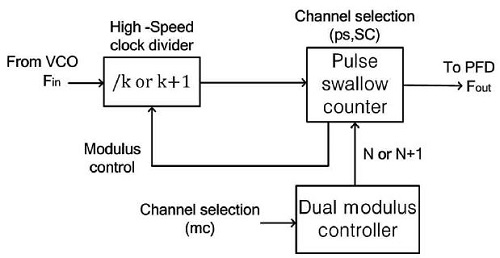

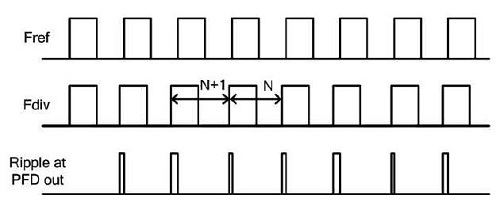

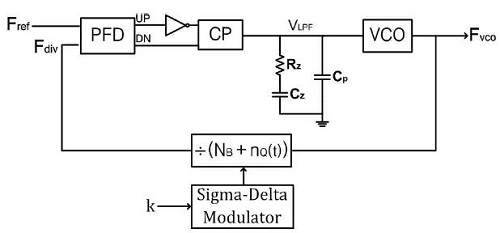

그림 1은 위상고정루프의 각 블록들을 나타낸 그림이다. 분주기 블록은 전압제발진기(VCO)의 출력을 분주해서 위상주파수 검출기(PFD)로 전달하는 역할을 하고 있다. 분주기의 구조에 따라 크게 Integer-N 구조와 Fractional-N 구조로 나뉘게 된다. 그림 2는 Fractional-N 구조의 분주기를 보여주고 있다. Integer-N 구조의 분주기에서 PS(Pulse Swallow) 카운터 값을 계속 변화시키면서 분수 부분을 구현한다. PS 카운터 값을 변화시키는 것은 그림 3과 같이 분주비가 /N에서 /(N+1)로 바뀌게 되는 것이다.

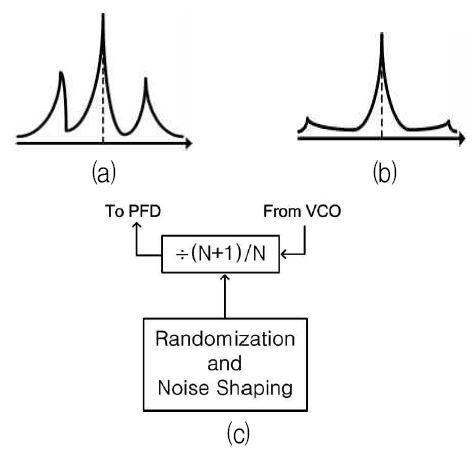

분주비가 바뀌게 되면 위상주파수 검출기 출력에 주기적인 리플이 발생하며, 위상고정루프 출력에 “Fractional 스퍼”가 생기게 된다. Fractional-N 분주기를 사용했을 때 발생하는 “Fractional 스퍼”를 줄이기 위해서는 그림 4(c)와 같이 신호의 무작위생성과 잡음정형을 할 수 있는 회로가 필요하다. 이러한 기능을 수행하기 위해서 시그마-델타 변조기를 사용한다. 시그마-델타 변조기를 사용하여 부분분수를 구현하면 그림 4(a)에서 (b)처럼 Fractional-N 분주기를 사용했을 때 생기는 큰 값의 “Fractional 스퍼”성분을 줄어들게 해준다.

그림 5에서 Fractional-N 분주기는 정수 값 NB와 분수 값 nQ (t)로 구성된다. 여기서 시그마-델타 변조기는 아날로그 k값을 입력으로 받아서 대응되는 분수 값 nQ (t)를 생성한다. 시그마-델타 변조기는 아날로그 입력을 받아서 디지털 출력을 생성하므로, 일종의 아날로그-디지털 변환기라고 할 수 있다. 시그마-델타 변조기에서는 입력 k에 비례하는 디지털 출력이 만들어지고, 이에 대응하는 분주기의 분주비를 지속적으로 변조시키면서, 평균치가 원하는 분주비를 가지도록 동작한다.

전압제발진기는 입력 전압에 비례하는 출력 주파수를 생성하게 된다. VLPF로부터 주기적인 전압파형을 가정한다면 전압제어발진기의 출력은 식 (1)과 같은 결과를 가진다.

| (1) |

여기서 ωfr은 기본 생성 주파수이다. 푸리에 시리즈 표현으로부터 ΔVLPF는 식 (2)와 같은 결과를 가진다. ΔVLPF는 위상고정루프의 위상이 고정된 후 루프필터의 전압변화량이며, ΔΔVLPF는 기준 신호 한주기 동안 변하는 루프필터의 전압변화량이다.

| (2) |

TREF는 기준 주파수의 주기이다. 식 (1)과 식 (2)로부터 전압제발진기의 출력인 식 (3)의 결과를 얻을 수 있다.

| (3) |

식 (3)에서 전압제발진기의 출력 신호에서 Fractional 스퍼”는 전하펌프(CP)에서 생기는 전류 부정합에서 발생하는 ΔΔVLPF의 크기에 비례한다. 제안된 Fractional-N 위상고정루프는 ΔΔVLPF의 값을 이산 루프필터를 사용하여 개선할 것이다. 또한 작은 면적을 가짐으로 인해 반도체 칩의 집적화가 가능해진다.

2.2 이산 루프 필터와 시그마-델타 변조기를 사용한 Fractional-N 위상고정루프

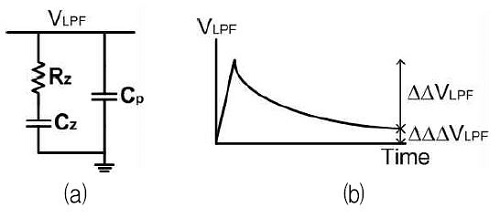

시그마-델타 변조기를 사용한 Fractional-N 위상고정루프는 대역폭 바깥 영역의 잠음과 스퍼를 낮추기 위해서 크기가 큰 루프필터를 사용해야 한다. 주파수 합성기의 역할을 하는 위상고정루프를 칩 내부에 집적화하기 위해서 잡음의 특성을 개선하고, 크기를 작게 만들어야 한다. 그림 6은 2차 루프필터를 사용하였을 때 전압파형을 보여주고 있다. 전압파형은 세 가지 ΔVLPF , ΔΔVLPF , ΔΔΔVLPF의 전압 폭으로 정의 할 수 있다. ΔVLPF는 위상고정루프의 위상이 고정된 후 루프필터의 전압변화량이며, 크기가 작을수록 잡음특성이 좋아진다. ΔΔVLPF는 위상주파수 검출기에서 발생하는 UP/DN 신호에 의해 기준 신호 한주기 동안 변하는 루프필터의 전압변화량이다. ΔΔVLPF는 UP/DN 신호 한 주기 동안의 전압변화량이기 때문에 작을수록 스퍼 크기가 줄어든다. ΔΔΔVLPF는 UP/DN 신호 한 주기 동안의 최종 변화량이기 때문에 ΔΔΔVLPF/ΔΔVLPF크기에 따라 작을수록 안정적이다.

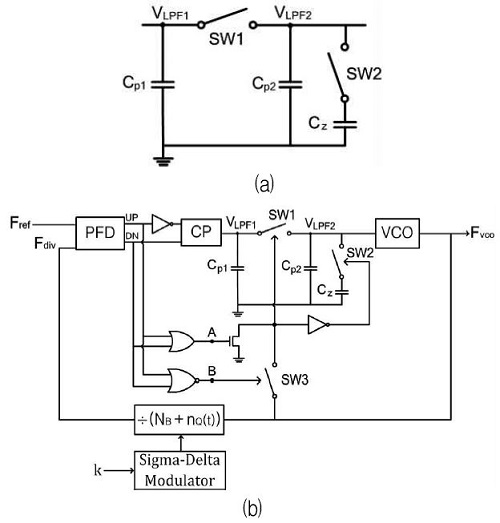

그림 7(a)는 기존의 시그마-델타 변조기를 사용한 Fractional-N 위상고정루프에서 2차 루프필터대신 면적과 잡음의 크기를 줄이기 위한 이산 루프필터의 그림이다. 그림 7(b)는 이산 루프필터로 대체한 제안된 Fractional-N 위상고정루프의 모습이다. 이산루프필터에서 3개의 스위치는 UP/DN신호로 제어한다. UP/DN신호가 발생하면 모든 스위치는 ‘off’상태가 된다. SW3은 UP/DN신호가 발생되지 않을 때 항상 ‘on’상태가 되고, SW1과 SW2는 서로 겹치지 않게 ‘on’상태가 된다.

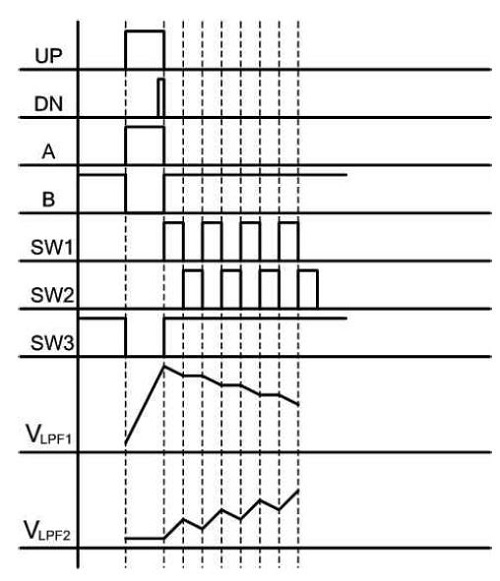

그림 8은 스위치상태에 따른 VLPF1와 VLPF2의 전압파형을 나타냈다. UP/DN신호에 따라 A지점과 B지점의 전압파형이 결정된다.

UP신호가 ‘High’상태가 되면 OR Gate를 통과하여 A지점의 전압파형이 ‘High’상태가 되고, B지점은 NOR 게이트를 통과하여 ‘Low’상태가 된다. B지점의 전압파형이 ‘Low’상태가 되면 SW3은 ‘off’상태가 되기 때문에 SW1 역시 ‘off’상태가 된다. UP 신호에 의해 CP에서 나오는 전류는 CP1으로 충전되어 VLPF1의 전압은 증가하게 된다. UP신호가 다시 ‘Low’상태가 되면 SW3은 ‘on’이 되고, FVCO 주기에 따라 SW1과 SW2가 엇갈리게 ‘on’ 혹은 ‘off’ 상태가 된다. SW1이 ‘on’상태가 되면 CP1에서 전류가 흘러나와 CP2로 흘러 VLPF 2의 전압이 증가한다. SW1이 ‘off’상태가 되고 SW2가 ‘on’상태가 되면 CP1에서 전류가 나오지 않아 VLPF 1 의 전압이 일정해지고, CP2에서 CZ로 전류가 흘러나와 VLPF2의 전압이 낮아진다. 2차 루프필터와 같이 큰 저항과 커패시터를 사용하지 않고서도 같은 모양의 전압파형을 만들어주어 작은 면적으로도 안정성을 확보할 수 있다.

Ⅲ. 시뮬레이션 결과

시뮬레이션에 사용된 기존 회로의 파라미터는 R = 200Ω, CP = 2nF , CZ = 100pF , ICP = 25uA이다. 제안된 회로의 파라미터는 CP1 = 200pF , CP2 = 200pF , CZ = 1.6nF , ICP = 25uA이다. 입력 주파수는 28MHz이고, 목표 주파수는 1GHz이다. 전압제어발진기의 이득은 330MHz/V로 하였다.

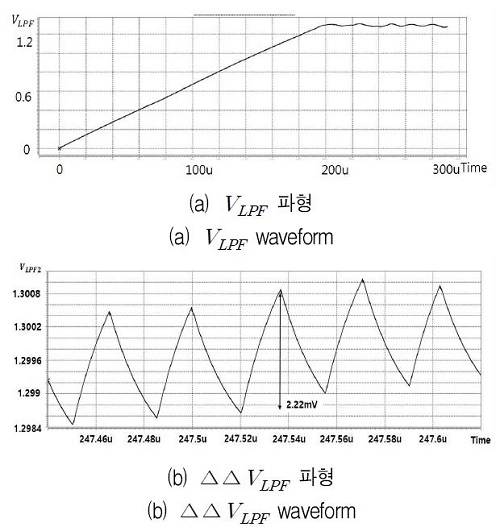

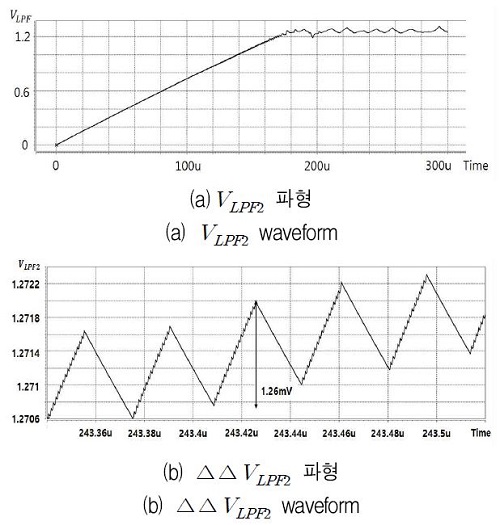

그림 9(a)는 기존의 Fractional-N 위상고정루프 회로의 VLPF 파형 모습이다. 그림 9(b)에서 Fractional 스퍼 크기를 결정하는 ΔΔVLPF2 값은 2.22mV로 높은 값이 나왔다. 그림 10(a)는 제안된 Fractional-N 위상고정루프 회로를 사용한 VLPF2파형 모습이다. 그림 10(b)는 기존의 Fractional-N 위상고정루프 회로에서 사용된 루프필터에서 저항을 사용하지 않고 같은 크기의 커패시터를 사용한 이산루프필터 Fractional-N 위상고정루프 회로의 ΔΔVLPF2의 모습이다. ΔΔVLPF2의 값은 1.26mV로써 기존의 2.22mV보다 약 60%이상 낮아진 효과를 볼 수 있다. 이는 시그마-델타 변조기를 사용했을 때 가지는 Fractional-N 위상고정루프의 단점을 보완한 것이라고 볼 수 있다. 이산 루프필터를 사용할 경우 저항을 사용하지 않고도 같은 커패시터만을 사용하여 작은 Fractional 스퍼를 가질 수 있게 된다. 이 결과를 통해 제안된 회로는 Fractional-N 분주기와 시그마-델타 변조기를 사용하였을 때 가지게 되는 높은 Fractional 스퍼 단점을 보완 할 수 있다.

Ⅳ. 결 론

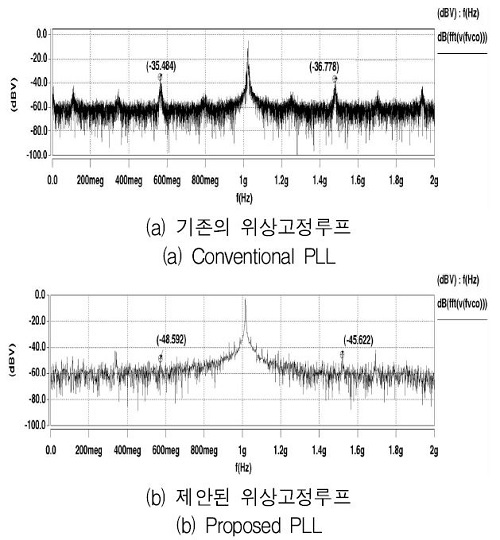

본 논문은 기존의 시그마-델타 변조기를 사용한 Fractional-N 위상고정루프의 단점을 보완하기 위해 2차 루프필터가 아닌 이산 루프필터를 사용한 회로를 제안하였다. 이산 루프필터는 전압제어발진기의 출력을 사용하여 스위치를 제어해서 동작시킨다. 2차 루프필터 대신 이산 루프필터를 사용하면 같은 면적에서도 Fractional 스퍼가 9dB 정도 감소하게 되어 우수한 성능의 Fractional-N 위상고정루프를 설계 할 수 있다. Hspice를 사용하여 시뮬레이션 하였으며, 기존의 Fractional-N 위상고정루프 보다 우수한 특성의 결과를 얻을 수 있었다.

Acknowledgments

이 논문은 부경대학교 자율창의학술연구비(2017년)에 의해서 연구되었음.

References

-

B. Razavi, "Challenges in the design of frequency synthesizers for wireless applications", IEEE Custom Integrated Circuits Conf., p395-402, May), (1997.

[https://doi.org/10.1109/cicc.1997.606653]

-

T. A. D. Riley, M. A. Copeland, and T. A. Kwasniewski, "Delta-sigma modulation in fractional-N frequency synthesis", IEEE J. Solid- State Circuit, 28(5), p553-559, May), (1993.

[https://doi.org/10.1109/4.229400]

- W Rhee, B. Song, and A. Ali, "A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-bit third-order Δ-Σ modulator", IEEE J. Solid-State Circuit, 35(10), p1453-1460, Oct), (2000.

- E. Temporiti, G. Albasini, R. Castello, and M. Colombo, "A 700-KHz bandwidth ΔΣ fractional synthesizer with spurs compensation and linearization techniques for WCDMA applications", IEEE J. Solid-State Circuit, 39(9), p1446-1454, Sept), (2004.

- S. Pamarti, L. Jansson, and I. Galton, "A wideband 2.4-GHz delta-sigma fracional-N PLL with 1-Mb/s in-loop modulation", IEEE J. Solid-State Circuit, 39(1), p49-62, Jan), (2004.

- S. E. Meninger, and M. H. Perrott, "A fracional-N synthesizer architecture utilizing a mismatch compensated PFD/DAC structure for reduced quantization-induced phase noise", IEEE Trans. Circuits Syst. Ⅱ, 50(11), p839-848, Nov), (2003.

-

Y. Zhang, J. H. Mueller, B. Mohr, L. Liao, A. Atac, R. Wunderlich, and S. Heinen, "A Multi- Frequency Multi-Standard Wideband Fractional-N PLL With Adaptive Phase-Noise Cancellation for Low-Power Short-Range Standards", IEEE Transactions on Microwave Theory and Techniques, 64(4), p1133-1142, Apr), (2016.

[https://doi.org/10.1109/tmtt.2016.2536022]

-

M. Zackriya V, J. Reuben, and H. M Kittur, "A low power dual modulus prescaler for fractional-N PLL synthsizer", Electronics and Communication Systems (ICECS), p1-4, Feb), (2014.

[https://doi.org/10.1109/ecs.2014.6892664]