오버샘플링과 CIC 필터를 이용한 14-bit 1-kS/s SAR ADC

초록

소면적 및 저전력 센서 응용을 위한 14-bit 1-kS/s 축차 근사 레지스터(SAR, Successive Approximation Register) 아날로그-디지털 변환기(ADC, Analog-to-Digital Converter)를 제안한다. 제안된 ADC는 128의 오버샘플링 비율(OSR, Oversampling Ratio)을 가지는 12-bit SAR ADC와 데시메이션을 위한 1차 구조의 CIC(cascaded integrator-comb) 필터로 구성된다. 아날로그 입력 신호는 12-bit 128-kS/s SAR ADC에 의해 12-bit의 디지털 신호로 변환된 다음, CIC 필터의 데시메이션 동작에 의해 1 kHz의 샘플링 비율을 가지는 14-bit 데이터로 변환된다. 12-bit SAR ADC는 1.8V 전원을 사용하는 180-nm CMOS 공정에 의해 구현되며, 1차 구조의 128의 데시메이션 비율을 가지는 CIC 필터는 FPGA를 통해 구현된다. 77 Hz의 주파수를 가지는 아날로그 입력 신호에 대해 12-bit 128-kS/s SAR ADC의 측정된 SNDR과 ENOB는 각각 72.09 dB과 11.67 bit이며, 제안된 1-kS/s SAR ADC는 128의 OSR과 CIC 필터의 적용을 통해 82.53 dB의 SNDR과 13.42 bit의 ENOB의 특성을 가진다.

Abstract

A 14-bit 1-kS/s Successive Approximation Register(SAR) Analog-to-Digital Converter(ADC) is proposed for small area and low power sensor applications. It consists of a 12-bit SAR ADC with an Oversampling Ratio(OSR) of 128 and a first-order Cascaded Integrator-Comb(CIC) filter for decimation. The analog input signal is converted to a 12-bit digital signal by the 128-kS/s SAR ADC, which is then converted to 14-bit data with a sampling rate of 1 kHz by integration and decimation in the CIC filter. The 12-bit SAR ADC is implemented using a 180 nm CMOS process with a 1.8 V supply, and the CIC is implemented using a FPGA with a first-order structure and a decimation ratio of 128. For an analog input signal with a frequency of 77 Hz, the measured SNDR and ENOB of the 12-bit 128-kS/s SAR ADC are 72.09 dB and 11.67 bits, respectively, while the proposed 1-kS/s SAR ADC is characterized by an SNDR of 82.53 dB and an ENOB of 13.42 bits by applying an OSR of 128 and the CIC filter.

Keywords:

SAR, ADC, oversampling, cascaded integrator-comb filterⅠ. 서 론

최근 휴대용 의료기기, 계측 장비, 스마트폰, 웨어러블 기기 등 무선 기기의 산업이 급속도로 성장하였다. 이들 기기는 생체신호와 같은 외부 아날로그 신호를 내부 프로세서에서 처리할 수 있도록 디지털 신호로 변환하는 아날로그-디지털 변환기(ADC, Analog-to-Digital Converter)를 사용한다. 이러한 응용 분야에 사용되는 ADC는 배터리와 같은 공급 전력이 한정된 환경에서 장기간 동작할 수 있도록 저전력 설계와 휴대에 용이하도록 크기를 줄이는 소면적 설계가 요구된다[1]. 축차 근사 방식(SAR, Successive Approximation Register)의 ADC는 저전압에서 최소한의 아날로그 회로를 사용하여 구현되며 매우 적은 소비전력과 소면적의 특성을 가진다[2]. 이러한 특성으로 인해 지자기 신호, 생체신호, 배터리 전압 등의 저주파 아날로그 신호를 변환하는 읽기 전용 집적 회로(ROIC, Readout Integrated Circuit)에 널리 사용된다. 그러나 SAR ADC에 사용되는 디지털-아날로그 변환기(DAC, Digital-to-Analog Converter)의 선형성이 ADC의 해상도를 제한한다[3]. SAR ADC의 동적 특성을 향상하기 위해 적분 연산을 추가하는 noise-shaping SAR ADC가 발표되었지만, 아날로그 회로 설계의 복잡성을 증가시킨다는 단점이 있다[4]. 본 논문에서는 소면적 및 저전력 센서 애플리케이션을 위해 SAR 아키텍처를 사용하는 14-bit ADC를 제안한다. 추가적인 아날로그 회로 없이 12-bit SAR ADC의 샘플링 속도를 128배 증가시키는 오버샘플링 기법과 CIC(Cascaded Integrator-Comb)[5] 구조의 데시메이션 디지털 필터를 적용하여 14-bit의 해상도를 갖는다. 본 논문의 II장에서는 오버샘플링 12-bit SAR ADC와 CIC 필터의 구조와 동작을 설명하고 III장에서는 FPGA를 통해 구현된 CIC 필터가 적용된 14-bit 1-kS/s SAR ADC 측정 결과를 서술한다. 그리고 IV장에서 결론을 제시하며 논문을 마무리한다.

Ⅱ. 오버샘플링 SAR ADC & CIC 필터

2.1 전체 블록도 및 12-bit SAR ADC

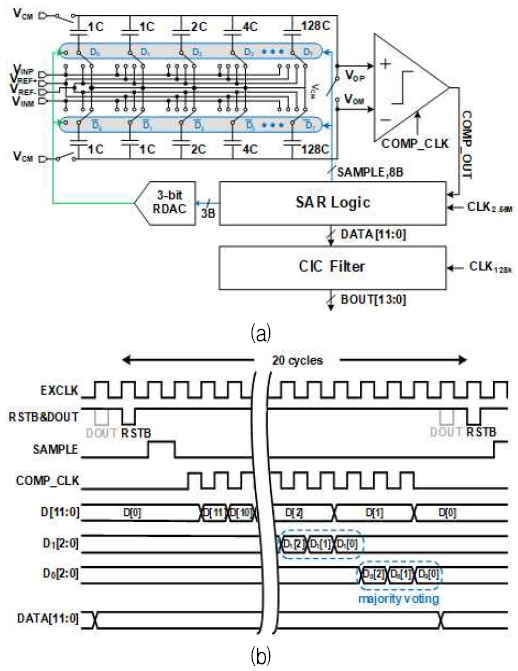

그림 1(a)에 나타낸 제안된 14-bit 1-kS/s SAR ADC는 오버샘플링 비율(OSR, Oversampling Ratio)이 128인 12-bit SAR ADC와 데시메이션 비율이 128인 1차 구조의 CIC 필터로 구성된다. 12-bit SAR ADC는 DAC의 면적을 줄이기 위해 9-bit VCM 기반의 커패시터 DAC와 3-bit 저항 DAC를 결합한 CRDAC(Capacitor-Resistor-based DAC)를 사용한다[6][7]. 9-bit VCM 기반의 커패시터 DAC는 SAR ADC의 아날로그 입력 신호에 대해 샘플 및 홀드 동작을 수행한다. 비교기는 CRDAC의 차동 출력을 비교하여 양자화를 수행한다. SAR 로직은 CRDAC를 제어하는 것을 포함한 ADC의 전반적인 동작을 제어하기 위한 제어 신호를 생성하고 12-bit의 디지털 코드를 CIC 필터로 출력한다. CIC 필터는 12-bit SAR ADC의 출력을 변환하는 동작을 수행하며, 최종적으로 14-bit 1-kS/s의 데이터를 출력한다. 12-bit SAR ADC는 그림 1(b)와 같이 외부 클록(EXCLK)에 동기되어 아날로그 전압 샘플 이후 12번의 데이터 변환을 진행한다.

Proposed SAR ADC using oversampling and CIC filter(a) Block diagram (b) Timing diagram of 12-bit SAR ADC

특히, 다양한 노이즈로부터 안정적인 디지털 코드의 하위 2 bit 신호인 D[1:0]을 결정하기 위한 voting 과정을 포함한 12-bit SAR ADC의 동작은 외부 클록의 20주기를 필요로 한다. 따라서, 128배의 오버샘플링을 수행하기 위하여 12-bit SAR ADC의 SAR 로직에 공급되는 외부 클록은 2.56 MHz의 주파수를 가진다.

2.2 CIC 필터 구조

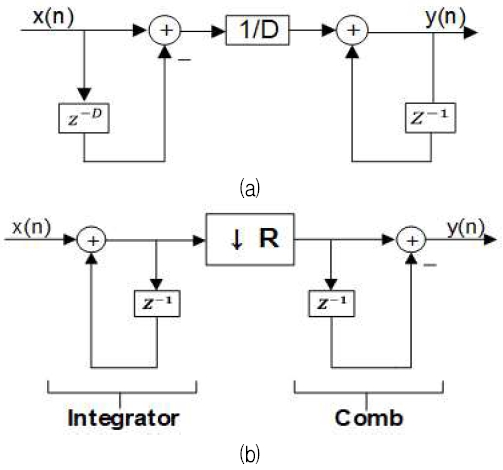

CIC 필터는 재귀 누적 합 필터에서 기원한 효율적인 연산 구조의 디지털 필터이다[8]. 그림 2(a)는 재귀 누적 합 필터의 블록도를 나타낸다. 재귀 누적 합 필터는 저역 통과 필터 역할을 하는 FIR(Finite Impulse Response) 필터 중 가장 기본적인 형태인 이동 평균 필터에서 덧셈기의 부담을 크게 줄여 산술적으로 효율적인 형태로 변형한 디지털 필터이다. 재귀 누적 합 필터는 지연된 입력 신호와 새로이 입력된 신호의 차이를 시간 지연만큼 뺄셈하여 평균값을 얻고 이전의 출력값과 합한 결과를 출력하는 FIR 필터이며 신호를 누적하고 평균값을 얻는 과정을 통해 저역 통과 필터 역할을 수행한다. 재귀 누적 합 필터의 시간 영역 출력은 식 (1)과 같고 전달함수는 식 (2)와 같다. 여기서 n은 시간 영역의 인덱스이며, D는 필터의 지연 길이를 나타낸다.

| (1) |

| (2) |

그림 2(b)는 1차 CIC 필터의 블록도를 나타낸다. 1차 CIC 필터는 FIR 필터 중 그림 2(a)의 재귀 누적 합 필터와 동일한 구조를 가지지만, CIC 필터는 곱셈기를 사용하지 않아 산술적으로 효율적인 연산이 가능하다. 식 (3)과 (4)는 각각 CIC 필터의 시간 영역 출력, 전달함수를 나타내며 상기 언급한 재귀 누적 합 필터에서 D가 1일 때의 출력과 동일하다.

| (3) |

| (4) |

이를 통해 CIC 필터가 곱셈기 없이 동일한 저역 통과 필터로 기능하며 곱셈기를 사용하지 않아 더욱 효율적인 연산이 가능함을 알 수 있다. CIC 필터의 다운 샘플러, comb 필터 및 truncator의 동작 주파수는 다운 샘플링 비율만큼 낮아진 주파수와 같아 저전력 동작이 가능한 장점을 가진다.

그림 3은 1차 CIC 필터의 진폭 응답을 나타낸다. 식 (5)는 M 차수의 CIC 필터 이득을 나타내며 sinc 함수로 근사화된다.

| (5) |

Sinc 함수 형태의 이득을 가지는 CIC 필터는 통과 대역에서 왜곡이 발생하고 차단 대역에서의 감쇠가 적다는 단점이 있다. 고차수 필터를 사용하거나 선행 또는 후행하는 보상 FIR 필터를 추가함으로써 통과 대역에서 왜곡을 줄이고 차단 대역 감쇠를 늘릴 수 있다[9][10]. 그러나 하드웨어 면적과 전력 소모가 증가하는 단점이 있어 최근에는 저전력/소면적 설계를 위해 CIC 필터 단일로 사용하는 추세이다. 그림 4는 12-bit ADC를 위해 설계된 1차 데시메이션 CIC 필터의 블록도이다.

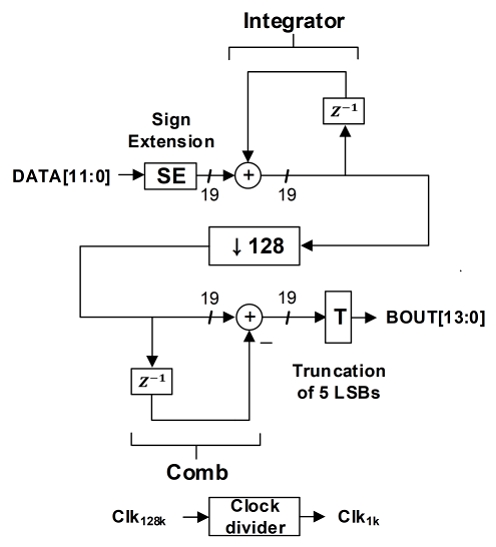

제안된 14-bit 1-kS/s SAR ADC에서는 12-bit SAR ADC의 고주파 대역의 노이즈를 고려하여 1차 구조의 CIC 필터를 사용한다. CIC 필터의 적분기의 연산 과정에서 발생하는 오버플로우를 제거하고 정확한 연산을 위하여 CIC 필터는 데이터를 비포화 2의 보수로 연산한다. 또한, 각 연산 단계에서 레지스터는 적절한 길이의 레지스터 비트 길이를 가진다. 레지스터의 최소 비트 길이 registerbit는 식 (6)과 같이 계산된다. inputbit는 입력 데이터 비트 길이이고, M은 필터의 차수이다. 그리고 N은 차동 지연 길이를 뜻하며 R은 다운 샘플링 비율을 의미한다.

| (6) |

입력 12-bit의 디지털 신호, 데시메이션 비율 128, 그리고 필터의 차수 1을 대입하여 최소 비트 길이는 19-bit로 결정하였다. Sign extension 블록에서 입력 12-bit 데이터를 2의 보수로 변환하고 19-bit로 비트 길이를 확장한다. 클록 분주기는 입력 128 kHz 클록을 분주하여 1 kHz의 클록을 생성한다. 적분기는 입력 신호를 누적하는 과정을 통해 신호의 저주파 성분을 강조하고 고주파 성분을 억제하는 역할을 한다. 이를 통해 저역 통과 필터링 동작을 수행한다. 다운 샘플러는 신호의 샘플링 주기를 데시메이션 비율만큼 변환한다. 다운 샘플링된 적분기의 출력은 comb 필터를 통과하면 입력과 동일한 파형으로 복원된다. 이 과정에서 comb 필터는 주기적으로 발생하는 잔여 고주파 성분을 제거하며 입력 신호를 강조한다. 앞서 적분기 연산 과정에서 bit growth 현상으로 인해 증가한 비트 길이를 다시 줄이기 위하여 bit truncation 블록을 통해 하위 5개의 LSB(Least Significant Bit)를 버린 후 부호가 없는 이진수로 변환한다. 이 과정을 통하여 최종적으로 14-bit의 출력을 얻는다.

2.3 Verilog HDL 설계

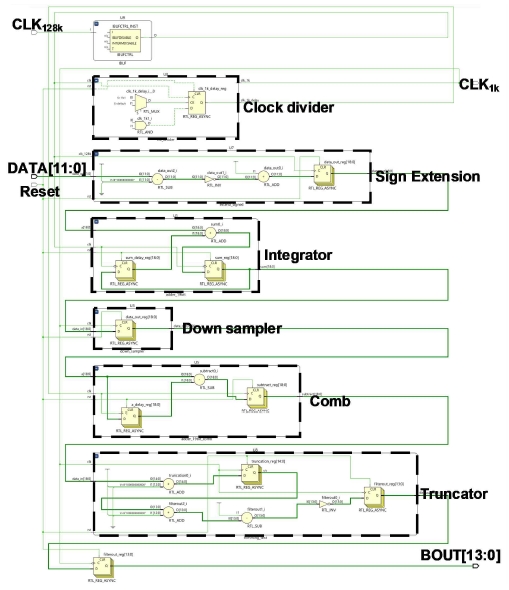

그림 5는 VIVADO 프로그램을 사용하여 Verilog HDL로 설계한 1차 데시메이션 CIC 필터의 논리 회로도이다. 비포화 2의 보수 연산을 위하여 입력 DATA[11:0]와 출력 BOUT[13:0]을 제외한 모든 블록에서 데이터 형식은 signed로 선언되었다. 설계된 CIC 필터의 동작을 검증하기 위해 테스트 벤치 작성 후 측정된 12-bit SAR ADC의 데이터를 활용하여 시뮬레이션을 진행하였다.

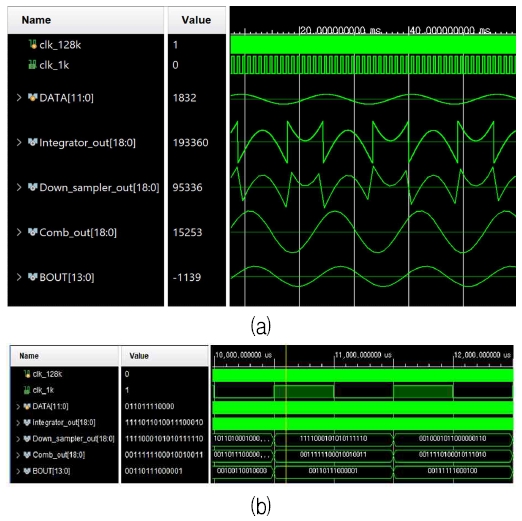

그림 6은 CIC 필터의 입력, 출력, 내부 노드에 대한 파형과 디지털 코드에 대한 시뮬레이션 결과이다. 그림 6(a)의 시뮬레이션 출력 파형에서 적분기의 2의 보수 연산 과정에서 오버플로우가 발생하는 것을 확인할 수 있다. 적분기의 출력은 다운 샘플러를 거치며 1-kS/s의 샘플링 주기로 변환된다. 다운 샘플러 및 comb 필터와 truncator 블록은 클록 분주기에서 입력 128 kHz 클록을 분주하여 생성한 1 kHz 클록에 동기화하여 동작한다. 다운 샘플링된 신호는 comb 필터를 거치며 잔여 고주파 성분이 제거되고 저주파 대역의 입력 신호가 강조되며 원래의 정현파 파형이 복원된다. Bit truncation 블록에서 하위 5개의 LSB를 제거하는 과정을 통해 bit trimming 동작을 수행하며 최종 BOUT[13:0]의 출력을 얻는다.

Ⅲ. 측정 결과

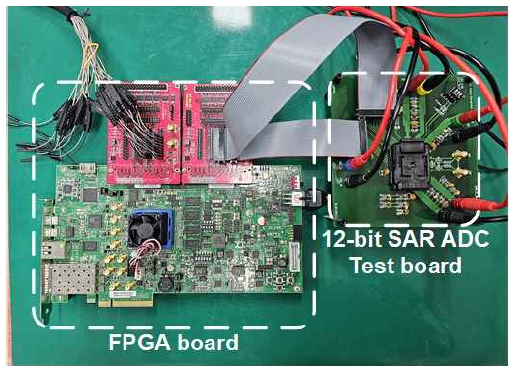

제안된 1-kS/s 14-bit SAR ADC를 위한 12-bit SAR ADC는 1.8V의 공급전압을 이용하는 180-nm CMOS 공정으로 구현하였으며, 그림 7은 제안된 FPGA 포함 14-bit SAR ADC의 평가 보드이다. 12-bit SAR ADC 테스트 보드를 통해 제작된 12-bit SAR ADC가 평가되었다. 또한, 12-bit SAR ADC에서 출력된 디지털 데이터를 리본 케이블을 통해 FPGA에 입력하고 구현된 CIC 필터에 의해 1-kS/s 14-bit 디지털 신호로 변환된 데이터를 획득함으로 14-bit SAR ADC의 측정을 수행하였다.

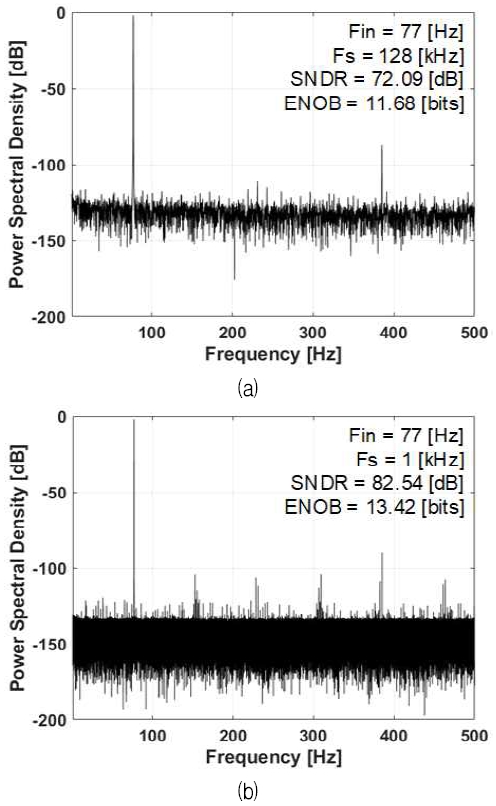

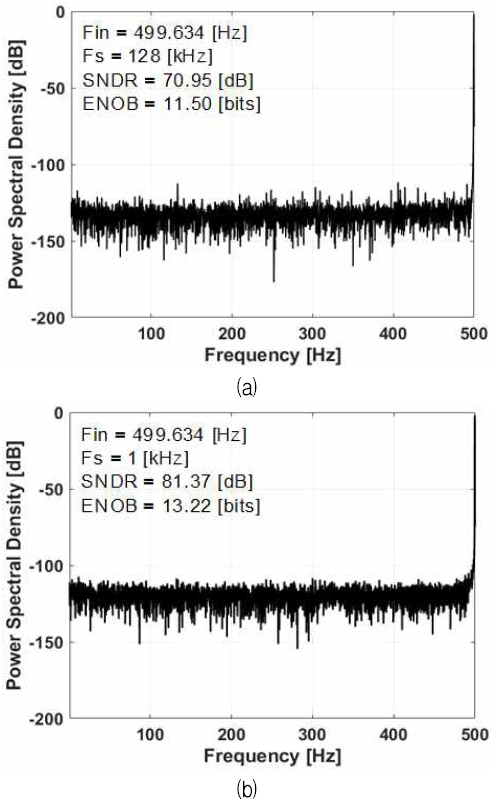

구현된 12-bit SAR ADC는 128 kHz의 샘플링 속도에서 60.42 uW의 전력을 소모하며, 주파수 77 Hz의 아날로그 입력 신호에 대해 측정된 SNDR과 ENOB는 그림 8(a)와 같이 각각 72.09 dB와 11.68 bit이다. 그림 8(b)는 1-kS/s 14-bit SAR ADC의 동적 특성을 보여준다. 측정된 SNDR과 ENOB는 각각 82.53 dB와 13.42 bit이다. 그림 9는 나이퀴스트 주파수인 499.634 Hz의 주파수를 가지는 아날로그 입력 신호에 대한 설계된 SAR ADC의 동적 특성을 보여준다. 128 kHz의 샘플링 속도에서 동작하는 12-bit SA ADC의 측정된 SNDR과 ENOB는 그림 9(a)에 나타난 바와 같이 각각 70.95 dB와 11.50 bit이다. 이 경우 오버샘플링과 CIC 필터를 추가로 이용한 1-kS/s 14-bit SAR ADC는 그림 9(b)에 보여준 바와 같이 81.37 dB의 SNDR과 13.22 bit의 ENOB의 동적 특성을 가진다.

결과적으로 저주파수를 가지는 아날로그 입력 신호에 대해 128배의 오버샘플링이 적용된 12-bit SAR ADC에 1차 CIC 필터의 적용함으로써 동적 특성 SNDR과 ENOB이 각각 약 10.44 dB과 1.74 bit만큼 향상되었다. 표 2는 측정된 12-bit SAR ADC와 14-bit SAR ADC의 특성을 보여준다.

Ⅳ. 결 론

본 연구에서는 오버샘플링이 128인 12-bit SAR ADC와 1차 CIC 필터를 이용하여 14-bit 1-kS/s SAR ADC를 구현하였다. 14-bit SAR ADC는 저주파수를 가지는 아날로그 입력 신호에 대해 12-bit SAR ADC에 비해 SNDR 10.45 dB, ENOB 1.57 bit 향상되었다. 12-bit SAR ADC는 0.116 mm2의 면적을 가지며 128-kS/s의 샘플링 속도에서 60.42 uW의 전력을 소모한다. FPGA를 통해 구현된 1차 CIC 필터는 128-kS/s 12-bit 디지털 데이터를 1-kS/s 14-bit 디지털 데이터로 변환하였고, 추가적인 아날로그 회로 없이 ADC의 동적 성능을 향상시켰다.

Acknowledgments

이 연구는 금오공과대학교 대학 학술연구비로 지원되었음 (2022학년도)

References

-

X. Tang, J. Liu, Y. Shen, S. Li, L. Shen, A. Sanyal, K. Ragab, and N. Sun, "Low-Power SAR ADC Design: Overview and Survey of State-of-the-Art Techniques", in IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 69, No. 6, pp. 2249-2262, Jun. 2022.

[https://doi.org/10.1109/TCSI.2022.3166792]

-

M.-U. Seong, J.-H. Lee, and J.-Y. Ryu, "Design of a Low Area 12-bit 1MSps SAR ADC", The Journal of Korean Institute of Information Technology, Vol. 13, No. 2, pp. 1-6, Feb. 2015.

[https://doi.org/10.14801/jkiit.2015.13.2.1]

-

W.-En Lee and T.-H. Lin, "A 0.6-V 12-bit Set-and-Down SAR ADC With a DAC-Based Bypass Window Switching Method", IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 70, No. 9, pp. 3223-3227, Sep. 2023.

[https://doi.org/10.1109/TCSII.2023.3266605]

-

X. Tang, X. Yang, W. Zhao, C.-K. Hsu, J. Liu, L. Shen, A. Mukherjee, W. Shi, S. Li, D. Z. Pan, and N. Sun, "A 13.5-ENOB, 107-μW Noise-Shaping SAR ADC With PVT-Robust Closed-Loop Dynamic Amplifier", IEEE Journal of Solid-State Circuits, Vol. 55, No. 12, pp. 3248-3259, Dec. 2020.

[https://doi.org/10.1109/JSSC.2020.3020194]

-

E. Hogenauer, "An economical class of digital filters for decimation and interpolation", in IEEE Transactions on Acoustics, Speech, and Signal Processing, Vol. 29, No. 2, pp. 155-162, Apr. 1981.

[https://doi.org/10.1109/TASSP.1981.1163535]

-

H. Son, W. Yang, H. Jung, and Y.-C. Jang, "1-kS/s 12-bit SAR ADC with Burst Conversion", 2023 20th International SoC Design Conference (ISOCC), Jeju, Korea, pp. 295-296, Oct. 2023.

[https://doi.org/10.1109/ISOCC59558.2023.10396006]

-

B. Sedighi, A. T. Huynh, E. Skafidas, and D. Micusik, "Design of hybrid resistive-capacitive DAC for SAR A/D converters", 2012 19th IEEE International Conference on Electronics, Circuits, and Systems (ICECS 2012), Seville, Spain, pp. 508-511, Dec. 2012.

[https://doi.org/10.1109/ICECS.2012.6463697]

-

H. Patel, S. Trivedi, R. Neelkanthan, and V. R. Gujraty, "A Robust UART Architecture Based on Recursive Running Sum Filter for Better Noise Performance", 20th International Conference on VLSI Design held jointly with 6th International Conference on Embedded Systems (VLSID'07), Bangalore, India, pp. 819-823, Jan. 2007.

[https://doi.org/10.1109/VLSID.2007.25]

-

G. Xuan and D. Wei-tao, "Analysis and design of CIC compensation filter", 2011 International Conference on Electric Information and Control Engineering, Wuhan, China, pp. 3969-3971, Apr. 2011.

[https://doi.org/10.1109/ICEICE.2011.5778276]

-

G. J. Dolecek and f. harris, "Design of CIC Compensator Filter in a Digital IF Receiver", 2008 International Symposium on Communications and Information Technologies, Vientiane, Laos, pp. 638-643, Oct. 2008.

[https://doi.org/10.1109/ISCIT.2008.4700271]

2024년 8월 : 금오공과대학교 전자공학부(공학사)

관심분야 : 고해상도 아날로그-디지털 변환기 포함 아날로그 혼성신호 집적회로 설계

2023년 2월 : 금오공과대학교 전자공학부(공학사)

2023년 2월 ~ 현재 : 금오공과대학교 반도체시스템공학과 석사과정

관심분야 : SAR ADC를 포함한 아날로그-디지털 변환기

1999년 2월 : 경북대학교 전자전기공학부(공학사)

2001년 2월 : 포항공과대학교 전자공학과(공학석사)

2005년 2월 : 포항공과대학교 전자공학과(공학박사)

2005년 3월 ~ 2009년 8월 : 삼성전자 반도체총괄 책임연구원

2009년 9월 ~ 현재 : 금오공과대학교 전자공학부 교수

관심분야 : 아날로그-디지털 변환기 및 고속 인터페이스를 위한 클록발생기와 송수신기 포함 아날로그 집적회로