이중 공진 인덕터 피킹 기술을 적용한 28-GHz 대역폭의 60-GHz CMOS 드라이버 증폭기 설계

초록

본 논문에서는 밀리미터파 대역에서 동작하며 광대역 특성을 제공하는 2단 드라이버 증폭기(DA, Driver Amplifier)를 제안한다. 제안하는 DA는 65-nm CMOS 공정을 기반으로 설계되었으며, 이중 공진 특성을 이용하여 대역폭을 확장하였다. 이를 위해 두 번째 증폭 단을 서로 다른 크기의 트랜지스터로 구성된 병렬 구조로 설계하였고, 각 경로의 드레인에 인덕터를 적용하여 서로 다른 기생 커패시턴스와의 공진을 통해 이중 공진 특성을 형성하였다. 또한 드레인 인덕터 간 비반전 자기 결합을 도입함으로써 칩 면적을 감소시켰다. 시뮬레이션 결과, 제안된 DA는 기존 구조 대비 약 6.6GHz 향상된 41.9GHz~70.0GHz 범위에서 총 28.1GHz의 -3dB 대역폭을 제공한다. 제안하는 DA는 0.8V 전원 전압에서 전체 29mA의 전류를 소모한다.

Abstract

This paper proposes a two-stage Driver Amplifier (DA) operating in the millimeter-wave band and providing wideband characteristics. The proposed DA is designed using a 65-nm CMOS technology, and its bandwidth is extended by exploiting a dual-resonance technique. To achieve this, the second gain stage is implemented as a parallel structure composed of transistors with different sizes. Inductors are applied to each path to form dual resonances with different parasitic capacitances. In addition, non-inverting magnetic coupling between the inductors is introduced to reduce the chip area. According to the simulation results, the proposed DA achieves a -3dB bandwidth of 28.1GHz over the frequency range of 41.9GHz~70.0GHz, representing an improvement of approximately 6.6GHz compared to the conventional structure, while consuming about 29mA from a 0.8V supply.

Keywords:

amplifier, CMOS, millimeter-wave, transformer, widebandⅠ. 서 론

5G 이동통신의 상용화로 대용량, 고속 데이터 전송의 중요성이 커지면서, 차세대 무선 시스템에서는 많은 데이터 처리를 위한 넓은 대역폭 확보가 필수적이다. 특히 초고해상도 영상, VR/AR, 실시간 클라우드 서비스 등에서는 방대한 데이터를 처리해야 하므로 광대역, 고주파 증폭 기술의 중요성이 높아지고 있으며, 이에 따라 밀리미터(Millimeter-wave) 대역에서 광대역 송수신기가 활발히 연구되고 있다[1]-[3].

기존에 보고된 밀리미터 대역 2단 드라이버 증폭기(DA, Driver Amplifier)[4][5]들은 초고주파 영역에서 트랜지스터의 기생 커패시턴스와 실리콘에서 구현할 수 있는 변압기 성능 한계로 인해 60GHz 이상의 주파수 대역에서 충분한 이득(Gain)을 유지하는 데 어려움이 있다. 따라서 60GHz 이상의 대역에서 -3dB 대역폭을 확보하기가 쉽지 않아 신호 전송 특성이 저하되는 문제가 발생한다. 이 문제를 해결하기 위해서는 충분한 -3dB 대역폭 확보가 필수적인데 기존에는 Inductive peaking 기법이 사용되었다[6]. 이 방식은 트랜지스터(Transistor)의 드레인(Drain) 단에 직렬로 온-칩 나선형 인덕터를 연결하여 기생 커패시턴스와 특정 주파수에서 공진을 통해 게인 피킹(Gain peaking)을 형성함으로써 대역폭을 확장하였다[6]. 그러나 이 설계 기법은 단일 공진 특성에 의존하고 초고주파 대역에는 인덕터의 Q 인자(Q-factor) 감소와 기생 성분에 의한 손실 증가로 인해 60GHz 이상 밀리미터 대역에서 대역폭을 확보하는 데 다소 제약이 있다.

본 연구에서는 두 번째 증폭기에서 서로 다른 크기의 트랜지스터를 병렬로 구성하고, 비반전 변압기를 적용한 새로운 형태의 2단 초광대역 드라이버 증폭기(DA)를 제안한다. 기존의 Inductive peaking 기법이 특정 주파수에서 단일 공진 효과만 제공하는 데 반해, 제안된 구조는 서로 다른 두 개의 주파수에서 공진을 활용한 이중 공진을 통해 60GHz 대역이상에서 보다 넓은 대역폭을 확보하는 것이 특징이다. 제안된 2단 DA는 65-nm CMOS 공정으로 설계되었으며, 기존 2단 증폭기와 동일한 전류를 소모하면서 약 6.6GHz의 더 넓은 대역폭을 제공한다.

Ⅱ. 기존의 Driver Amplifier

2.1 기존의 2-단 DA 구조

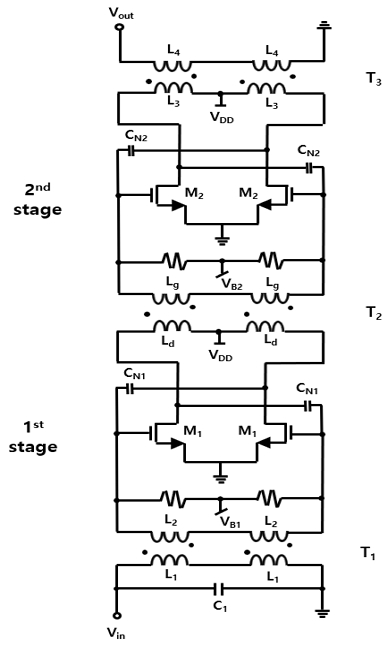

그림 1은 기존의 2-단 DA의 전체 회로도를 나타낸다. 입력단의 밸룬(T1)은 단일 위상 입력 신호를 차동 신호로 변환하여 첫 번째 단의 입력 트랜지스터 M1에 전달하며, 동시에 광대역 입력 임피던스 매칭을 수행한다. 첫 번째 증폭기 M1과 두 번째 증폭기 M2 사이에 위치한 변압기(T2)는 첫 번째 단의 출력 신호를 두 번째 단의 입력 트랜지스터 M2로 전달하는 역할을 한다. 그림 1에서, 2-단 DA의 광대역 인터스테이지 매칭을 위해 Ld=200pH, Lg=135pH, k(Magnetic coupling coefficient)=0.33의 값을 사용하였다. M1은 40um/60nm, M2는 48um/60nm의 크기를 가지며 트랜지스터의 입/출력 격리 특성을 강화하기 위해 사용된 중성화 커패시터는 CN1=17fF, CN2=19fF의 값을 가진다. 출력단의 밸룬(T3)은 두 번째 증폭기의 차동 출력 신호를 단일 신호로 변환하여 50-Ω 부하에 전달하고, 부하와의 파워 매칭을 통해 전력 손실을 최소화하여 최대 전력 전달 효율을 달성하도록 설계되었다.

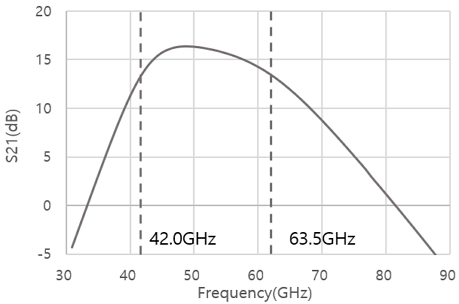

그림 1에서 첫 번째 단, 두 번째 단 증폭기의 공급 전압은 모두 VDD=800mV이고 첫 번째 단은 10.1mA, 두 번째 단은 21.2mA 전류를 소모한다. 그림 2는 그림 1의 2단 DA의 전체 주파수 응답 특성인 S21 시뮬레이션 결과를 보여준다.

그림 2에서 -3dB 대역폭은 42.0GHz~63.5GHz까지의 범위를 가지며, 약 21.5GHz에 해당하는 -3dB 대역폭을 보인다. 이때 54GHz, 60GHz, 66GHz에서의 이득은 각각 15.1dB, 13.8dB, 11.6dB이다. 그림 2에서 보는 바와 같이 기존의 2단 DA는 60GHz 이상의 높은 주파수 영역일수록 충분한 이득을 확보하지 못하여 -3dB 대역폭이 제한되고, 이득 곡선의 평탄도가 저하되는 문제가 존재한다. 이러한 현상은 트랜지스터의 기생 커패시턴스와 실리콘에서 구현된 온-칩 변압기들의 낮은 Q 인자 그리고 커플링 효율의 한계로 인해 고주파 신호 전달이 제한되기 때문이다.

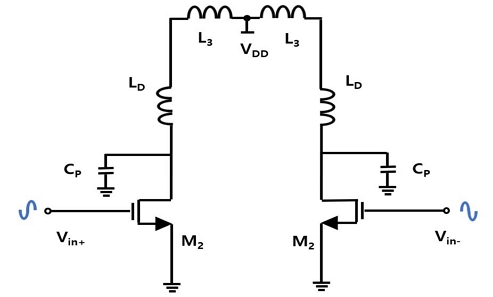

2.2 대역폭 확장을 위한 Inductive Peaking 기술

그림 3은 기존 DA 구조에서 대역폭 확장을 위해 M2의 드레인에 인덕터 LD가 적용된 증폭기 구조를 간략히 보여주고 있다. 이 Inductive peaking 회로 설계 기법은 드레인 노드에 인덕터(LD)를 추가하면 인덕터(LD)와 트랜지스터의 드레인 노드에서의 기생 커패시턴스(CP)와 공진 특성을 형성하게 된다. 이로 인해 고주파 대역에서 신호 감쇄가 완화되면서 공진 주파수 부근에서 게인 피킹이 나타난다[6]. 따라서 Inductive peaking 기법은 DA의 -3dB 대역폭을 확장하는 효과를 제공할 수 있다. 그러나 이러한 구조는 단일 공진점(Single resonance)에 의존하므로, 공진 주파수 이후의 주파수 영역에서 이득이 감소하는 근본적 한계는 여전히 가지며, 고주파로 갈수록 인덕터의 Q 인자가 감소하여 게인 피킹 효과가 크지 않다.

그림 1 회로의 -3dB 대역폭을 확장하기 위해 그림 3의 Inductive peaking DA를 그림 1의 두 번째 증폭기에 적용하여 55GHz 부근에서의 이득 저하를 보완하였다. 이를 위해 M2 드레인에 LD=60pH를 적용하여 기생 커패시터 CP=137fF와 공진을 형성하였다.

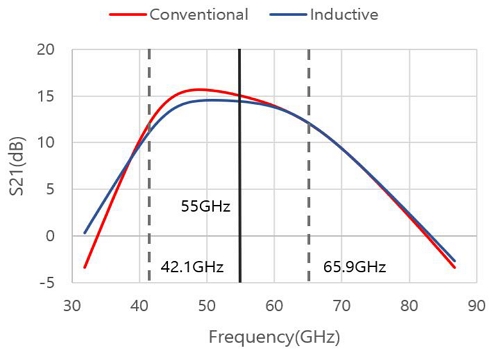

그림 4는 그림 1의 두 번째 증폭기에서 Inductive peaking을 적용하지 않았을 때와 적용하였을 때 주파수 응답 특성에 대한 비교 시뮬레이션 결과를 보여준다. 그림 4에서 보는 바와 같이 이득 유지 효과는 관찰되었으나, 뚜렷한 Peaking 효과는 나타나지 않았다. 따라서 본 논문에서는 기존의 Inductive peaking 회로 기술의 한계를 개선하고 대역폭 확장을 위해 이중 공진 특성을 형성하는 구조를 제안하였다.

Ⅲ. 제안하는 Driver Amplifier

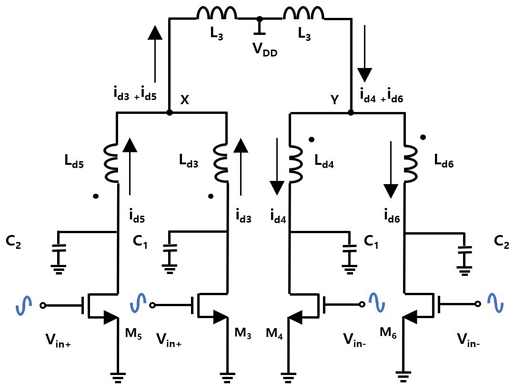

그림 5는 그림 3의 Inductive peaking 증폭기 구조를 두 개의 증폭기를 병렬 형태로 변형한 구조로 이중 공진 특성을 이용하여 대역폭을 확장하기 위해 본 논문에서 제안하는 구조이다. 그림 5에서 M3~M6 트랜지스터들은 그림 3에서 사용된 M2 트랜지스터의 크기의 절반으로 전체 전류 소모는 동일하고, 각 드레인 단에서 기생 커패시턴스 C1, C2 값은 CP의 절반 수준이 된다. Inductive peaking을 위하여 M3~M6의 각 드레인에 인덕터 Ld3~Ld6이 각각 적용되었다. M3, M5와 M4, M6의 출력 전류 id3, id5와 id4, id6는 노드 X, Y에서 각각 합쳐져서 id3+id5, id4+id6의 형태로 출력 인덕턱(L3)로 전달된다.

그림 5의 제안하는 구조에서 그림 3과 동일하게 단일 공진을 얻고자 하면, M3~M6의 기생 커패시터가 C1=C2=CP/2이므로 인덕터 값은 Ld3=Ld4=Ld5=Ld6=2⨯(LD=60pH)=120pH를 사용하면 된다. 그러나 본 논문에서는 대역폭을 확장하기 위해 이중 공진 특성을 활용해야 하므로 그림 5에서 M3, M4와 M5, M6의 사이즈를 서로 다르게 하여 기생 커패시터 값 C1, C2를 다르게 조정하였다. 이와 같이 트랜지스터의 크기를 다르게 구성함으로써 추가적으로 커패시터를 사용하지 않고 각 병렬 경로에서 서로 다른 기생 커패시턴스가 형성되어, 인덕터 Ld3~Ld6와 함께 두 개의 공진이 유도된다.

| (1) |

식 (1)과 같이 트랜지스터 M3, M4의 각 드레인 노드에서 C1=72fF과 Ld3=Ld4=120pH가 형성되는 공진 주파수는 기존 Inductive Peaking(55GHz) 구조와 거의 유사한 54GHz에서 나타난다. 반면 상대적으로 작은 크기의 트랜지스터 M5, M6은 작은 기생 커패시턴스(C2=47fF)를 가지므로, 드레인 인덕터(Ld5=Ld6=120pH)와 형성되는 공진 주파수는 기존 Inductive peaking(55GHz)보다 높은 68GHz 영역에서 형성된다. 그 결과, 두 branch의 서로 다른 공진 특성은 주파수 축 상에서 (f1=54GHz, f2=68GHz)로 분리되어 나타난다.

| (2) |

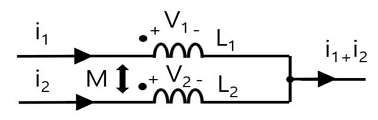

또한, 두 인덕터 Ld3와 Ld5 그리고 Ld4와 Ld6은 각각 비반전 변압기(Non-inverting transformer)로 구현 가능하다. 그림 6은 비반전 자기 결합을 설명하기 위해 서로 다른 두 인덕터 L1, L2 값을 가지는 변압기를 나타낸다. 여기서, M은 L1, L2사이의 자기 결합에 의한 상호 인덕턴스(Mutual inductance)를 의미한다. 그림 6과 식 (2)에서 보는 바와 같이, 각 변압기를 비반전 자기 결합이 되도록 구현하면 자기 결합이 서로 보강되는 방향으로 결합되어 (), 각 인덕터 L1, L2의 유효 인덕턴스 값이 각각 으로 증가하게 된다[7]. 이러한 효과는 동일한 실리콘 면적에서 더 큰 인덕턴스를 사용한 경우와 동일한 효과를 제공한다. 그림 5의 병렬 구조에서 Ld3=Ld4=Ld5=Ld6=68pH 값을 가지는 변압기를 각각 사용하여 자기 결합 없이 120pH의 인덕터들을 사용하는 경우보다 칩 사이즈를 50% 줄였다.

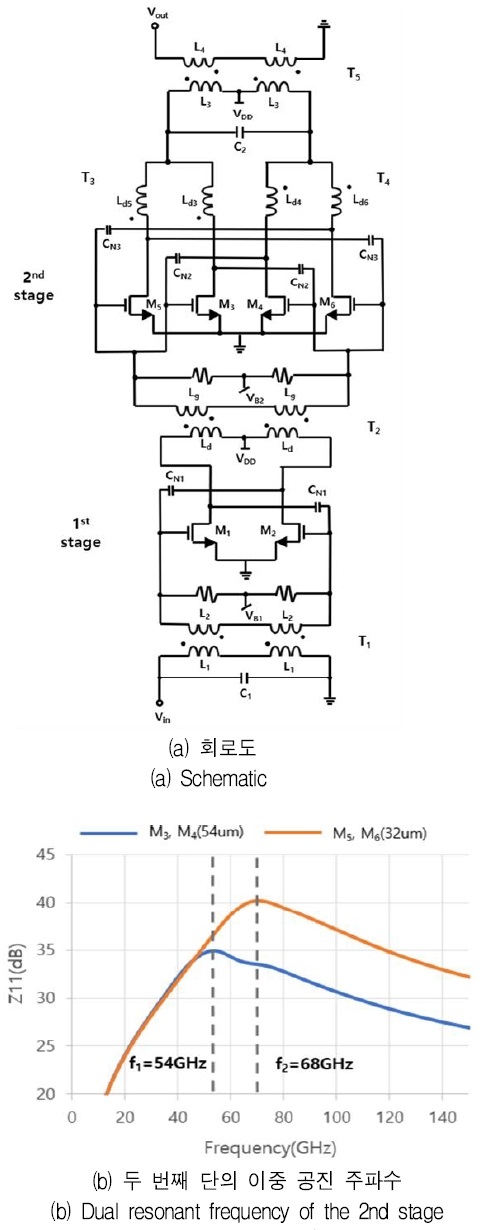

그림 7(a)은 제안된 2단 드라이버 증폭기(DA)의 전체 회로도를 보여준다. 그림 7(b)에서 보는 바와 같이 그림 5의 이중 공진(f1=54GHz, f2=68GHz)을 이용한 증폭기 구조가 두 번째 증폭기로 사용되었다. 제안하는 증폭기의 전체 대역폭은 41.9GHz~70.0GHz의 주파수 범위에서 총 28.1GHz의 넓고 평탄한 -3dB 대역폭을 확보하며, 그림 1과 그림 3의 기존 구조를 보다 더 평탄하고 넓은 -3dB 대역폭을 달성하였다. 그림 7(a)의 첫 번째 단, 두 번째 단 VDD=800mV이고 첫 번째 단은 10.1mA, 두 번째 단은 18.9mA 전류를 소모한다. 그림 7(a)의 제안하는 구조는 그림 1의 기존 구조와 동일한 전류를 소모한다.

Ⅳ. 모의실험 결과

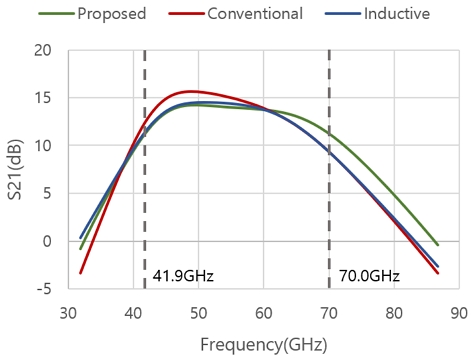

그림 8은 그림 1의 기존 2단 DA, 그림 3의 Inductive peaking 기술이 적용된 2단 DA, 그림 7(a)의 병렬 공진 경로에 비반전 변압기가 적용된 제안한 2단 DA에 대한 S21 시뮬레이션 결과를 보여주고 있다. 그림 8의 증폭기들은 공정한 대역폭 비교를 위해 동일한 크기의 트랜지스터를 사용하고 동일한 전류를 소모하였다.

그림 8에서 기존 DA 구조는 -3dB 대역폭이 42.0GHz~63.5GHz(21.5GHz)이다. 드레인에 인덕터를 삽입한 Inductive peaking DA 구조는 -3dB 대역폭이 42.1GHz~65.9GHz(23.8GHz)로 약간 개선되었다. 제안된 DA 구조는 41.9GHz~70.0GHz(28.1GHz)의 -3dB 대역폭을 나타내었다. 따라서, 제안한 구조는 동일한 전류를 소모하면서 기존 DA 대비 약 6.6GHz, Inductive peaking DA 대비 약 4.3GHz의 -3dB 대역폭 확장을 달성하면서, 고주파 영역서도 비교적 평탄한 이득 특성을 유지한다.

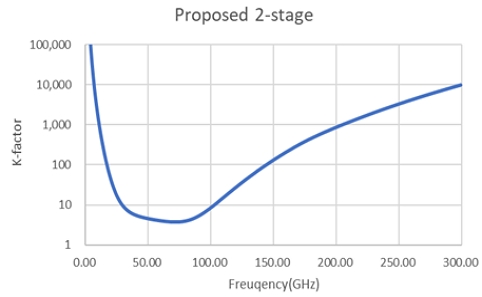

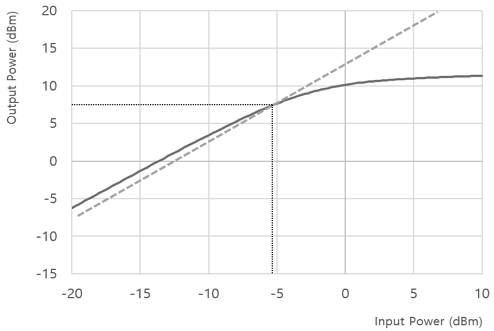

제안된 2단 DA 구조의 안정성은 Rollett's stability factor(K-factor)를 통해 평가하였다. K-factor는 증폭기의 안정성을 판단하는 대표적인 지표로, K-factor가 1 이상일 경우 안정성이 보장된다. 그림 9는 제안된 2단 DA 구조의 K-factor가 300GHz까지 1 이상임을 보여주며, 이를 통해 제안된 DA 구조가 고주파 영역에서도 안정한 동작을 유지함을 확인할 수 있다. 그림 10은 제안된 DA의 출력 P1dB 대한 시뮬레이션 결과이다. 제안된 DA는 conventional 구조와 거의 동일한 P1dB 특성을 유지하면서도 대역폭이 확장되었음을 확인할 수 있다.

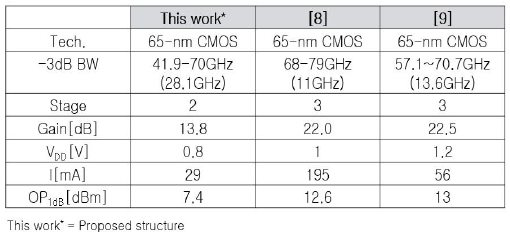

표 1은 제안된 DA 구조와 기존에 보고된 전력 증폭기들[8][9]의 성능을 비교한 결과이다. 제안된 구조는 기존에 보고된 전력 증폭기 구조들 대비 각각 17.1GHz, 14.5GHz 더 넓은 -3dB 대역폭을 확보하여 대역폭 측면에서 뚜렷한 우위를 가진다. 또한 표 1의 제안하는 2단 DA의 OP1dB 항목은 공급 전압(VDD)을 증가시키는 경우 추가적인 개선이 가능하다. 표 1에서 기존 구조[8][9]들은 충분한 이득 확보를 목적으로 3-단 구조를 사용하였다.

Ⅴ. 결 론

본 논문에서는 밀리미터파 대역에서 이중 공진 특성을 활용하여 광대역 특성을 제공하는 2단 DA를 제안하였다. 단일 공진에 의존하는 기존 Inductive peaking 구조의 한계를 극복하기 위해, 서로 다른 크기의 트랜지스터로 구성된 병렬 증폭 경로를 적용하고 비반전 변압기를 사용하였다. 그 결과, 제안된 DA는 추가적인 전류 소모 없이 41.9GHz~70.0GHz 범위에서 총 28.1GHz의 -3dB 대역폭을 달성하였다.

Acknowledgments

이 논문은 2022년 한국연구재단의 지원을 받아 수행된 연구임(2022NR073751)

References

-

M. Yang, B. Wu, and D. Zhao, "A Ka-Band Compact Active Switch With Broadband Amplifiers for Phased-Array Transceiver in 65-nm CMOS", IEEE Solid-State Circuits Letters, Vol. 2, No. 5, pp. 33-36, May. 2019.

[https://doi.org/10.1109/LSSC.2019.2920096]

-

Y. Wang, R. Wu, and J. Pang, "A 39-GHz 64-Element Phased-Array Transceiver With Built-In Phase and Amplitude Calibrations for Large-Array 5G NR in 65-nm CMOS", IEEE Journal of Solid-State Circuits, Vol. 55, No. 5, pp. 1249-1269, May 2020.

[https://doi.org/10.1109/JSSC.2020.2980509]

-

J. Yoo, D. Kim, and W. Keum, "A 140-GHz FMCW Radar Transceiver With Dual-Lens Packaging for Improved Beam Alignment in 65-nm CMOS Technology", IEEE Transactions on Microwave Theory and Techniques, Vol. 72, No. 11, pp. 6426-6442, Nov. 2024.

[https://doi.org/10.1109/TMTT.2024.3396668]

-

W. Feng, D. Chen, and C. Zhao, "A 21.5–26.4 GHz CMOS cascode driver amplifier with 13.9 dBm output power for 24G FMCW radar applications", IEEE IWS, Chengdu, China, pp. 1-3, May. 2018.

[https://doi.org/10.1109/IEEE-IWS.2018.8400883]

-

M. Yang, D. Zhao, and X. You, "A Ku-Band CMOS Balanced Driver Amplifier With Transformer-Based Notch Filter for SATCOM Phased Arrays", IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 70, No. 9, pp. 3318-3322, Sep. 2023.

[https://doi.org/10.1109/TCSII.2023.3268798]

-

S. S. Mohan, M. Hershenson, and S. P. Boyd, "Bandwidth extension in CMOS with optimized on-chip inductors", IEEE Journal of Solid-State Circuits, Vol. 35, No. 3, pp. 346-355, Mar. 2000.

[https://doi.org/10.1109/4.826816]

-

A. Niknejad, "Electromagnetics for High-Speed Analog and Digital Communication Circuits", Cambridge University Press, pp. 295-296, Mar. 2007.

[https://doi.org/10.1017/CBO9780511805738]

-

W. Lv, Z. Duan, and S. Wu, "A 68–79 GHz 15.6dBm Power Amplifier in 65nm CMOS", APMC, Kyoto, Japan, pp. 1522-1524, Nov. 2018.

[https://doi.org/10.23919/APMC.2018.8617633]

-

X. Li, D. Cheng, and X. Jiang, "A 57-71-GHz Accurate dB-Linear Variable Gain Power Amplifier with Ultralow Gain Error Using Particle Swarm Optimization Algorithm", 2024 IEEE/MTT-S International Microwave Symposium, Washington, DC, USA, pp. 454-457, Jun. 2024.

[https://doi.org/10.1109/IMS40175.2024.10600450]

2024년 2월 : 동아대학교 전자공학과(공학사)

2024년 3월 ~ 현재 : 동아대학교 ICT 융합해양스마트시티공학과 석사과정

관심분야 : CMOS RF/Analog 집적회로, 밀리미터-웨이브 대역 회로 설계

2003년 2월 : KAIST 전자전기공학부 (공학석사)

2006년 2월 : KAIST 전자전기공학부 (공학박사)

2007년 3월 ~ 현재 : 동아대학교 전자공학과 교수

관심분야 : CMOS RF/Analog 집적회로, 밀리미터-웨이브 대역 회로 설계