재구성 가능한 모듈 기반 CNN 가속기 구현

초록

본 논문에서는 CNN(Convolutional Neural Network)을 구성하는 주요 연산 모듈을 모듈 제어 명령어를 통해 구동함으로써 네트워크를 구현할 수 있는 CNN 가속기를 제안한다. 모듈 기반 CNN 가속기는 합성곱(Convolution), 풀링(Pooling) 등 CNN의 주요 연산 모듈로 구성되어 있으며, 프로세서에서 모듈 제어 명령어를 통해 네트워크 구성에 필요한 연산 모듈을 선택 및 내부 파라미터를 설정 할 수 있다. 본 논문에서 제안하는 모듈 기반 CNN 가속기를 사용하여 Xilinx SoC형 FPGA에 ResNet-18을 구현하였으며 CNN 프레임워크 모델인 PyTorch와 C 기반 검증 모델을 사용하여 출력 결과를 비교 검증하였다. 실험결과, CNN 가속기의 추론 결과는 92.87%의 정확도를 보였다.

Abstract

In this paper, we propose a CNN(convolution neural network) accelerator that can implement a network by driving main computation modules constituting the CNN through module control commands. The module-based CNN accelerator consists of CNN's main computation modules such as convolution and pooling, and the processor can select the computation module required for network configuration and set internal parameters through module control commands. In this paper, ResNet-18 was implemented on a Xilinx SoC-type FPGA using the proposed module-based CNN accelerator, and the output results were compared and verified using PyTorch, a CNN framework model, and a C-based verification model. As a result of the experiment, the inference result of the CNN accelerator showed an accuracy of 92.87%.

Keywords:

CNN accelerator, module-based architecture, FPGA, Verilog-HDLⅠ. 서 론

최근 단말 단에서 지능형 동작을 구현하기 위해 엣지(Edge) AI 가속기에 대한 연구가 활발히 이루어지고 있다[1][2]. 엣지 AI의 경우 클라우드 기반 AI 시스템에 비해 성능에 제한이 있으나 네트워크 지연시간 등을 감소시킬 수 있는 장점이 있다[3]. 엣지 AI 시스템을 구현하기 위해서는 전력, 하드웨어 크기 및 메모리 효율성 등이 고려되어야 하며, 이를 위해 하드웨어 자원 최소화 및 연산 속도 향상 등을 위한 연구가 이루어지고 있다[4].

엣지 AI 시스템을 구현하기 위한 디바이스 중 SoC형 FPGA는 CPU와 FPGA가 결합된 디바이스이다. SoC형 FPGA의 경우 하드웨어/소프트웨어 통합 설계를 통해 성능과 에너지 효율성을 향상시킬 수 있는 장점이 있다[5].

SoC형 FPGA를 활용한 CNN 가속기의 경우 HLS(High-Level Synthesis) 기법을 적용하여 CNN 가속기를 구현한 연구가 있다[6]-[8]. HLS의 경우 C 및 C++ 언어를 사용하여 알고리즘을 하드웨어로 합성 가능하나 회로 설계 및 하드웨어 최적화 측면에서는 Verilog-HDL(Hardware Description Language) 대비 엣지 AI 시스템 구현에 부적합하다[9].

이에 본 논문에서는 Verilog-HDL을 사용하여 CNN의 주요 연산 모듈을 설계하였으며, 명령어를 통해 CNN의 주요 연산 모듈을 선택 및 내부 파라미터를 설정함으로써 네트워크 구현이 가능한 모듈 기반 CNN 가속기를 제안하고 이를 SoC형 FPGA에 구현한 결과를 제시한다. 제안하는 가속기의 구현 및 검증을 위해 선행 연구에서 제안한 가속기 구조와 연산 모듈 검증을 위한 C 기반 검증 모델을 사용하였다[10][11]. 또한, 연산 모듈의 데이터 손실 최소화 및 처리 시간 향상을 위해 양자화 기법(Quantization)[12]-[16]을 적용하여 메모리 크기 및 연산 시간을 단축시켰으며, ResNet-18[17] 네트워크를 사용한 모듈 기반 CNN 가속기의 설계 및 성능 평가 결과를 도출함으로써 기존 연구 내용을 확장하였다.

본 논문의 2장에서는 하드웨어 합성 프로그램 분석 및 모듈 기반 CNN 가속기 구조에 관한 선행 연구를 설명하며, 3장에서는 본 논문에서 제안하는 SoC형 FPGA 기반 CNN 가속기 구조 및 CNN 가속기 모듈 구조에 대해 설명한다. 이후 4장에서는 본 논문에서 제안하는 모듈 기반 CNN 가속기의 ResNet-18 네트워크 기준 추론 정확도 및 하드웨어 구현 결과를 제시한다. 5장에서는 본 논문의 결론과 향후 연구과제에 대해 논한다.

Ⅱ. 관련 연구

2.1 하드웨어 합성 기법

HLS기법을 적용한 CNN 가속기의 경우 C 및 C++ 언어를 사용하여 CNN 연산에 필요한 핵심 알고리즘을 하드웨어로 합성이 가능하여 개발 시간 단축 및 생산성 향상 등의 장점이 있다[18][19]. 하지만 C 및 C++언어를 사용할 경우 회로 설계 및 하드웨어 최적화 측면에서는 하드웨어 기술 언어인 Veilog-HDL 대비 엣지 AI 시스템 구현에 적합하지 않은 단점이 있다[20]. 이에 본 논문에서는 최적화된 엣지 AI 시스템 구현을 위해 Verilog-HDL을 사용하였으며, 명령어를 통해 CNN의 주요 연산 모듈을 선택 및 내부 파라미터를 설정함으로써 네트워크 구현이 가능한 모듈 기반 CNN 가속기를 제안한다.

2.2 모듈 기반 CNN 가속기 구조

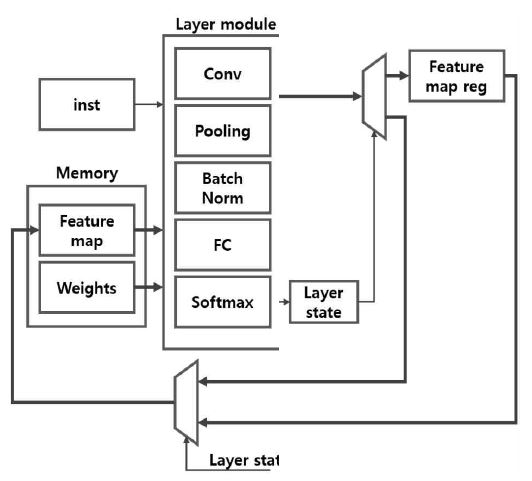

그림 1은 선행 연구에서 제안한 모듈 기반 CNN 가속기 구조이다. 연산 계층 모듈(Layer module)은 합성곱(Convolution), 풀링(Pooling), 배치 정규화(Batch normalization), 완전 연결(Fully-connected), 소프트맥스(Softmax)로 구성되며, 연산에 필요한 입출력 특징 맵 및 가중치 데이터는 내부 메모리를 활용한다. 가속기의 동작은 모듈 제어 명령어를 사용하여 CNN 연산 모듈 선택 신호 및 연산 모듈에 사용되는 내부 파라미터, 메모리 선택 등을 수행함으로써 네트워크를 구현할 수 있다.

Ⅲ. 제안하는 모듈 기반 CNN 가속기

3.1 SoC형 FPGA 기반 CNN 가속기 구조

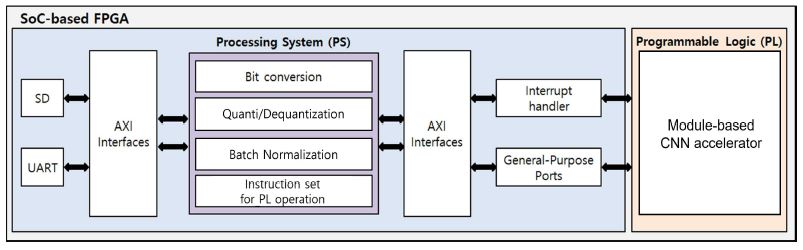

그림 2는 제안하는 SoC형 FPGA 기반 CNN 가속기 구조이다. 모듈 기반 CNN 가속기는 Xilinx사의 SoC형 FPGA인 ZC706을 사용하여 구현하였으며, PS(Processing System), PL(Programmable Logic) 영역으로 구분된다. PS 영역에서는 AXI(Advanced eXtensible Interface) 버스 인터페이스를 통해 외부 메모리(SD)에 저장되어 있는 정규화된 입력 이미지 데이터를 전송받는다. 전송받은 데이터는 비트 연산을 위해 소수점 데이터를 16진수 데이터로 비트 변환(Bit conversion)을 수행하며, 연산 모듈의 입력으로 사용하기 위해 양자화 기법을 적용하여 8비트 정수형 데이터로 비트 변환을 수행한다. 이후, PS에서는 PL 영역의 연산 모듈 동작을 위해 모듈 제어 명령어를 사용하여 네트워크 구성에 필요한 연산 모듈 선택 및 내부 파라미터를 설정하고 AXI 버스 인터페이스를 통해 생성된 명령어를 PL로 전달한다. 또한, AXI 버스 인터페이스를 통해 핵심 연산 모듈에 필요한 데이터를 전송하며, 이때 전송 비트는 입력 8비트, 출력 18비트이며, 전송 크기는 ResNet-18 구현을 위해 필요한 입출력 크기에 비례한다.

표 1은 ResNet-18 계층 별 출력 크기 및 가중치, 채널 등의 파라미터 값을 나타낸다. 표 2는 PS/PL 영역 간의 데이터 전송량을 나타내며, 입출력 및 가중치의 크기와 비트 수의 곱연산을 수행한 결과값을 나타낸다.

PL 영역에서는 주요 커널 단위 합성곱, 완전 연결 계층, 풀링, 활성화 함수 등의 주요 연산 모듈과 연산에 필요한 데이터를 저장하기 위한 메모리로 구성되어 있다. 배치 정규화의 경우 학습에 의해 고정된 평균, 분산값을 사용하여 데이터 정규화를 수행하므로 PS 영역에서 수행하도록 변경함으로써 추론 성능 저하를 최소화하였다. 주요 연산 모듈의 출력 결과는 인터럽트(Interrupt) 신호를 통해 PS 영역에서 확인이 가능하며, AXI 버스 인터페이스를 통해 출력 결과를 PS 영역으로 전송한다. 전송된 데이터는 PS 영역에서 UART 통신을 이용하여 PC에서 모니터링이 가능하다.

PS에서 생성하는 모듈 제어 명령어는 PL내부 CNN 연산 모듈의 동작 신호 및 매개변수를 제어하며 표 3과 같이 구성된다. Module Enable은 주요 연산 모듈의 동작을 제어하기 위한 신호이며, 각 비트 별로 주요 연산 모듈의 동작을 제어한다.

연산 모듈의 동작 종료 시 인터럽트 신호를 AXI 버스 인터페이스를 통해 PS 영역으로 전달한다. 연산 처리에 사용되는 입력은 Input Feature Size, Input Feature Channel, Kernel Configuration 명령어를 통해 연산 모듈의 입력 파라미터를 제어할 수 있다. Memory Selector는 입력 특징맵, 가중치, 바이어스, 출력 특징맵 데이터의 메모리 저장 공간 선택 명령을 받아 연산을 수행하며, 특징맵의 크기와 매개변수에 따라 연산할 수 있도록 설계되었다.

본 논문에서는 제한된 메모리를 가지는 임베디드 환경에서 특징맵(Feature map)을 저장하는 메모리와 연산량을 줄일 수 있는 CNN을 구현하기 위해 양자화 기법을 사용한다. 양자화 기법은 CNN에서 사용하는 부동 소수점 데이터를 낮은 대역폭의 근사값을 가지는 데이터로 치환하는 방법으로써 이 중 부동 소수점 범위의 최소/최대를 정수 범위의 최소/최대로 매핑하는 대칭 양자화 기법(Symmetric quantization)을 사용한다. INT8(integer-8bit)로 양자화된 결과(yq)는 FP32(floating point-32bit) 결과값(yf)과 양자화 스케일 팩터(Scale factor)(qy)의 곱으로 이루어진다. 메모리 사용 효율을 높이기 위해서는 양자화된 입력(xq), 가중치(wq), 바이어스(bq)와 각각의 스케일 팩터(qx, qw, qb)를 이용하여 출력값을 얻는다. 스케일 팩터는 표현하고자 하는 비트 수와 FP32 입력값(xf,wf,bf)으로 정해진다.

| (1) |

양자화 데이터는 FP32 데이터와 스케일 팩터의 곱에 반올림을 수행한 값이며, 이를 통해 양자화된 입력과 가중치 값을 얻을 수 있다. 위의 과정을 통해 얻은 양자화 데이터의 MAC(Multiply and ACcumulation) 연산으로 양자화된 INT8 결과값이 연산된다.

| (2) |

| (3) |

| (4) |

| (5) |

| (6) |

| (7) |

3.2 CNN 가속기 모듈 구조

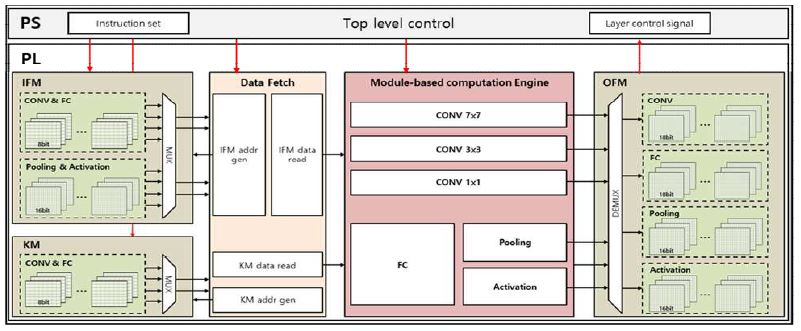

PL 영역에서 구현된 모듈 기반 CNN 가속기 모듈 구조는 그림 3과 같으며, 데이터 접근을 빠르게 수행하기 위해 내부 데이터 캐싱을 처리하는 IFM(Input Feature Memory), KM(Kernel Memory), OFM(Output Feature Memory)으로 구성된 메모리 시스템, Data Fetch, 그리고 연산을 위한 모듈 기반 CNN 연산기(Module-based CNN calculator)로 구성되어 있다.

모듈 기반 CNN 가속기의 메모리 시스템은 세 가지의 BRAM으로 구성되어 있다. IFM은 AXI 버스 인터페이스를 통해 외부 메모리로부터 CNN 연산에 필요한 입력 데이터를 저장할 수 있는 레지스터이다. 풀링과 활성화 함수의 결과는 FP32를 사용하는 CNN 데이터의 크기를 줄이기 위해 고정 소수점(Fixed-point) 16비트를 사용하였으며 대역폭 감소로 인한 소수점 데이터 손실을 최소화하기 위해 부호 1비트, 지수 5비트, 가수 10비트의 데이터가 IFM에 저장된다. 합성곱 및 완전 연결 계층의 경우 FP32를 양자화한 INT8 데이터가 저장된다. KM은 AXI 버스 인터페이스를 통해 외부 메모리로부터 합성곱과 완전 연결 계층 연산을 위한 가중치(Weight)를 저장할 수 있는 레지스터이다. KM의 데이터는 합성곱과 완전 연결 계층 연산에서 사용되며 입력 데이터와 동일한 비트의 양자화한 데이터가 저장된다. OFM은 CNN 연산 모듈의 출력 결과를 저장할 수 있는 레지스터이다. 합성곱과 완전 연결 계층 연산 결과는 INT8로 이루어진 특징맵과 가중치의 MAC 연산 결과를 저장하기 위해 18비트를 사용하였으며, 그 외 모듈은 고정 소수점 16비트를 사용하였다. 연산 모듈의 중간 연산 결과는 모두 내부 메모리에 저장되며 연산 모듈 간의 직접적인 인터페이스로 빠른 데이터 접근 및 연산 처리가 가능하다.

본 논문에서 제안하는 모듈 기반 CNN 가속기는 커널 단위 합성곱, 완전 연결 계층, 풀링, 활성화 함수 연산 모듈이다.

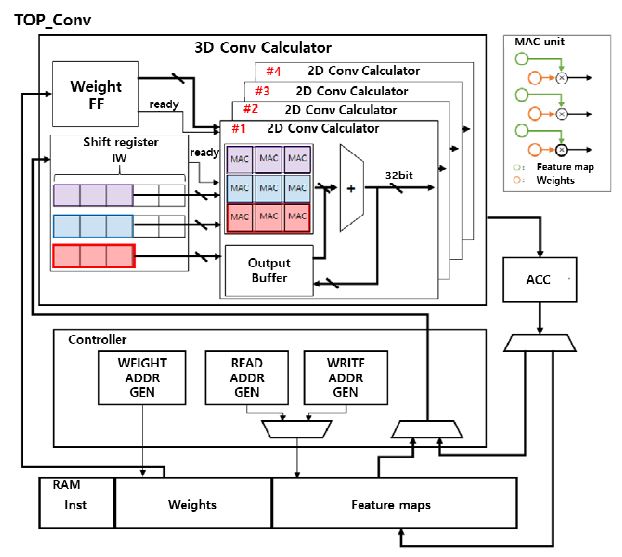

합성곱 연산 모듈은 그림 4와 같이 3D 합성곱 연산기, 제어기, 누산기로 구성된다. 3D 합성곱 연산기는 가중치 플리플롭(Flip-flop)과 시프트 레지스터, 2D 합성곱 연산기로 이루어져 있다. 2D 합성곱 연산기는 시프트 레지스터를 통해 특징맵을 얻고 가중치 플리플롭을 통해 4개의 채널 출력을 위한 가중치를 입력받는다. 2D 합성곱 연산의 결과는 누적 연산을 반복적으로 수행함으로써 3D 연산을 수행하며, 최종 출력 결과는 메모리에 저장한다.

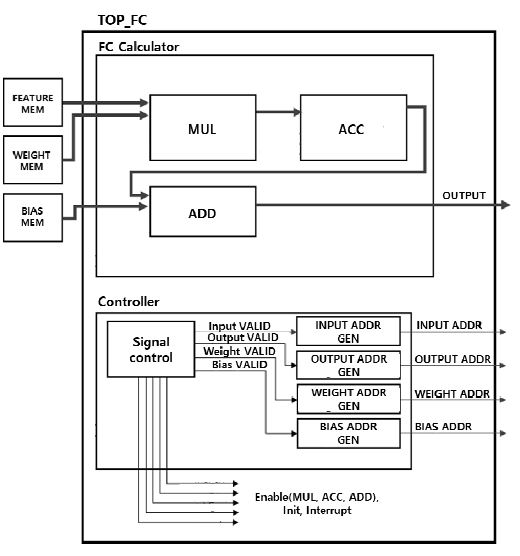

완전 연결 계층 연산 모듈은 그림 5와 같이 곱셈기 및 누산기를 사용하여 합성곱과 유사한 연산을 수행하며, 가산기를 사용하여 편향(Bias) 연산을 수행한다. 특징맵과 가중치는 클럭마다 메모리로부터 로드(Load) 되어 곱셈 및 누적 연산을 수행된다. 연산이 완료된 결과와 편향 데이터는 가산기를 통해 더해지며 이후 누산기는 제어기의 초기화 신호를 통해 초기화된다. 편향 데이터를 더한 연산 결과는 메모리에 저장하며 각 연산 모듈은 FSM(Finite State Machine)으로 이루어진 제어 신호를 통해 순차적으로 동작한다.

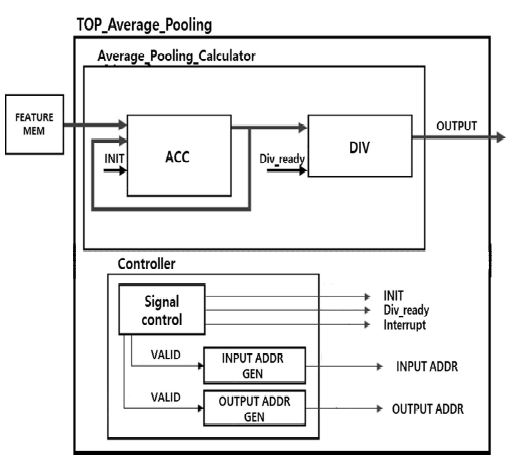

풀링 연산 모듈은 그림 6과 같이 7×7 커널을 가지는 평균 풀링 연산기로 설계하였으며, 평균값 연산을 위해 클럭마다 메모리에서 데이터를 로드하여 누산 과정을 수행한다.

이후 제어기의 초기화 신호(Init)를 통해 초기화 동작을 수행하며, 출력 결과는 나눗셈기 동작 신호(div_ready)를 입력받아 평균 연산을 수행하여 최종 결과를 출력한다.

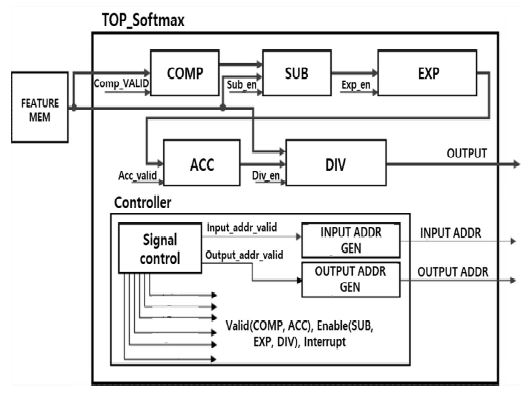

활성화 함수 연산 모듈로써 소프트맥스(Softmax)를 설계하였으며, 이를 통해 모듈로 입력 데이터를 0~1사이의 값으로 모두 정규화함으로써 클래스의 확률값을 출력할 수 있다.

활성화 함수 연산 모듈은 소프트맥스 연산에서 필요한 지수 연산을 하드웨어에서 가산기와 시프트를 이용하여 설계하였으며, 다음과 같은 수식을 통해 구현할 수 있다[21]. 즉, ‘exp(4)=1’이라는 조건을 주었을 경우, 입력 x에서 임의의 상수 k를 뺀 값은 수식 (8)-(10)과 같이 표현할 수 있다.

| (8) |

| (9) |

| (10) |

입력 x에서 임의의 상수 k를 뺀 값은 y와 exp(k)의 역수를 곱하는 것으로 표현 가능하며, k를 소수점으로 표현하여 지수연산을 정수로 연산할 수 있다. 이를 기반으로 설계한 소프트맥스 연산 모듈 구조는 그림 7과 같다.

Ⅳ. 모듈 기반 CNN 가속기 구현 및 검증

4.1 실험 환경 및 방법

본 논문에서 제안하는 모듈 기반 CNN 가속기는 Xilinx 사의 SoC형 FPGA ZC706을 사용하였으며, HDL 합성 프로그램 Vivado를 통해 CNN 연산 모듈을 구현하였다. 제안하는 모듈 기반 CNN 가속기는 ResNet-18 네트워크를 사용하여 연산 모듈에 대한 검증을 수행하였으며, 얼굴 데이터 세트인 VGG Face와 LFW(Labeled Faces in the Wild) 데이터 세트[22]를 이용하여 추론 정확도 성능을 측정하였다. 측정된 결과는 딥러닝 프레임워크인 MXNet 및 C 기반 검증 모델의 추론 결과와 비교함으로써 성능을 평가하였다.

4.2 연산 모듈 검증 모델

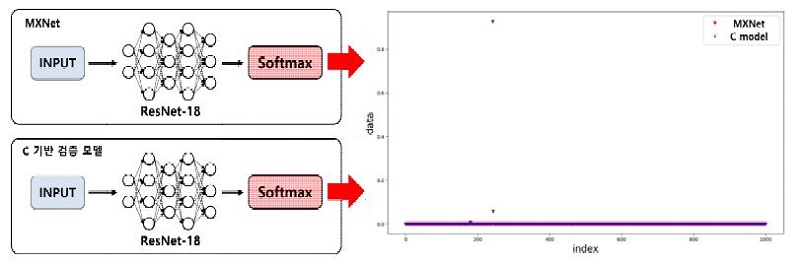

모듈 기반 CNN 가속기의 경우 비트 단위로 설계된 주요 연산 모듈의 출력 결과와 네트워크 계층별 연산 결과의 정확성에 대한 검증이 필요하다. 기존의 MXNet 및 PyTorch 등의 레퍼런스 모델에서는 CNN의 최종 추론 결과만 추출이 가능하고 중간 연산 결과는 추출이 불가능하여 모듈 기반 CNN 가속기 검증에 어려움이 있다.

C 기반 검증 모델의 경우 C언어를 사용하여 모듈 기반 CNN 가속기의 연산 모듈을 채널 단위로 구현하였으며, 이를 통해 CNN의 모듈 단위 연산 결과뿐만 아니라 채널 단위의 내부 연산 결과를 출력하여 비교 검증이 가능하도록 구현함으로써 주요 연산 모듈 검증에 용이한 검증용 모델을 구현하였다. 또한, C언어로 구현한 연산 모듈을 연결하여 ResNet-18 네트워크를 구현하였으며, 그림 8과 같이 MXNet 및 PyTorch 등의 레퍼런스 모델과 CNN 계층 별 중간 연산 결과 및 최종 추론 결과를 비교 검증하여 정상 동작함을 확인하였다.

4.3 실험 결과 및 성능 평가

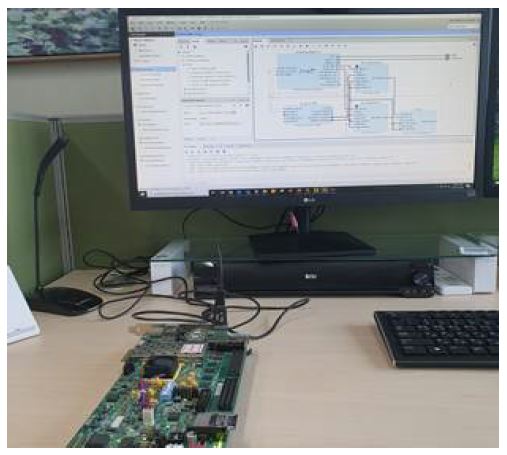

표 3은 HDL 합성 프로그램을 통해 타겟 보드에 구현한 CNN 연산 모듈과 이를 검증하기 위한 C 기반 검증 모델과의 출력 오차를 비교 검증한 결과이고, 그림 9는 FPGA 기반 구현 환경이다. 성능 비교 평가를 수행한 연산 모듈은 합성곱, 완전 연결 계층, 평균 풀링, 활성화 함수 모듈이다.

본 논문에서 구현한 연산 모듈의 정확성에 대한 검증을 수행하기 위해 동일한 파라미터를 적용하고, 이에 따른 모듈별 출력에 대한 평균값을 측정하였다.

또한, 연산 모듈과 C 기반 검증 모델 간의 오차율을 비교 검증하였으며 성능 비교 평가 결과 본 논문에서 제안하는 연산 모듈은 평균 98.2%의 정확도를 보였다.

연산 모듈 중 활성화 함수 모듈의 경우 MAC 연산을 수행하지 않아 양자화 기법이 적용되지 않아 고정 소수점 16비트 사용하였으며, 하드웨어에서 지수 연산을 수행하기 위해 식 (8)-(10)과 같이 정수 연산으로 변환하는 방식을 사용함으로써 정확도의 차이를 보였다.

표 4는 제안하는 모듈 기반 CNN 가속기의 연산 모듈 별 사용량 및 처리 시간이다.

ResNet-18 네트워크를 포함한 대부분의 CNN은 구현한 주요 연산 모듈을 반복적으로 사용하며, 이를 순차적으로 연결한 구조이므로 사용되는 연산 모듈 개수 및 처리 시간을 통해 ResNet-18 네트워크에 사용되는 주요 연산 모듈의 총 처리 시간을 나타낼 수 있다. 이를 위해 연산 모듈의 사이클 타임을 측정한 후 한 클럭 당 200MHz 기준 처리 시간을 측정하였으며, ResNet-18 네트워크 기준 연산 모듈 사용 개수를 종합한 결과 약 0.175 sec의 연산속도를 가진다.

표 5는 제안하는 모듈 기반 CNN 가속기의 하드웨어 자원량을 나타내며, 타겟 보드인 ZC706에서 구현 가능함을 보였다.

본 논문에서는 CNN 연산 모듈을 연결하여 ResNet-18을 구현하고 얼굴 데이터 세트인 VGG Face와 LFW 데이터 세트를 사용하여 추론 결과에 대한 정확도 검증을 수행하였다.

표 6은 레퍼런스 CNN[23] 및 C 기반 검증 모델과 비교한 모듈 기반 CNN 가속기의 추론 정확도 결과이다.

본 논문에서 제안하는 모듈 기반 CNN 가속기는 92.87% 추론 정확도를 보였다. 모듈 기반 CNN 가속기는 엣지 AI 시스템의 제한된 하드웨어 자원에 맞게 구현하기 위해 입출력 비트를 압축함으로써 FP32 대비 약 3% 정도의 추론 정확도 차이가 있음을 보였다.

Ⅴ. 결 론

본 논문에서는 모듈 제어 명령어를 통해 CNN의 주요 연산 모듈을 선택 및 내부 파라미터를 설정함으로써 딥뉴럴 네트워크 구현이 가능한 모듈 기반 CNN 가속기를 제안하고 이를 SoC형 FPGA에 구현한 결과를 제시하였다. 제안하는 CNN 가속기의 연산 모듈은 합성곱, 풀링, 완전 연결 계층 및 활성화 함수이며, AXI 버스 인터페이스를 통해 각 모듈을 제어하도록 설계하였다. 또한, 양자화 기법을 사용함으로써 32비트 부동소수점으로 이루어진 특징맵 데이터를 8비트 정수형 데이터로 변환하여 임베디드 시스템 구현에 필요한 메모리 크기를 줄이고 정확도를 유지하였다.

연산 모듈의 검증을 위해 C 기반 검증 모델을 구현하였으며, 얼굴 데이터 세트인 VGG Face와 LFW 데이터 세트를 이용하여 모듈 기반 CNN 가속기의 추론 정확도 성능을 측정하였다. 본 논문에서 제안하는 연산 모듈의 경우 C 기반 검증 모델 대비 98.2%의 정확도를 보였으며, ResNet-18 추론 정확도 측정 결과 92.87%의 정확도를 보였다.

향후, 제안하는 모듈 기반 CNN 가속기는 MPW(Multi-Project Wafer)를 통해 ASIC 개발을 진행할 예정이며, ARM DesignStart[24]를 활용하여 Cortex-M0 기반 SoC 개발에 대한 연구를 진행 예정이다.

Acknowledgments

본 연구는 2022년도 정부(산업통산자원부)의 재원으로 한국연구재단-실종아동 등 신원확인을 위한 복합인지기술개발사업의 지원을 받아 수행된 연구임” (2018M3E3A1057248) “본 연구는 IDEC에서 EDA Tool를 지원받아 수행하였습니다.

References

-

F. Samie, L. Bauer, and J. Henkel, "From Cloud Down to Things: An Overview of Machine Learning in Internet of Things", in IEEE Internet of Things Journal, Vol. 6, No. 3, pp. 4921-4934, Jun. 2019.

[https://doi.org/10.1109/JIOT.2019.2893866]

- Y. Kwon and S. Kim, "Trend Analysis of IoT Technology Using Open Source", The Journal of IIBC, Vol. 20, No. 3, pp. 65-72, Jun. 2020.

- https://signalm.sedaily.com/ReportView/3028, , [accessed: Oct. 20, 2020]

-

D. Moolchandani, A. Kumar, and S. R. Sarangi, "Accelerating CNN inference on ASICs: A survey", Journal of Systems Architecture, Vol. 113, 101887, Feb. 2021.

[https://doi.org/10.1016/j.sysarc.2020.101887]

-

A. D. George and C. M. Wilson, "Onboard processing withhybrid and reconfigurable computing on small satellites", Proceedings of the IEEE, Vol. 106, No. 3, pp. 458-470, Mar. 2018.

[https://doi.org/10.1109/JPROC.2018.2802438]

- Y. Zhou and J. Jiang, "An FPGA-based accelerator implementation for deep convolutional neural networks", 2015 4th International Conference on Computer Science and Network Technology (ICCSNT), Harbin, China, Vol. 1, pp. 829-832, Dec. 2015.

-

S. Sabogal, A. George, and G. Crum, "ReCoN: A Reconfigurable CNN Acceleration Framework for Hybrid Semantic Segmentation on Hybrid SoCs for Space Applications", 2019 IEEE Space Computing Conference (SCC), Pasadena, CA, USA, pp. 41-52, Aug. 2019.

[https://doi.org/10.1109/SpaceComp.2019.00010]

-

H. Nakahara, Z. Que, and W. Luk, "High-Throughput Convolutional Neural Network on an FPGA by Customized JPEG Compression", 2020 IEEE 28th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), Fayetteville, AR, USA, pp. 1-9, May 2020.

[https://doi.org/10.1109/FCCM48280.2020.00010]

-

R. Millon, E. Frati, and E. Rucci, "A Comparative Study between HLS and HDL on SoC for Image Processing Applications", arXiv:2012.08320, [cs.AR], Dec. 2020.

[https://doi.org/10.37537/rev.elektron.4.2.117.2020]

- H. Lee, S. Lee, S. Jeon, and S. Ok, "A FPGA-based Reconfigurable CNN Accelerator", 2020 Conference on Korean Institute of Information Technology, Cheongju Korea, pp. 47-48, Oct. 2020.

- S. Jeon and S. Ok, "A C-based Verification Model for FPGA-based CNN Accelerators", 2020 Conference on Korean Institute of Information Technology, Cheongju Korea, pp. 528-530, Oct. 2020.

-

J. Choi, B. Y. Kong, and I. Park, "Retrain-less Weight Quantization for Multiplier-less Convolutional Neural Networks", in IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 67, No. 3, pp. 972-982, Mar. 2020.

[https://doi.org/10.1109/TCSI.2019.2949935]

-

S. Seo and J. Kim, "Efficient Weights Quantization of Convolutional Neural Networks Using Kernel Density Estimation based Non-uniform Quantizer", Proc. Applied Sciences, Vol. 9, No. 12, 2559, Jun. 2019.

[https://doi.org/10.3390/app9122559]

- R. Solovyev, A. Kustov, D. Telpukhov, V. Rukhlov, and A. Kalinin, "FPGA Implementation of Convolutional Neural Networks with Fixed-Point Calculations", arXiv:1808.09945, [cs.CV], Aug. 2018.

-

Y. Wu and C. T. Huang, "Efficient Dynamic Fixed-Point Quantization of CNN Inference Accelerators for Edge Devices", 2019 International Symposium on VLSI Design, Automation and Test, Hsinchu, Taiwan, pp. 1-4, Apr. 2019.

[https://doi.org/10.1109/VLSI-DAT.2019.8742040]

- D. Chang, J. Lee, and J. Heo, "Lightweight of ONNX using Quantization-based Model Compression", The Journal of IIBC, Vol. 21, No. 1, pp. 93-98, Feb. 2021.

-

K. He et al., "Deep residual learning for image recognition", IEEE Conf. on Computer Vision and Pattern Recognition (CVPR), Las Vegas, NV, USA, pp. 770-778, Jun. 2016.

[https://doi.org/10.1109/CVPR.2016.90]

-

G. Martin and G. Smith, "High-level synthesis: Past, present, and future", IEEE Design & Test of Computers, Vol. 26, No. 4, pp. 18-25, Aug. 2009.

[https://doi.org/10.1109/MDT.2009.83]

-

R. Nane, V. M. Sima, C. Pilato, J. Choi, B. Fort, A. Canis, Y. T. Chen, H. Hsiao, S. Brown, F. Ferrandi, J. Anderson, and K. Bertels, "A survey and evaluation of FPGA high-level synthesis tools", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 35, No. 10, pp. 1591-1604, Dec. 2016.

[https://doi.org/10.1109/TCAD.2015.2513673]

-

H. Ren, "A brief introduction on contemporary High-Level Synthesis", in 2014 IEEE International Conference on IC Design & Technology, Austin, TX, USA, Vol. 4, No. 2, pp. 100-106, May 2014.

[https://doi.org/10.1109/ICICDT.2014.6838614]

- J. Sujitha and V. R. Reddy, "Implementation of Log and Exponential Functionin FPGA", Proc. International Journal of Engineering Research & Technology, Vol. 3, No. 11, pp. 1404-1407, Nov. 2014.

- http://vis-www.cs.umass.edu/lfw/, [accessed: Oct. 29. 2019]

-

Y. Wan, M. X. Zhang, Y. A. Zhang, and L. Yao, "Research on Unconstrained Face Recognition Based on Deep Learning", 2020 International Conference on Big Data & Artificial Intelligence & Software Engineering (ICBASE), Bangkok, Thailand, pp. 219-227, Nov. 2020.

[https://doi.org/10.1109/ICBASE51474.2020.00054]

- https://www.arm.com/resources/designstart/, [accessed: Oct. 29. 2019]

2019년 2월 : 동의대학교 메카트로닉스공학과(공학학사)

2021년 2월 : 동의대학교 지능시스템공학과(공학석사)

2021년 3월 ~ 현재 : ㈜아진엑스텍 연구원

관심분야 : FPGA, NPU, Embedded System, 머신비전

2021년 2월 : 동의대학교 로봇·자동화공학전공(공학사)

2021년 3월 ~ 현재 : 동의대학교 인공지능학과(석사과정)

관심분야 : On-device AI, FPGA, NPU, Edge AI-System

2008년 2월 : 경북대학교 전자공학과(공학석사)

2014년 2월 : 경북대학교 전자공학부(공학박사)

2014년 3월 ~ 2017년 8월 : 삼성전자 책임연구원

2017년 9월 ~ 현재 : 동의대학교 로봇·자동화공학전공 조교수

관심분야 : 로봇비전, SoC, VLSI