양자 회로 동작 검증을 위한 QCA 룩업 테이블과 QRAM을 이용한 유효성 확인

초록

양자점 셀룰러 오토마타(QCA, Quantum-dot Cellular Automata)는 크기, 전력 소모, 그리고 정보 전달 속도에서 주목받고 있는 차세대 양자 회로 기술이다. QCA로 설계된 회로들을 검증하는 방법으로는 물리적 증명 방법이 있다. 물리적 증명 방법은 시뮬레이션 환경 외에서도 QCA 회로를 검증할 수 있다는 장점이 있지만, 연산이 많이 필요하다는 단점이 있다. 이에 본 논문에서는 QCA 룩업 테이블(QLUT, QCA Look-Up Table)을 사용하여 회로를 검증하는 방법을 제안한다. QLUT를 이용한 검증은 입력에 따른 출력 값이 무엇이 나오는지를 미리 표의 형식으로 만들어 이를 활용하는 방법이다. 해당 방법을 사용함으로써 기존의 물리적 증명의 복잡한 연산을 수행할 필요 없이 더욱 간결하게 회로를 검증할 수 있다. 본 논문에서는 QLUT 기반 검증으로 QRAM(Quantum RAM)의 동작을 검증하고, 기존의 물리적 증명과 QLUT 방식을 비교 분석한다.

Abstract

Quantum-dot cellular automata (QCA) is a next-generation quantum circuit technology that is attracting attention for its size, power consumption, and speed of information transfer. A method of verifying circuits designed with QCA is a physical proof method. The physical proof method has the advantage of being able to verify the QCA circuit outside the simulation environment, but has the disadvantage that it requires a lot of computation. Therefore, this paper proposes a method for verifying a circuit using a QCA look-up table (QLUT). Verification using QLUT is a method of making an output value according to an input in a tabular format in advance. By using this method, it is possible to verify the circuit more concisely without having to perform a complicated operation of the existing physical proof. In this paper, the operation of QRAM (Quantum RAM) is verified by QLUT-based verification, and the existing physical proof and QLUT method are compared and analyzed.

Keywords:

QCA lookup table, nanotechnology, quantum dot cellular automata, QRAM, cell interactionⅠ. 서 론

기존 CMOS 소자는 다양한 디지털 회로를 구성하는 소자이며[1], 계속해서 회로의 크기를 줄이는 방식으로 성능을 향상시켜왔다. 그러나 CMOS 소자가 다양한 면에서 한계에 도달함에 따라 CMOS 기술을 대체할 새로운 기술이 요구된다[2]. 이런 요구에 부응하는 기술인 양자점 셀룰러 오토마타(QCA, Quantum-dot Cellular Automata)는 전력 소모, 발열, 정보 전달 속도 그리고 크기 등에서 기존의 디지털 소자와 비교했을 때 높은 성능을 보여 기존의 디지털 회로를 대체할 기술로 주목받고 있다. QCA 환경 상에서 디코더[3], 가산기[4]-[7], 비교기[8][9], 인코더[10], T 플립플롭[11], 유니버설 시프트 레지스터[12], RAM[13] 그리고 이 외에도 다양한 회로들[14]-[16]이 제안되었다.

제안된 회로들을 검증하는 방법으로는 크게 QCA Designer[17]와 같은 시뮬레이션 도구를 활용하는 방법과 시뮬레이션을 사용하지 않는 물리적 증명 방법[16]이 있다. 둘 중에서 물리적 증명 방법은 검증할 셀 내부의 전자들이 인접한 셀의 전자들과 상호작용하며 가지게 되는 퍼텐셜 에너지를 계산하고 각 편극 상태마다 퍼텐셜 에너지의 총합을 구해서 더 낮은 퍼텐셜 에너지의 편극 상태를 셀이 가진다는 결과를 이용해서 검증하는 방법이다[16].

제안하는 QCA 룩업 테이블(QLUT, QCA Look-Up Table) 기반 검증은 일련의 입력 셀들에 대해서 출력 셀의 값을 시뮬레이션을 통해 알아내 이를 표로 만들어, 실제 회로의 검증에서 입력 셀과 출력 셀의 배치가 일치하는 경우를 찾아서 회로 검증을 진행하는 방법이다. QLUT 기반 검증 방식으로 회로를 검증하게 되면 기존의 물리적 증명 방식과는 달리 많은 연산을 요구하지 않는다는 장점이 있다.

QLUT 기반 검증을 사용함으로써 QCA 회로를 검증하는 과정의 복잡함이 기존 방법과 비교했을 때 대폭 줄어들 것이며, 이는 차후에 대규모 QCA 회로를 설계하거나, 셀 간 상호작용을 이용하는 QCA 회로를 설계할 때 회로의 동작을 검증해보는 유용한 방법이 될 수 있을 것이다. 본 논문에서는 QLUT 기반 검증에 대해서 설명하고, 이를 이용하여 QRAM(Quantum Random Access Memory) 중 하나의 동작을 검증하도록 한다.

회로를 검증한 결과 QLUT 방식이 기존의 물리적 증명보다 연산량이 더 적고, 표와 비교하는 식으로 검증을 진행하기 때문에 속도가 빠르다. 또한, 정확성 역시 시뮬레이션 결과를 바탕으로 제작된 표를 이용해서 검증하기 때문에 높은 것을 확인하였다. QLUT 방식은 차후 대규모 회로를 검증하는 속도를 한층 더 빠르게 만들어 줄 것이다.

Ⅱ. 관련 연구

2.1 QCA 기본 소자

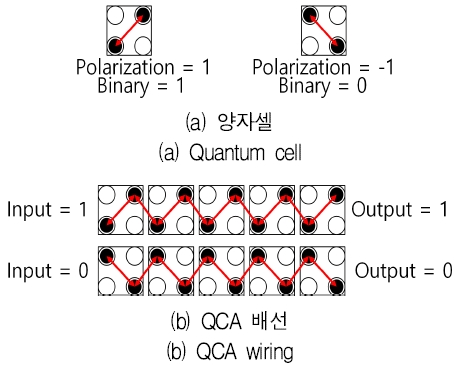

QCA는 양자 셀을 기본 소자로 가진다. 양자 셀은 네 개의 양자점과 두 개의 유동 전자로 구성되어 있으며, 유동 전자는 전자끼리 서로 밀어내는 힘으로 인해 셀 내부에서 서로로부터 가장 멀리 떨어진 상태로 배치된다. 내부 유동 전자의 배치에 따라서 이진 정보 1과 0을 설정할 수 있다. 이진 정보 1일 때의 편극을 +1이라고 하며, 이진 정보 0일 때의 편극을 –1이라고 한다[3]. 또한, 양자셀들을 이어서 신호를 전달하는 배선을 만들 수 있다. 배선의 신호 전달은 인접한 셀의 전자들과 셀 내부의 전자가 서로 밀어내는 힘에 영향을 받아서 신호가 결정되는 방식으로 전달되게 된다. QCA 셀은 그림 1(a)에 QCA 배선은 그림 1(b)에 나타나 있다[4].

2.2 기존의 물리적 증명

기존에 사용되고 있던 물리적 증명 방법[16]은 먼저 검증하고자 하는 셀을 선택한 뒤, 해당 셀 내부의 전자들이 인접한 셀의 전자들과 상호작용하며 가지는 퍼텐셜 에너지를 계산하고, 각 전자 배치 상태에 따라서 셀 내부의 두 전자의 퍼텐셜 에너지의 합을 계산한 뒤, 더 낮은 에너지 합을 가지는 상태를 결정짓는다. 물리적 증명을 하기에 앞서서 두 가지 가정이 필요하다.

1. 각 셀의 전자는 셀의 꼭짓점 부분에 중심점이 위치하는 것으로 한다.

2. 셀 간 거리는 2nm, 그리고 셀의 가로와 세로 길이는 18nm로 가정한다.

각 전자 간의 상호작용으로 인해서 전자가 가지는 퍼텐셜 에너지는 식 (1)을 사용해서 계산한다. U는 퍼텐셜 에너지, r은 두 전자 사이의 거리, k는 쿨롱 상수, q1과 q2는 각각 상호작용하는 두 전자의 전하량이다.

| (1) |

기존의 물리적 증명 방법은 시뮬레이션 환경 외에서도 QCA 회로를 검증할 수 있는 방법을 제공한다는 점에서 그 중요성이 높다. 그러나 검증을 하기 위해서 비교적 많은 연산을 해야 한다.

Ⅲ. QLUT 기반 검증과 적용 예

3.1 QLUT 기반 검증 방법

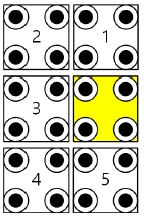

QLUT 기반 검증은 본 논문에서 제안하는 QCA 회로 검증 방법이다. QLUT 기반 검증은 먼저 각 입력 셀의 배치와 상태마다 출력 값을 시뮬레이션 한 뒤 이를 정리해놓은 표 1을 보고 검증을 진행한다.

이를 통해서 검증을 진행할 때 기존의 복잡한 연산을 수행하는 물리적 증명과는 달리 회로를 간단히 검증할 수 있다. 그림 2에서 색깔이 입혀진 셀은 출력셀로 검증을 진행하고자 하는 셀이다.

표 1에 그림 2와 같이 1번부터 5번까지의 입력값에 대한 출력 값을 표시하였다.

검증할 셀을 기준으로 상하로 뒤집거나, 회전시켜도 검증 결과는 변하지 않는다. 표 1의 상단의 열은 1부터 5까지, 출력셀을 중심으로 반 시계 방향으로 순서대로 번호를 매긴 것이다. 표 1의 행은 각 경우에 매겨진 번호이다. 표 1의 내부에서 출력을 제외한 내부의 값은 각 셀의 편극으로 표시하였고, 해당 셀이 존재하지 않을 때를 X로 표기하였다.

3.2 RAM 셀의 QLUT 기반 검증

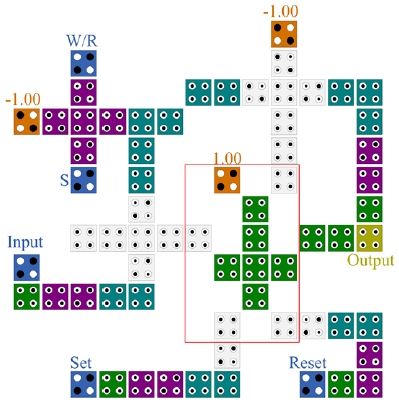

RAM 셀은 컴퓨터의 메모리를 구성하는 기본 단위 중 하나라는 점에서 그 중요성이 높다고 할 수 있다. 본 논문에서 검증할 RAM 셀은 [12]에서 제안된 QRAM 셀이며 그림 3에 나타나 있다. [13]에서 제안한 QRAM 셀은 5입력 다수결 게이트를 사용하여 설계되었다. 이 회로는 다른 논문들에서 제안된 QRAM 셀과 비교했을 때 셀 수, 면적, 그리고 지연시간 면에서 좋은 성능을 보인다.

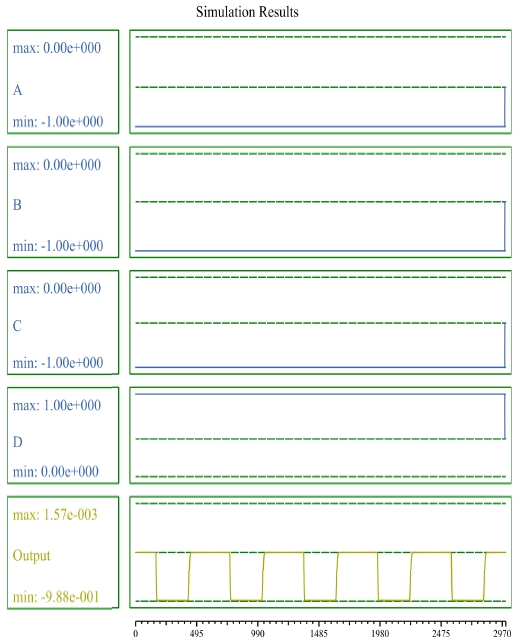

그림 3은 [13]에서 제안한 QRAM 셀의 시뮬레이션 결과이다. 진리표는 표 2에 나타나 있다. 본 논문에서는 그림 3에 네모 상자로 표시되어 있는 5입력 다수결 게이트에 대해서 검증을 진행하고자 한다. 해당 부분은 RAM 셀의 출력 부분을 결정하는 부분이라는 점에서 회로에서 중요한 부분이라고 판단할 수 있다.

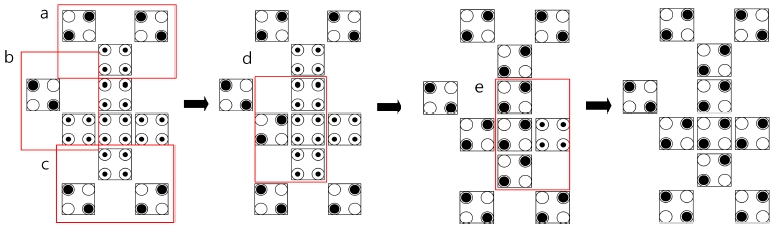

5입력 다수결 게이트의 검증을 진행하기 위해서 이전 출력값은 0, S는 1, W/R는 0, Input은 0, Set은 0, Reset은 1인 경우를 가정하였다. 이 경우에는 출력값이 0이 나와야 한다. 그러면 이제 순차적으로 을 진행해보도록 하자. 검증의 진행을 그림 4에 나타내었다. 그림 4에서 붉은색으로 표시된 부분은 각 단계에서 검증을 진행하는 부분이다.

그림 4의 검증 단계를 분석해보면 다음과 같다. 먼저 a라고 표시된 네모에 나타난 경우는 표 1에서 34번과 같은 경우이므로 검증하고자 하는 셀의 편극은 0이다. b의 경우는 표 1에서 37번과 같은 경우이므로 검증하는 셀의 편극은 1이 된다. c의 경우는 표 1에서 34번과 같은 경우이므로 검증하는 셀의 편극은 0이 된다.

그 후, d에서 신호가 남은 우측의 셀들에 전파된다. 이후 e는 표 1에서 28번과 같은 경우이므로 검증하는 셀의 편극은 1이 된다. 최종적으로 그림 3에서 보이듯이 출력부로 신호가 전파될 때, 표 1의 36번과 같은 경우이므로 출력값의 편극은 –1이 된다. 이는 시뮬레이션 결과인 그림 5와도 일치한다.

Ⅳ. 비교 분석

표 3은 기존의 물리적 증명 방식과 QLUT 기반 검증 방식을 비교해놓은 표이다. 표 3에서 보이듯이, QLUT 기반 검증 방식은 기존의 물리적 증명 방법 대비 검증에 필요한 연산량과 속도 역시 만들어진 표에서 검증하고자 하는 셀과 일치하는 경우를 찾기만 하면 되므로 기존의 물리적 증명보다 적고, 빠르다. 또한, 정확성 역시 시뮬레이션 결과로 만들어진 표와 비교하는 경우를 찾는 것이므로 정확성 역시 높다고 할 수 있다. 최초의 표를 만드는 데 필요한 시뮬레이션만을 수행하고 나면 만들어진 표를 이용하여 시뮬레이션 환경 외에서도 회로를 검증할 수 있다. 이로 미루어보았을 때 QLUT 기반 검증 방식은 기존의 물리적 증명 방법과 경쟁력을 가지고 있다고 할 수 있다.

Ⅴ. 결 론

본 논문에서는 QCA 환경 상에서 제안된 RAM 셀을 하나 특정하여 QLUT 기반 검증 방식으로 검증하였고, 이를 통해 시뮬레이션 결괏값과 일치하는 결과를 얻을 수 있음을 보였다. QLUT 기반 검증 방식으로 회로를 검증하는 것은 기존의 회로 검증 방식과 비교해 보았을 때 수식을 계산할 필요가 없어 연산량이 적고, 속도가 빠르며, 정확성 역시 높다. QLUT 기반 검증 방식은 차후에 대규모 QCA 회로를 더 빠르고 정확하게 검증하는 데 유용한 도구로 활용될 수 있을 것이며, 이를 바탕으로 더 큰 QCA 회로를 설계하는 데 사용될 수 있다.

Acknowledgments

이 논문은 2019년도 정부(교육부)의 재원으로 한국과학창의재단(2019년도 학부생 연구프로그램)의 지원을 받아 수행된 연구임.

References

-

K. H., Park and Y. H. Kim, "Skin Condition Analysis of Facial Image using Smart Device: Based on Acne, Pigmentation, Flush and Blemish", Journal JAITC, Vol. 8, No. 2, pp. 47-58, Dec. 2018

[https://doi.org/10.14801/JAITC.2018.8.2.47]

-

N. Z. Haron and S. Hamdioui, "Why is CMOS scaling coming to an END?", 2008 3rd International Design and Test Workshop, Monastir, pp. 98-103. Dec. 2008.

[https://doi.org/10.1109/IDT.2008.4802475]

-

J. C. Jeon, "Extendable Quantum-Dot Cellular Automata Decoding Architecture Using 5-Input Majority Gate", International Journal of Control and Automation, Vol. 8, No. 12, pp. 107-118, Dec. 2015.

[https://doi.org/10.14257/ijca.2015.8.12.10]

-

S. Erniyazov and J. C. Jeon, "Implementation of Full Adder Using 5-Input Majority Gate", International Engineering & Technology, Vol. 7, No. 4.4, pp. 17-18, Feb. 2018.

[https://doi.org/10.14419/ijet.v7i4.4.19598]

-

N. Safoev and J. C. Jeon, "Coplanar Qca Addres for Arithmetic Circuits", International Journal of Engineering & Technology, Vol. 7, No. 4.4, pp. 15-16, Sep. 2018.

[https://doi.org/10.14419/ijet.v7i4.4.19597]

-

S. Erniyazov and J. C. Jeon, "Carry save adder and carry look ahead adder using inverter chain basedcoplanar QCA full adder for low energy dissipation", Microelectronic Engineering, Vol. 211, pp. 37-43, Apr. 2019.

[https://doi.org/10.1016/j.mee.2019.03.015]

-

N. Safoev and J. C. Jeon, "A Novel Controllable Inverter and Adder/Subtractor in Quantum-Dot Cellular Automata Using Cell Interaction Based XOR Gate", Microelectronic Engineering, Feb. 2020.

[https://doi.org/10.1016/j.mee.2019.111197]

-

Y. W. You and J. C. Jeon, "Design of One-Bit Comparator Using Multilayer in Quantum-Dot Cellular Automata", Advanced Science Letters, Vol. 23, No. 10, pp. 10087-10091, Oct. 2017.

[https://doi.org/10.1166/asl.2017.10394]

- S. Erniyazov and J. C. Jeon, "Low power consumption Quantum-dot cellular automata (QCA) magnitude comparator with single layer wire-crossing technique", Asia Life Sciences, Vol. 18, No. 3, pp. 1471-1478, Apr. 2019.

-

J. C. Jeon, "7-input Majority Gate Based Priority Encoder Using Multi-Layer Quantum-Dot Cellular Automata", Advanced Science Letters, Vol. 23, No. 10, pp. 10118-10122, Oct. 2017.

[https://doi.org/10.1166/asl.2017.10400]

-

Y. W. You and J. C. Jeon, "Design of Falling-Edge Triggered T Flip-Flop based on Quantum-Dot Cellular Automata", International Journal of Engineering & Technology, Vol. 7, No. 4.4, pp. 19-20, Sep. 2018.

[https://doi.org/10.14419/ijet.v7i4.4.19599]

-

J. C. Jeon, "Low Complexity QCA Universal Shift Register Design Using Multiplxer and D Flip-Flop Based on Electronic Correlations", The Journal of Supercomputing, pp. 1-15, Aug. 2019.

[https://doi.org/10.1007/s11227-019-02962-y]

-

A. H. Majeed, E. AlKaldy, and S. Albermany, "An energy-efficient RAM cell based on novel majority gate in QCA techonology", SN Applied Sciences, Article no. 1354, Oct. 2019.

[https://doi.org/10.1007/s42452-019-1330-6]

- N. Safoev and J. C. Jeon, "Design of Extendable Binary to Gray Code Converter Using Quantum-Dot Cellular Automata", International Journal of Mechanical Engineering and Technology, Vol. 10, No. 2, pp. 587-596, Feb. 2019.

-

N. Safoev and J. C. Jeon, "Design of high-performance QCA incrementer/decrementer circuit based on adder/subtractor methodology", Microprocessors and Microsystems, Vol. 72, Feb. 2020.

[https://doi.org/10.1016/j.micpro.2019.102927]

-

S. R. Kassa and R. K. Nagaria, "A novel design of quantum dot cellular automata 5-input majority gatewith some physical proofs", Journal of Computational Electronics, Vol. 15, No. 1, pp. 324-334, Oct. 2015.

[https://doi.org/10.1007/s10825-015-0757-2]

-

K. Walus, T. J. Dysart, G. A. Jullien, and R. A. Budiman, "QCADesigner: A Rapid Design and Simulation Tool for Quantum-Dot Cellular Automata", Vol. 3, No. 1, pp. 26-30, Mar. 2004.

[https://doi.org/10.1109/TNANO.2003.820815]

2019년 3월 ~ 현재 : 금오공과대학교 컴퓨터공학과 재학 중

관심분야 : 양자회로, 블록체인, 정보보안, 인공지능 등

2000년 2월 : 금오공과대학교 컴퓨터공학과(공학사)

2003년 2월 : 경북대학교 컴퓨터공학과(공학석사)

2007년 2월 : 경북대학교 컴퓨터공학과(공학박사)

2009년 3월 ~ 2012년 8월 : 우석 대학교 정보보안학과 교수

2012년 9월 ~ 현재 : 금오공과대학교 컴퓨터공학과 교수

관심분야 : 정보보안, 암호학, 암호회로설계, 양자회로설계, 양자프로토콜, 블록체인 등