저 잡음 저 전력 CMOS 다중 위상 VCO 설계

초록

본 논문에서는 무선 랜 802.11a 표준의 5GHz UNII band에서 동작하는 무선 송수신기의 다중 전압조절 발진기(Quadrature Voltage Controlled Oscillator)를 제안하였다. 또한 직교위상 출력을 스위칭 전류소스의 입력으로 사용한 새로운 구조의 저잡음, 저전력의 quadrature coupled VCO를 제안하였다. 이 구조를 응용하여 전류소스가 분리된 구조나 전류소스를 공통으로 사용하는 등의 다른 회로에 적용하면, 기존의 VCO보다 17dB 개선된 위상잡음 특성을 얻을 수 있다. 특히나 기존의 동위상의 QVCO와 비교하여 간단한 구조로 저 전력으로 동작하도록 설계하였다. 회로의 설계는 TSMC 0.13µm RF CMOS 공정으로 1.2V의 supply 전압을 사용하였다. 측정된 VCO는 4.5~5.6GHz의 주파수에서 동작하는 20%의 큰 튜닝 범위를 갖으며, 1MHz offset에서 -117dBc/Hz 이하의 위상잡음을 얻었다. 제안한 QVCO의 출력 위상 오차는 0.5도 이하를 갖고, 전체 전력 소비는 1.2V에서 5.3 mW을 얻을 수 있었다.

Abstract

This paper proposed Quadrature coupled voltage controlled oscillator for a wireless LAN 802.11a standard transceiver in 5GHz UNII band. And also, low phase noise and low power CMOS QVCO of which ouput of quadrature phase put in input of switching current source has proposed. A new coupling and switched biasing schemes have been proposed for the implementation of a low phase noise LC-tank QVCO. The proposed QVCO implemented in a 0.13mm CMOS technology shows 17dB phase noise improvement over the conventional QVCO while the two QVCOs consume the same power. This concept can be very applicant for other circuits for example, seperation structure of current source, common structure of current source and expected more improved phase noise. The phase noise of the closed loop voltage-controlled oscillator (VCO) has been achieved -117dBc at 1MHz offset from 5.15GHz. The QVCO has had a wide tuning range of 20% from 4.5GHz to 5.6GHz. The phase error between the quadrature outputs has been smaller than 0.5° and the total power consumption has been 5.3mW from 1.2V power supply voltage.

Keywords:

low power, phase Noise, quadrature coup led voltage controlled oscillator, complementary metal oxide semiconductorⅠ. 서 론

오늘날 발전된 무선 송수신기의 변조방식은 송신 path와 수신 path 모두에 I/Q (In-phase, Quadrature-phase)의 LO 신호를 필요로 한다. I/Q 신호를 갖는 LO 신호를 만들기 위해 널리 사용하는 방법으로는 poly-phase 필터, VCO+주파수 분주기(I/Q clock 발생기), 직교위상형 전압제어발진기(Quadrature-coupled VCO )가 있다[1]-[4]. 이 방법들은 전력 소모, 집적화, 노이즈 등 각각의 장단점을 가지고 있으며, 이 논문에서는 이들에 대한 특징에 대해 설명할 것이다.

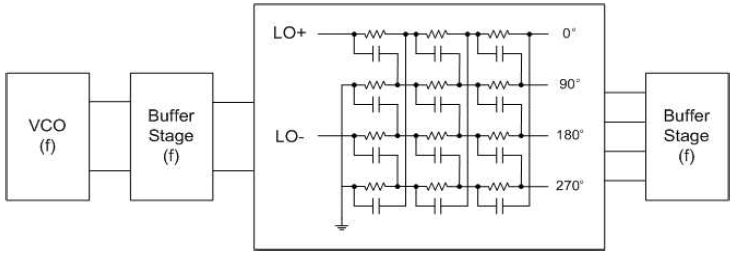

Poly-phase 필터를 이용한 방법은 그림 1에서 나타낸 것과 같이 RC network의 위상 변화를 사용하여 I/Q 위상 신호를 만들어 낸다. 하지만 출력 진폭을 일정하게 하기 위해 다단의 RC network을 직렬로 연결해야하기 때문에 resistance에 의한 손실이 생기게 된다. 이로 인한 LO 전압 swing의 감소는 mixer의 잡음을 증가시키는 원인이 되므로, 이를 보상하기 위해 출력 단에 큰 전류를 소모하는 버퍼 stage가 필요하게 되므로 이로 인한 큰 전력을 소모한다는 단점을 가진다.

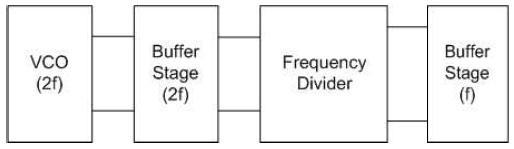

VCO+주파수 분주기를 사용한 방법은 그림 2의 master-slave 플립플롭 구성된 주파수 분주기의 출력을 사용하여 I/Q 신호를 만들어 낸다. 이 구조는 주파수 분주기의 사용으로 원하는 주파수를 위해 VCO는 두 배의 주파수에서 동작해야 한다. 그러므로 보다 작은 크기의 인덕터를 사용하고 주파수 분주기의 면적이 매우 작으므로 집적화 측면에서 큰 장점을 가지고 있으며, 두 배의 주파수 사용으로 LO pulling을 피할 수 있다. 하지만 이 방법도 출력 단에 버퍼가 필요하게 되므로 전체 전력 소모는 증가하게 된다.

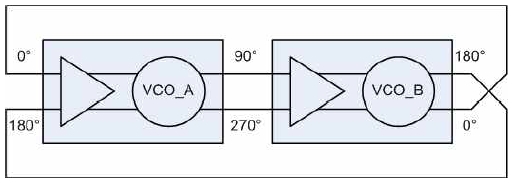

마지막으로 quadrature coupled VCO는 커플링 트랜지스터를 사용하여 동일한 두 VCO를 그림 3과 같이 직접연결(Direct connection)과 교차연결(Cross connection)함으로써 같은 주파수에서 동작하는 분리된 I/Q 신호를 생성하는 방법이다. 이 방법은 두 개의 VCO를 사용함으로 인한 인덕터의 증가로 인해 큰 면적을 차지하고, VCO의 잡음원인 트랜지스터의 증가로 위상잡음이 증가하는 단점을 가지지만 추가의 버퍼가 필요 없어 앞서 설명한 두 방법과 비교하여 적은 전류를 사용한다는 장점을 가지고 있다.

Ⅱ. Rofougaran에 의해 제안된 QVCO

가장 널리 알려진 QVCO는 Rofougaran에 의해 제안된 그림 4의 병렬 커플링 트랜지스터를 사용한 구조이다[4].

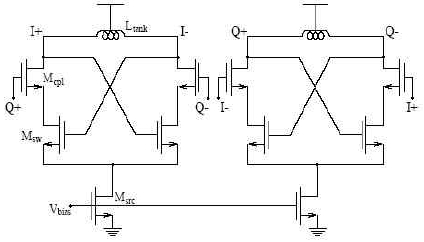

이것은 스위치 트랜지스터 Msw에 병렬로 연결된 트랜지스터 Mcpl에 의해 두 VCO가 커플링되는 구조를 갖는다. 이 구조는 두 트랜지스터의 크기에 의해 위상잡음과 위상에러가 서로 상반되는 특성을 가지고 있다. 이를 개선하여 Andreani는 그림 5의 회로와 같이 커플링 트랜지스터를 직렬로 연결하여 위상에러와 무관하고 10dB의 위상잡음을 개선한 구조를 제안하였다[4]-[6]. 이 외에도 QVCO의 위상잡음 및 위상에러 등의 특성을 개선한 많은 연구들이 발표되었다.

Ⅲ. 제안된 저 잡음 Quadrature VCO 설계

본 연구에서는 Rofougaran의 QVCO를 기본으로 하여 보다 개선된 위상잡음을 가지는 QVCO를 제안하였다. VCO의 구조는 nMOS와 pMOS의 직교 커플링 구조를 사용하여 적은 전류를 사용하여 저 전력으로 발진할 수 있도록 설계하였다.

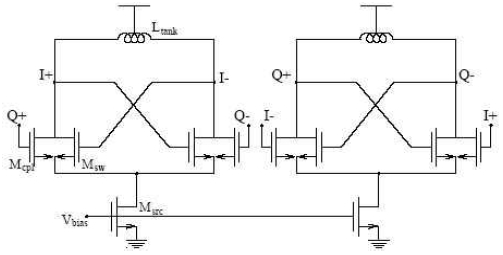

그림 6의 QVCO는 quadrature 위상을 커플링하기 위해 nMOS에만 병렬로 트랜지스터를 사용하였으며, 특별하게 고정된 bias 전류소스 대신 Boon이 제안한 스위칭 트랜지스터[6]를 사용한 전류소스를 기본으로 설계하였다.

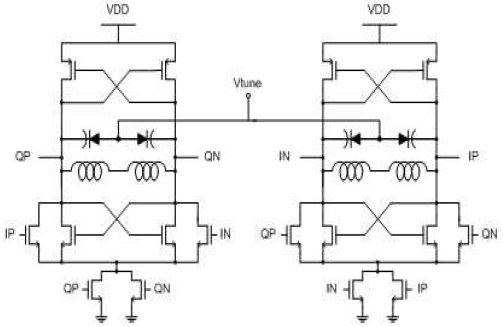

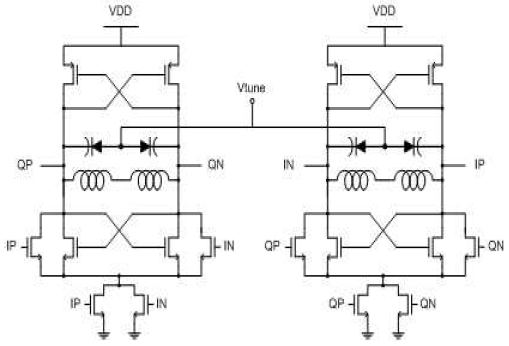

전류소스의 스위칭은 큰 출력 진폭을 스위칭 트랜지스터의 게이트 입력으로 사용하여 가능하다. 이 스위칭 트랜지스터는 MOS의 gate oxide에 갇혀있는(Trapped) 전자를 풀어주는 힘을 가지기 때문에 플리커 노이즈(Flicker noise, 1/f noise)를 감소시키게 된다. 이는 [6]에서 비교한 바와 같이 고정된 전류소스나 전류소스를 사용하지 않은 VCO보다 더 개선된 위상잡음을 가진다. 이 구조를 기반으로 본 연구에서 제안하는 구조는 그림 7과 같이 전류소스의 입력으로 동위상(In-phase)을 가지는 VCO의 출력이 아닌 직교위상(Quadrature-phase)을 가지는 VCO의 출력을 사용한다. 예를 들어, QP와 QN의 출력을 갖는 VCO의 전류소스의 gate 입력으로 IP와 IN의 입력하고 반대로 IP와 IN의 출력을 갖는 VCO의 전류소스의 gate 입력으로 QP와 QN을 사용한 것이다. 이 구조는 출력 전압의 swing과 전류소스의 드레인 공통노드의 위상을 일치시킴으로 인해 전류소스에 의해 제한된 출력 swing을 더 크게 함으로 인해 위상잡음을 감소시키게 된다.

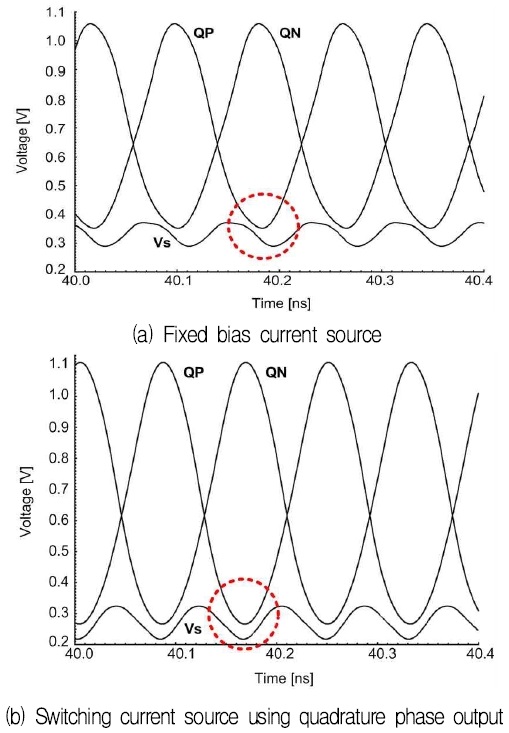

고정된 바이어스 및 그림 6의 전류소스를 가지는 VCO는 triode영역 트랜지스터의 resistance와 전류소스의 공통 드레인 노드의 capacitance에 의한 time delay로 인해 그림 8(a)와 같이 출력 위상파형과 전류소스의 공통드레인 노드의 파형이 일치하지 않는다. 하지만 제안된 구조를 사용함으로 그림 8(b)와 같이 두 위상 파형을 일치시킴으로 더 큰 출력 진폭을 갖게 한다. VCO의 위상잡음은 출력 진폭의 크기와 비례하므로 더 개선된 위상잡음을 갖게 된다[7]-[10].

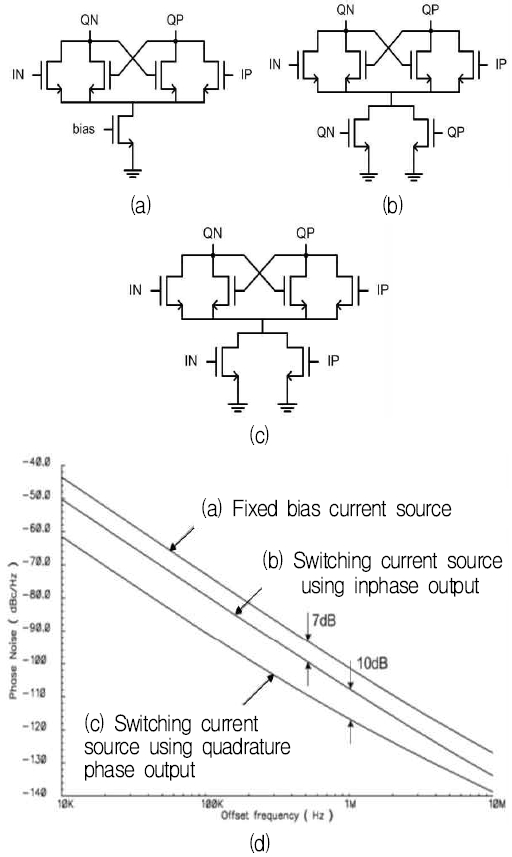

그림 9는 고정된 바이어스를 사용하였을 때와 동위상의 출력 및 직교위상의 출력을 전류소스의 입력으로 사용한 제안된 구조의 위상잡음 특성을 시뮬레이션한 결과이다. 고정된 바이어스를 사용했을 때와 비교하여 17dB 개선됨을 알 수 있다. 그림 7은 가장 기본이 되는 회로이며, 이를 응용하여 전류소스가 분리된 구조나 전류소스를 공통으로 사용하는 등의 다른 회로에 적용하면, 보다 개선된 위상잡음 특성을 얻을 수 있다.

QVCO with tail current source, (a) Fixed bias current source, (b) Switching current source using inphase output, (c) Switching current source using quadrature phase output, (d) Output graph of each current source

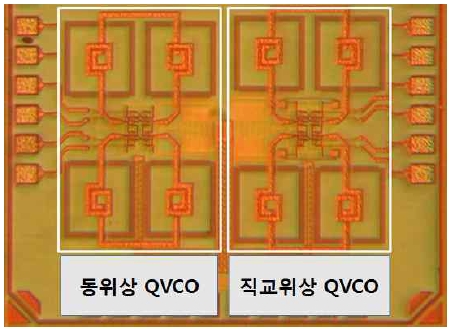

그림 10은 CMOS QVCO의 마이크로 칩 사진을 찍은 그림이다. 동일한 회로상에서 동위상 QVCO와 직교위상 QVCO 칩의 실제 공정상의 칩사진을 보여주고 있다.

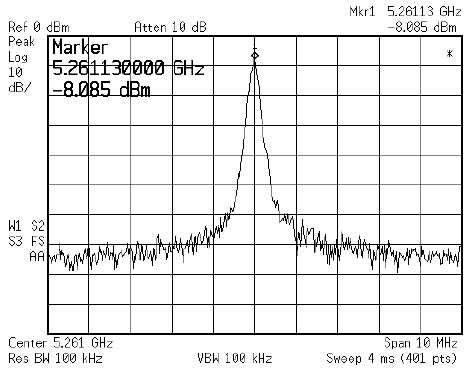

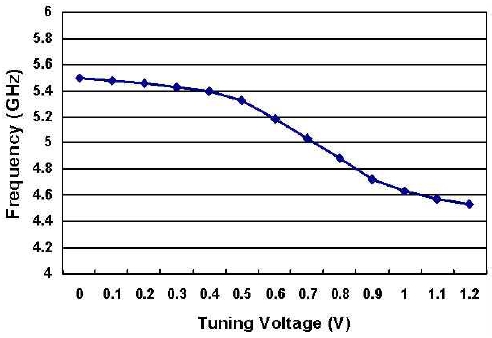

그림 11은 직교위상 스위칭시의 QVCO의 출력 파형으로 –8.085dBm의 높은 출력파형을 얻을 수 있었다. 그림 12에서는 0V ~ 1.2V에서의 control 전압이 변화함에 따라 5.5GHz에서 4.5GHz로 일정한 주파수 간격을 갖으며 공진주파수가 변화함을 알 수가 있다. 주파수 간격이 상대적으로 일정치 않은 범위는 LC-tank를 위해 사용된 p+n 다이오드 바랙터(Varactor)의 특성에 의해 나타나는 현상으로 바랙터 양쪽의 두 단자 사이에 전압이 reverse로 걸려있던 것이 forward로 걸려 나타나게 되는 현상이다.

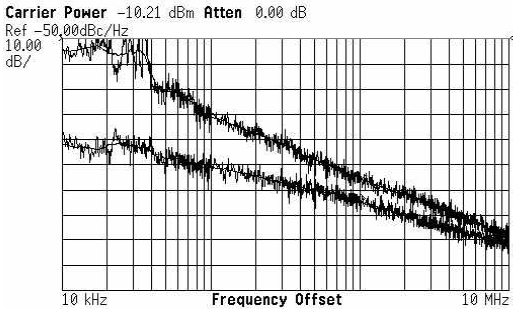

그림 13에서는 기본적인 컨셉의 QVCO와 이번 논문에서 제안한 QVCO의 위상 잡음(Phase noise) 파형을 비교하여 보여주고 있는 그림이다.

직교위상 스위칭을 갖는 QVCO의 경우 EEE 802.11a WLAN 목표 주파수인 5.5GHz에서 위상 잡음이 -117dBc/ Hz@1MHz를 얻었음을 보여주고 있다.

이 논문에서는 기본적인 컨셉의 QVCO와 비교해 LO 전압 swing을 증가시키기 위해 직교위상 스위칭을 갖는 QVCO를 제안하여 저전력을 사용하더라도 같은 크기의 스윙을 얻는 방식을 사용하였다.

표 1은 다른 논문들 [3][11]~[13]과의 비교를 나타낸 것이다. VCO의 성능을 나타내는 잘 알려진 식 (1)에서와 같이 FOM(Figure Of Merit)을 다음과 같이 쓸 수 있다. 표 1에서 보여지듯이 CMOS QVCO중 5~6GHz대역에서 동작하는 타 논문들과 비교해 이 논문에서 제시한 QVCO가 FOM이 184.6으로 가장 높음을 나타내고 있다.

| (1) |

Ⅳ. 결 론

본 논문에서는 무선 랜 802.11a 표준의 5GHz UNII band에서 동작하는 무선 송수신기의 다중전압조절 발진기를 제안하였다. 또한 직교위상 출력을 스위칭 전류소스의 입력으로 사용한 새로운 구조의 저잡음, 저전력의 quadrature coupled VCO를 제안하였다. 이 구조를 응용하여 전류소스가 분리된 구조나 전류소스를 공통으로 사용하는 등의 다른 회로에 적용하면, 보다 개선된 위상잡음 특성을 얻을 수 있다. 특히 기존의 동위상의 QVCO와 비교하여 17dB나 개선된 위상잡음을 얻을 수 있었으며 간단한 구조로 저 전력으로 동작하도록 설계하였다. 회로의 설계는 TSMC 0.13µm RF CMOS 공정으로 1.2V의 supply 전압을 사용하였다. 측정된 VCO는 4.5~5.6GHz의 주파수에서 동작하며, 1MHz offset에서 -117dBc/Hz 이하의 위상잡음을 얻었다. 제안한 QVCO의 출력 위상 오차는 0.5도 이하를 갖고, 전체 전력 소비는 1.2V에서 5.3 mW을 얻었다.

Acknowledgments

This work has been supported by Hannam University, 2019

References

- H. Hegazy, K. Sharaf, and H.F. Ragai, "A comparative study of CMOS-based quadrature integrated LC VCO topologies", Proc. 2002 45th Midwest Symposium on Circuits and Systems, Tulsa, OK, USA, Vol. 1, pp. 1-336, Aug. 2002

- A. Rofougaran, "A 900MHz CMOS LC-oscillator with quadrature outputs", in Proc. ISSCC 1996, San Francisco, CA, USA, pp. 392-393, Feb. 1996.

- R. van de Ven, J. van der Tang, D. Kasperkovitz, and A. van Roermund, "An optimally coupled 5 GHz quadrature LC oscillator", 2001 Symposium on VLSI Circuits. Digest of Technical Papers, Kyoto, Japan, pp. 115-118, Jun. 2001.

-

Lee Miyoung, "A Design of CMOS QVCO Using the High Performance Differential Inductor", Journal of KIIT, Vol. 17, No. 2, pp. 21-26, Feb. 2019.

[https://doi.org/10.14801/jkiit.2019.17.2.21]

-

P. Vancorenland and M. Steyaert, "A 1.57GHz fully integrated very low-phase-noise quadrature VCO", IEEE Journal of Solid-State Circuits, Vol. 37, No. 5, pp. 653-656, May 2002.

[https://doi.org/10.1109/4.997860]

-

P. Andreani, A. Bonfanti, L. Romano, and C. Samori, "Analysis and design of a 1.8-GHz CMOS LC quadrature VCO", IEEE Journal of Solid-State Circuits, Vol. 37, No. 12, pp. 1737-1747, Dec. 2002.

[https://doi.org/10.1109/JSSC.2002.804352]

-

Ali Hajimiri, "Design issues in CMOS differential LC oscillators", IEEE Journal of Solid-state Circuits, Vol. 34, No. 5, pp. 717-724, May 1999.

[https://doi.org/10.1109/4.760384]

-

B. Razavi, "A study of phase noise in CMOS oscillators", IEEE Journal of Solid-State Circuits, Vol. 31, No. 3, pp. 331-343, Mar. 1996.

[https://doi.org/10.1109/4.494195]

-

Barbara A. Chappell, "Fast CMOS ECL receivers with 100mV worst-case sensitivity", IEEE journal of solid-state circuits, Vol. 23, No. 1, pp. 59-67, Feb. 1988.

[https://doi.org/10.1109/4.257]

-

E. A. M. Klumperink, S. L. J. Gierkink, A. P. van der Wel, and B. Nauta, "Reducing MOSEF 1/f noise and power consumption by switched biasing", EEE Journal of Solid-State Circuits, Vol. 35, No. 7, pp. 994-1001, Jul. 2000.

[https://doi.org/10.1109/4.848208]

-

A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators", EEE Journal of Solid-State Circuits, Vol. 33, No. 2, pp. 179-194, Feb. 1998.

[https://doi.org/10.1109/4.658619]

- T. Liu, "A 6.5-GHz monolithic CMOS voltage-controlled oscillator", 1999 IEEE International Solid-State Circuits Conference, Digest of Technical Papers, San Francisco, CA, USA, pp. 404-405, Feb. 1999.

- H. Shin, Z. Xu, and M. F. Chang, "A 1.8V 6/9GHz switchable dual-band quadrature LC VCO in SiGe BiCMOS technology", 2002 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium. Digest of Papers, Seattle, WA, USA, pp. 71-74, Jun. 2002.

1999년 2월 : 전북대학교 정보통신공학과(공학사)

2001년 2월 : 전북대학교 정보통신공학과(공학석사)

2010년 8월 : 한양대학교 전자통신전파공학과(공학박사)

2011년 2월 : 카이스트 박사 후 연구원

2011년 3월 ~ 2019년 12월 현재 : 한남대학교 전자공학과 교수 재직 중

관심분야 : RFIC and Hybrid 설계