수직 분할 링 공진기를 이용한 S-밴드 발진기 설계

*호서대학교 전자디스플레이공학부**호서대학교 전자디스플레이공학부(교신저자)

초록

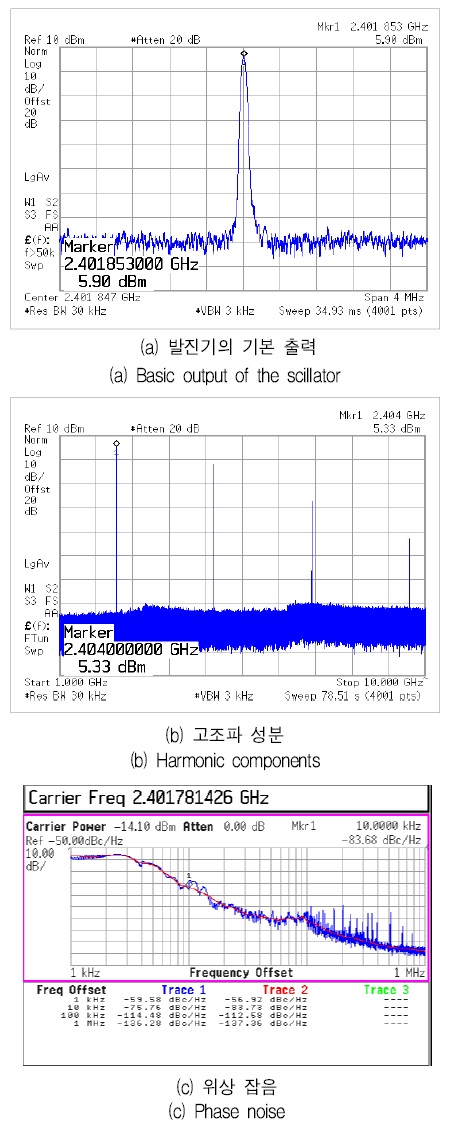

본 논문에서는 수직 분할 링 공진기(VSRR, Vertical Split Ring Resonator)를 적용하여 전기적 크기를 축소시킨 발진기를 제안하였다. VSRR은 유전체 기판의 상면과 하면에 일렬로 놓인 마이크로스트립 라인간에 발생하는 커패시턴스와 인덕턴스에 의해서 공진기로 동작하는 분리형 링 공진기(Split Ring Resonator)형태이며, 마이크로스트립 라인을 이용한 일반적인 hairpin 형태 또는 평면형 링 공진기에 비해 공진 회로의 전기적 크기를 축소할 수 있는 장점이 있다. 본 논문에서는 S-band에서 동작하는 VSRR을 설계하고, 이를 공진회로로 사용한 발진기를 설계 및 구현한 결과를 제시하였다. 제안된 발진기는 2.4GHz에서 5.9dBm의 출력을 나타내었으며, 오프셋 주파수 100kHz에서 –112.58dBc@Hz, 1MHz에서 –137.36dBc@Hz의 위상잡음 특성을 나타내었다.

Abstract

In this paper, we propose a S-band oscillator with a reduced electrical size by applying a vertical split ring resonator(VSRR). The VSRR is a type of split ring resonator that operates as a resonator by the capacitance and inductance generated between the microstrip lines arranged on the top and bottom of the dielectric substrate and it has an advantage that the electrical size of the resonance circuit can be reduced as compared with the conventional ring resonator. In this paper, we design a VSRR operating over S-band and an oscillator using the VSRR as the resonant circuit. The proposed oscillator showed the output of 5.9dBm at 2.4HGz and showed the phase noise characteristics of –112.58dBc at 100KHz offset frequency and –117.85dBc at 1MHz offset.

Keywords:

microwave oscillator, vertical split ring resonator, miniaturized resonator, metamaterial, split ring resonatorⅠ. 서 론

오늘날의 위성 통신 및 이동 통신과 같은 마이크로웨이브 시스템에서 주파수 변환과 반송파 발생은 매우 중요한 요소로써, 발진기는 이 요소를 충족시키기 위해 사용되는 가장 필수적인 부품이다. 발진기는 시스템의 안정도 및 효율성에 큰 영향을 미치는 마이크로파 시스템의 국부발진기로 사용되며, 장거리 통신시 위상 잡음은 채널 대역폭과 수신 오율에 큰 영향을 주기 때문에 발진기의 위상 잡음 특성은 시스템의 감도와 선택도 결정에 있어 매우 중요한 요소로 위상 잡음을 최소화하기 위해 많은 연구가 진행되어 왔다[1]-[4]. 한편 마이크로웨이브 시스템에서 발진기의 주파수 안정도를 높이기 위해 높은 Q값을 가지며, 공진기의 부피를 축소하는 방향으로 크게 공동 공진기, 마이크로스트립 공진기, 유전체 공진기로 분류하여 연구되었다. 공동 공진기는 제작이 용이하며 Q값이 큰 장점이 있지만 공진기 형태 특성상 부피가 크고 무거운 단점이 있기 때문에 집적화가 힘든 특징을 갖는다. 마이크로스트립 공진기는 평면구조를 사용하여 직접화하기 용이하지만 낮은 Q값을 가지기 때문에 위상 잡음 특성이 좋지 못한 단점이 있다. 유전체 공진기는 다양한 형상으로 설계 할 수 있어 소형화와 회로 구현이 용이하고 높은 Q값을 갖는 장점이 있지만 유전체 공진기의 동작 특성상 3차원 구조로 제작하여야 하기 때문에 MMIC(Monolithic Microwave Integrated Circuit)에 활용하기 힘든 단점이 있다[5]. MMIC는 칩이 실장되는 회로의 전체 면적이 가격에 큰 영향을 주기 때문에 분할 링 공진기(SRR, Split Ring Resonators)와 같은 평면 형태의 구조를 사용하지만 2D 패턴의 형태는 넓은 면적을 차지하며, 상대적으로 큰 손실과 좁은 대역폭을 가짐으로 이를 해결하기 위한 많은 연구가 진행 되었다[6]-[8].

한편, 메타 물질(Metamaterial)은 인공적으로 가공된 음의 유전율과 음의 투자율을 동시에 갖는 자연에 존재하지 않는 물질을 뜻한다. 이러한 메타 물질은 “left-handed material”로 알려져 있으며, 이는 일반적으로 사용하는 물체의 기본 물질 특성이 아닌, 물질에 구성되는 회로 소자를 특정한 형태의 구조를 갖도록(일반적으로 반복적인 패턴의 배열) 함으로써 음의 유전율과 투자율이 생성되는 새로운 물리적 특성을 이용하게 된다. 이러한 메타물질은 CRLH(Composite Right/Left Handed 전송선 이론을 통해 등가회로 모델이 정립되었으며, 특정 주파수에서 위상속도가 영(0)이 되는, 소위 영차 모드 공진(Zeroth-order Resonance), 혹은 무한 파장 공진 현상을 가지고 있다. 즉, 영이 아닌 주파수에서 영의 전파상수를 가지게 되고, 무한 파장의 전기적 길이 성분으로 공진을 발생한다[9]. 이러한 영차 모드 공진은 주파수에 무관한 특성으로 인하여 안테나, 필터 등의 다양한 고주파 무선 부품의 소형화에 적용 가능하다. 이중 분리형 링 공진기는 평면적인 구성이 가능하여 구현이 용이하여 여러 가지 무선 통신용 회로에 많이 사용되고 있다. 하지만, 평면에 구현되기 때문에 차지하는 면적이 적지 않으므로 소형화에 있어 제약이 발생한다.

따라서 본 논문에서는 메타 물질 구조를 유지하면서 형태를 더 소형화 할 수 있는 새로운 형태의 분리형 링 공진기로 수직 분할 링 공진기를 제시하고, 이를 이용하여 ISM 대역에 적용하여 소형화된 발진기를 제안하였다. 본 논문 II장에서는 수직 분할 링 공진기(VSRR, Vertical Split Ring Resonator)의 동작 원리와 등가 모델에 대한 시뮬레이션 결과를 나타내었으며, VSRR을 적용한 발진기의 설계 결과를 3장에 기술하였다. 4장에서는 앞선 장들의 시뮬레이션 결과를 토대로 발진기를 제작 및 측정한 결과를 나타내고, 5장에 결론을 제시하였다.

Ⅱ. VSRR 설계

2.1 VSRR 구조 및 동작원리

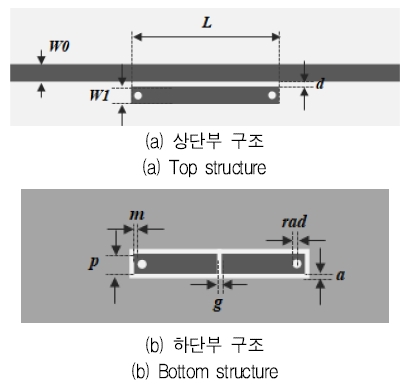

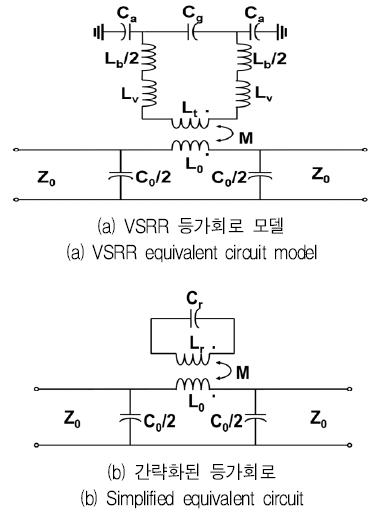

제안된 수직 분할 링 공진기의 구조는 그림 1과 같이 유전체 기판의 상부, 하부에 놓인 마이크로스트립 라인과 via hole로 구성된다. 상부에 높인 마이크로스트립 라인과 하부에 놓인 마이크로스트립 라인은 via hole로 전기적으로 연결되며, 하단부의 라인 중간이 단선되어 있는 형태로 구성되어, 수직 구조의 헤어핀 공진기 형태로 동작하게 된다. 이러한 VSRR을 마이크로스트립 전송선에 적용하였을 때의 등가 모델은 그림 2(a)에 나타낸 것과 같다.

Lo와 Co는 공진기가 위치한 구간을 통과하는 마이크로스트립 전송선로의 인덕턴스와 커패시턴스이며, Cg는 VSRR 하단부의 라인 갭 사이의 커패시턴스, Ca는 VSRR 하단부 라인과 접지면 사이의 커패시턴스, Lt와 Lv는 상단부 VSRR의 인덕턴스, Lb는 상부층과 하부층을 연결하는 via hole에 의해 발생하는 인덕턴스이다.

이를 발진기 회로 설계에 적용하기 위하여 간단한 LC 공진회로로 등가 변환한 것을 그림 2(b)에 나타내었으며, 이 때의 Lr, Cr값은 식 (1), (2)에 의해 주어지며, 이 때, 공진주파수 ωr은 식 (3)과 같이 주어진다[10]-[12].

| (1) |

| (2) |

| (3) |

2.2 ISM대역에서의 VSRR 설계

VSRR을 발진기의 공진부로 사용하기 위하여 전송선로에 인가된 VSRR의 전기적 특성을 확인하기위해 ANSYS 사의 EM 시뮬레이터인 HFSS를 사용하여 시뮬레이션을 수행하였다. VSRR 회로의 기판은 두께 h = 0.508mm, 비유전율 3.5인 Taconic사의 RF-35를 사용하였으며, 전송선로의 50옴 선폭 W0와 VSRR의 선폭 W1은 1.15mm, 전송선로와 공진기의 사이 간격 d, 하단부 공진기 선로 사이의 간격 g, 하단부 공진기 선로와 접지면 사이 간격 a는 0.2 mm로 설정하였다. via hole의 반지름 rad는 0.25 mm로 설정하였으며, parasitic 성분의 발생을 최소화하기 위하여 via hole은 상부 전송선의 끝선과 간격 m을 0.2 mm로 설정하였다.

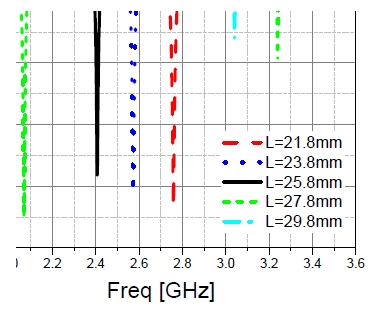

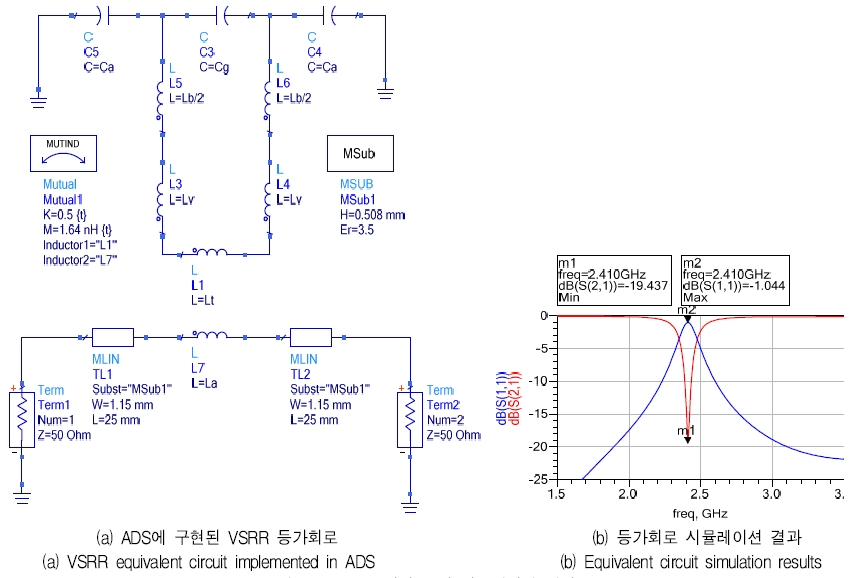

VSRR의 전기적 크기에따른 공진 특성을 확인하기 위하여 공진기의 길이 L을 21.8~29.8 mm 사이로 변경하여, 공진주파수의 변화를 HFSS로 시뮬레이션한 결과를 그림 3에 나타내었으며, 25.8mm의 길이에서 2.406 GHz의 공진 주파수를 갖는 것을 확인하였다. 설계된 VSRR을 발진기 설계에 적용하기 위하여 그림 2(a)에 나타낸 것과 같이 등가 회로 모델을 적용하였으며, HFSS를 통해 수행한 시뮬레이션 결과와 동일한 동작 특성을 얻기 위한 각 회로 소자의 파라미터를 Agilent사의 ADS(Advanced Design System)을 이용하여 시뮬레이션을 통해 구하였다.

그림 4(a)는 ADS 시뮬레이션에 사용한 VSRR의 등가 회로이며, 이를 시뮬레이션하여 얻은 등가 회로의 각 파라미터를 표 1에 나타내었다. 이 파라미터를 적용하여 회로 시뮬레이션을 수행한 결과를 그림 4(b)에 나타내었으며, HFSS를 통해 시뮬레이션 한 결과와 동일하게 2.41GHz에서 공진이 발생하는 것을 확인하였다.

Ⅲ. VSRR을 적용한 발진기 설계

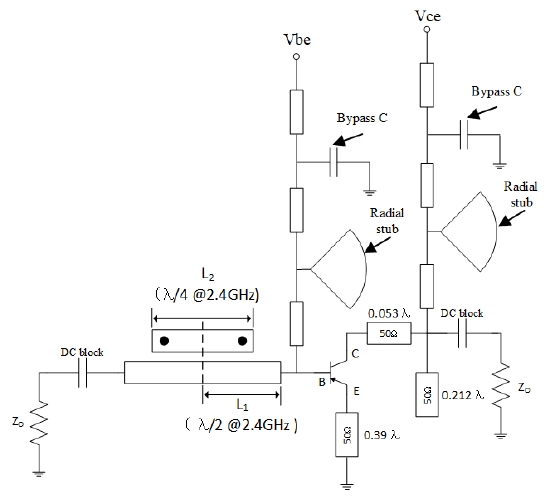

2장에서 제안된 VSRR을 적용하여 ISM대역에서 동작하는 발진기를 Broadcom사의 BJT인 AT-32033을 사용하여 설계하고, 시뮬레이션을 수행하였다. 제안된 발진기의 구조는 그림 5에 나타낸 것과 같으며, 트랜지스터에서 발진 현상이 안정적으로 발생되도록 에미터에 short stub를 연결하여 불안정 영역을 증가시켰다.

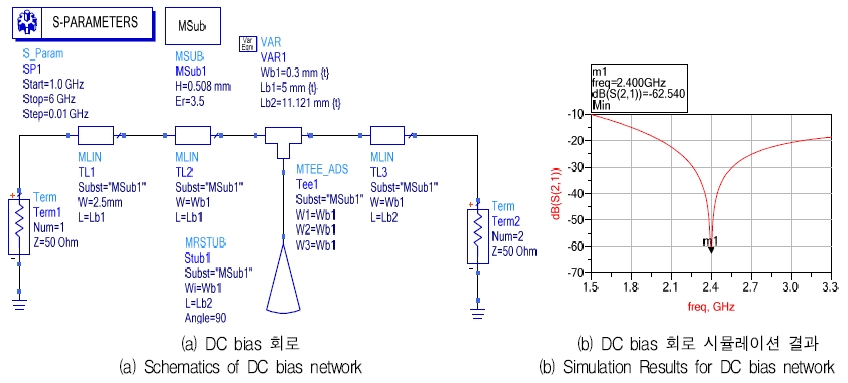

트랜지스터의 베이스에 연결된 VSRR에 의해 발진 현상이 발생하며, 이 때 공진기와 트랜지스터의 결합선로 길이 L1은 harmonic 성분을 최소화하기 위해 반파장 길이로 설정하였다. 공진 회로에 의해 결정된 임피던스를 사용하여 50옴 부하에 출력을 생성하기 위해 출력부의 임피던스 정합회로를 직렬 스터브와 병렬 스터브를 조합하여 구성하였다. 발진기의 DC bias 회로의 설계에서는 불필요한 잡음에 의해 불요파 발생 등이 발생하는 것을 막기 위하여 그림 6(a)와 같이 λg/4 길이의 마이크로스트립 선로와 radial stub를 이용한 RF choke 구조를 적용하고, DC 전압에 발생하는 노이즈를 줄여주기 위하여 커패시터를 추가하였다. DC bias회로의 동작 특성을 시뮬레이션한 결과를 그림 6(b)에 나타내었다.

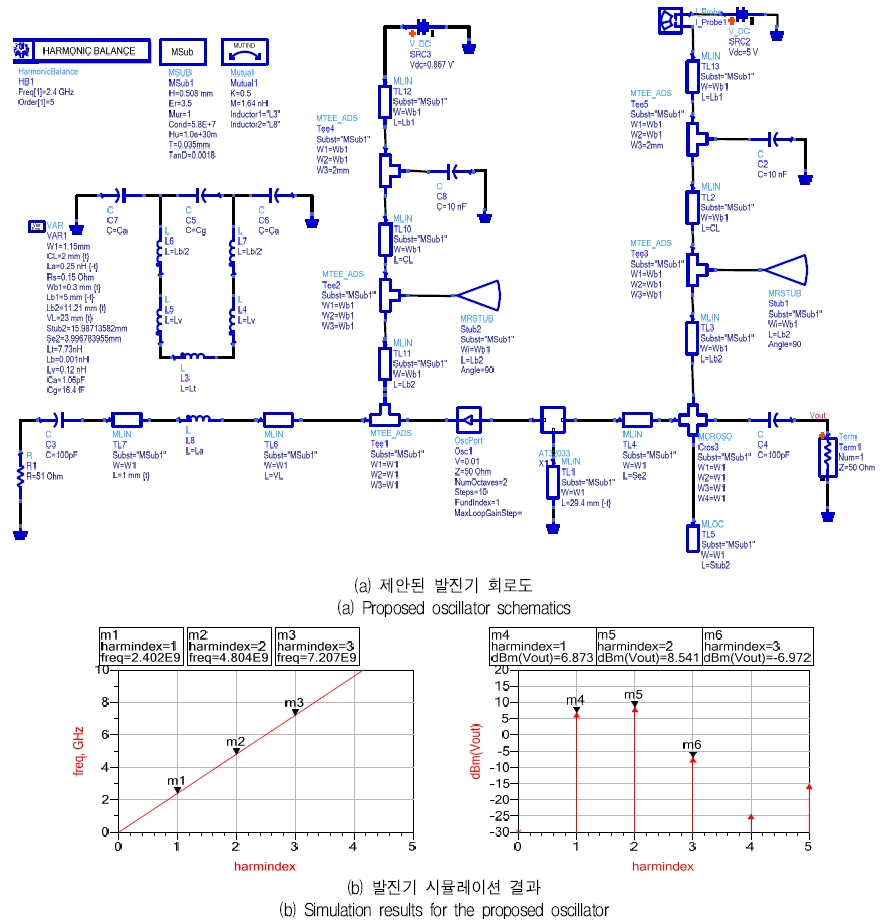

제안된 VSRR을 적용한 발진기의 동작 특성을 ADS를 이용하여 시뮬레이션하였다. 시뮬레이션을 위해 그림 7과 같이 VSRR의 등가 회로를 적용하였으며, 시뮬레이션 결과 2.402GHz에서 7dBm의 출력이 발생하는 것을 확인하였다.

Ⅳ. 발진기 구현 및 측정

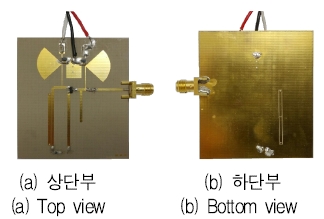

제안된 VSRR 발진기는 비유전율 3.5, 두께 0.508mm 를 갖는 taconic사의 RF-35를 사용하여 50×60mm2의 크기로 제작되었으며, 그림 8에 제작된 사진을 나타내었다. 발진기의 바이어스 조건은 VBE = 0.75V, VC =5V이며, 이 때, IC =50mA로 설정하였다.

제작된 발진기의 동작 특성은 Agilent사의 스펙트럼 분석기 E4440A를 사용하여 측정하였으며, 그 결과를 그림 9에 나타내었다. 출력 주파수 2.402GHz에서 5.9dBm의 출력을 나타내었으며, 시뮬레이션을 통해 얻은 출력 주파수와 거의 일치하였다. 또한, 2차 및 3차 고조파 성분은 각각 -7.43dBc, -22.61dBc로 측정되었다. 10kHz, 100kHz, 1Mhz 오프셋 주파수에서 위상 잡음을 측정한 결과는 각각 -83.73dBc/Hz, -112.58dBc/Hz, -137.36dBc/Hz로 나타났다.

V. 결 론

본 논문에서는 기존 평면형 공진기의 구조적 형상에서 벗어나 수직방향으로 분할 링 형태를 갖는 VSRR을 적용한 발진기를 제안하였다. 제안된 VSRR은 공진부의 상부면과 하부면이 via hole을 통해 수직으로 연결되어 기존의 평면형 분할 링 공진기에 비해 차지하는 면적이 줄어들어 발진기를 소형화할 수 있는 장점을 갖는다. 이러한 VSRR을 적용하여 ISM대역에서 동작하는 발진기의 설계를 진행하여, 성능을 검증하였다. 제작된 발진기는 2.4GHz 대역에서 5.9dBm의 출력을 나타내었으며, 위상 잡음을 측정한 결과 10kHz offset 주파수에서 -83.73dBc/Hz, 100kHz offset 주파수에서 -112.58dBc/Hz의 저잡음 특성을 나타내었다.

제안된 발진기는 VSRR을 적용하여 소형화 특성을 가질 뿐만 아니라, 공진기의 한 쪽 종단부를 50옴 종단으로 설계하여 향후 주입동기 발진기로 적용할 수 있다. 이렇게 주입동기 발진기의 형태로 설계할 경우, DC bias 회로의 변경을 통하여 저전력 수신기 구조인 SRR회로로 구현할 수 있을 것으로 판단된다.

Acknowledgments

본 연구는 2016년도 정부(미래창조과학부)의 재원으로 한국연구재단의 지원을 받아 수행된 기초연구사업임(No. NRF-2016R1C1B1013862)

References

-

Thomas H. Lee, "Oscillator Phase Noise: A Tutorial", IEEE J. of Solid-State Circuits, 35(3), p326-336, Mar.), (2000.

[https://doi.org/10.1109/4.826814]

- A. Hajimiri, and T. Lee, "A general theory of phase noise in electrical oscillator", IEEE J. of Solid-State Circuits, 33(2), p179-194, Feb.), (1998.

-

D. S. Kim, S. H. Chai, W. S. Yoon, "Design of Wideband Voltage Controlled Oscillator with Capacitor-Bank for IoT Sensor System", Journal of KIIT, 14(9), p11-18, Sep.), (2016.

[https://doi.org/10.14801/jkiit.2016.14.9.11]

- M. Y. Lee, "A Low power CMOS LC-tank VCO and Phase-shifting Network", Journal of KIIT, 10(1), p47-52, Jan.), (2012.

- E. Holtzman, "Solid State Microwave Power Oscillator Design", Artech House, (1992).

- C. Hwang, J. Lee, J. Kim, N. Myung, and J. Song, "Simple K-band MMIC VCO utilizing a miniaturized hairpin resonator and a three terminal p-HEMT varactor with low phase noise and high output power properties,", IEEE Microwave Wireless Compon. Lett., 13(6), p229-231, Jun.), (2003.

- Xian Qi Lin, and Tie Jun Cui, "Controlling the Bandwidth of Split Ring Resonators", IEEE Microwave Wireless Compon. Lett., 18(4), p245-247, Apr.), (2008.

-

A. K. Horestani, C. Fumeaux, S. F. Al-Sarawi, and D. Abbott, "Split ring resonators with tapered strip width for wider bandwidth and enhanced resonance", IEEE Microw. Wireless Compon. Lett., 22(9), p450-452, Sep.), (2012.

[https://doi.org/10.1109/lmwc.2012.2211341]

-

A. Lai, T. Itoh, and C. Caloz, "Composite Right/Left-handed Transmission Line metamaterials", IEEE microwave magazine, 5(3), p34-50, Sep.), (2004.

[https://doi.org/10.1109/mmw.2004.1337766]

-

J. Choi, S. Oh, S. Jo, W.-S. Yoon, and J. Lee, "Vertical Split Ring Resonator Using Vias With Wide Bandwidth and Small Electrical Size", IEEE Microwave Wireless Compon. Lett., 27(1), p16-18, Jan.), (2017.

[https://doi.org/10.1109/lmwc.2016.2629988]

- R. Grag, I. Bahl, and M. Bozzi, "Microstrip Lines and Slotlined", Norwood, MA, USA, Artech House, (2013).

- I. Bahl, and P. Bhartia, "Microwave Solid State Circuit Design", New York, NY, USA, Wiley, (1988).

2017년 2월 : 호서대 전자공학과(공학사)

2017년 3월 ~ 현재 : 호서대학교 전자디스플레이공학부(석사과정)

관심분야 : 초고주파 능동/수동회로, 재구성 안테나 시스템, 초고주파 센서 네트워크 시스템 등

2017년 2월 : 호서대 전자공학과(공학사)

2017년 3월 ~ 현재 : 호서대학교 전자디스플레이공학부(석사과정)

관심분야 : 초고주파 능동/수동회로, 재구성 안테나 시스템, 초고주파 센서 네트워크 시스템 등

2018년 2월 : 호서대 전자공학과(공학사)

2018년 3월 ~ 현재 : 호서대학교 전자디스플레이공학부(석사과정)

관심분야 : 초고주파 능동/수동회로, 재구성 안테나 시스템, 초고주파 센서 네트워크 시스템 등

1997년 2월 : 고려대 전파공학과(공학사)

1999년 2월 : 고려대 대학원 통신시스템공학과(공학석사)

2010년 8월 : 고려대 대학원 컴퓨터·전파통신공학과(공학박사)

1999년 3월 ~ 2015년 8월 : 한화탈레스(現한화시스템) 통신연구소 수석연구원

2015년 9월 ~ 현재 : 호서대학교 전자공학과 조교수

관심분야 : RF transceivers, Reconfigurable antenna systems, RF sensor systems 등