15-T 셀 기반의 저 전력 TCAM 설계

초록

TCAM(Ternary content-addressable memory)은 빠른 속도를 요구하는 응용분야에 사용되는 고속 검색 메모리이다. 대용량의 TCAM은 워드의 비트와 어드레스가 증가하여 매치라인과 서치라인의 수 즉, 커패시턴스가 증가한다. 본 논문에서는 매치라인의 전력소모를 감소시키기 위하여 매치라인의 커패시턴스를 감소시킨 15-T TCAM 셀과 선택적 매치라인 충전기법을 적용시킨 128비트×128비트 TCAM을 제안한다. 제안한 회로는 0.18um CMOS 공정을 사용하여 설계하였으며 HSPICE를 통해 타당성을 검증하였다. 이전의 선택적 충전 매치라인 기법과 비교하여 최소 사이클 시간은 28.2% 증가하였고 매치라인의 에너지 (fJ/bit/search)는 48.5% 감소하였으며 EDP(Energy Delay Product)는 28.4% 감소되었다. 또한 정상동작의 위험요소인 1 비트 미스매치상태의 매치라인은 매치상태의 매치라인과 0.53V의 전압 마진을 가진다.

Abstract

Ternary content-addressable memory (TCAM) is a high-speed search memory used for high-speed applications. A large capacity TCAM increases the bit and address of the word, which increases the number of match lines and search lines, and capacitance. We propose a 15-T TCAM cell that reduces the capacitance of the match line and an 128 bit × 128 bit TCAM that applies the selective match line charging technique to reduce the power consumption of the match line. The proposed circuit is verified through the HSPICE with 0.18um CMOS technology. The minimum cycle time increased by 28.2%, the match line energy (fJ/bit/search) decreased by 48.5% and the EDP (Energy Delay Product) decreased by 28.4% compared to the previous selective match line charging scheme. Also, the 1-bit mismatch match line, which is a risk factor in steady operation, has a voltage margin of 0.53V as compared with the match line of the match condition.

Keywords:

ternary content-addressable memory, 15-T TCAM cell, selective-charging match-line, EDPⅠ. 서 론

CAM(Content Addressable Memory)은 매우 빠른 검색속도를 요구하는 응용분야에서 사용되는 메모리이다. 서치동작을 통해 메모리의 저장 셀에 저장된 모든 데이터를 서치 데이터와 동시에 병렬로 비교하여 매치된 데이터의 주소 값을 출력하므로 고속으로 동작이 가능하다. 오늘날 CAM의 주요 상업적 응용은 네트워크 라우터에서 IP(Internet Protocol) 패킷을 분류하고 전달하는 것이다[1]. CAM의 기본적인 형태는 저장 셀의 개수에 따라 BCAM(Binary CAM)과 TCAM(Ternary CAM)으로 분류될 수 있으며 또한 매치라인(ML, Match Line), 서치라인(SL, Search Line), 그리고 CAM 셀의 연결 형태와 동작방식에 따라 NAND형과 NOR형으로 나누어진다. CAM의 병렬비교동작은 빠른 검색속도를 자랑하지만 ML과 SL이 충●방전하는 동작방식으로 인하여 전력소모가 매우 큰 단점을 가지고 있다[2]. 나아가 CAM은 구조적으로 크기가 증가하면 저장 셀 배열의 증가로 매치라인과 서치라인의 수 그리고 기생 커패시턴스가 증가한다. 이는 전력소모의 증가를 야기하므로 대용량 CAM 설계에서 설계자는 동작속도와 전력소모의 트레이오프(Trade-off)를 고려한 적절한 설계가 필요하다.

위와 같은 문제를 해결하기 위해 본 논문에서는 ML 커패시턴스를 줄인 15-T TCAM 셀과 선택적 충전 ML 기법을 적용한 TCAM을 제안한다. ML의 커패시턴스를 줄임으로써 ML 충전을 위한 전력소모를 감소시키며 TCAM에서 전력소모의 큰 비중을 차지하는 ML을 완전히 충∙●방전하지 않고 완전히 매치된 ML만을 선택적으로 충전함으로써 ML의 전력소모를 줄일 수 있다. 또한 일반적으로 TCAM에서 완전히 매치된 매치라인은 한 개에서 수개 정도이므로 TCAM의 용량이 커지더라도 ML의 전력소모를 감소시킬 수 있다. 제안하는 TCAM은 0.18um CMOS 공정을 사용하여 128비트×128비트의 크기로 설계하였으며 HSPICE로 검증하고 Cadence Virtuoso를 사용하여 배치설계를 완료하였다.

Ⅱ. 제안하는 구조

2.1 매치라인의 커패시턴스를 감소시킨 NOR형 15-T TCAM 셀

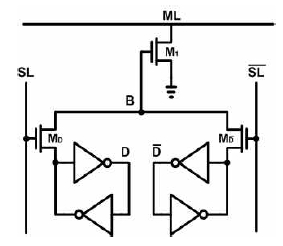

그림 1은 본 논문에서 제안하는 NOR형 TCAM셀의 구조를 보여준다. 트랜지스터의 개수는 종래의 NOR형 TCAM 셀과 비교하여 하나 감소한 15개이다. ML에 연결되는 NMOS 트랜지스터가 기존의 NOR형에 비해 2개에서 1개로 감소하므로 NMOS로 인한 ML의 기생 커패시턴스는 기존의 구조와 비교하여 절반으로 감소한다. 노드 B는 D와 SL의 값에 따라 매치일 경우 ‘0’, 미스매치일 경우 VDD - Vtn의 전압을 가진다. 그러므로 NMOS 트랜지스터 M1은 매치일 경우 OFF되어 ML에서 접지로의 방전 경로가 차단되고, 미스매치일 경우 ON되어 접지와의 방전경로를 형성한다. 또한 내부 데이터노드 D와 가 모두 1일 경우 노드 B는 검색 데이터에 상관없이 무조건 ‘0’이 되어 ‘X’동작을 수행할 수 있다. 표 1은 D와 SL에 따른 ML의 상태를 표로 정리한 것이다.

2.2 제안하는 선택적 충전 매치라인

그림 2는 본 논문에서 제안하는 매치라인 기법의 충전 제어기와 MLSA(Match Line Sense Amplifier)의 회로도이다. 충전 제어기는 6개의 트랜지스터로 구성되며 제어신호 MLP와 MLC에 의해 동작한다. M1은 최소 크기로 설정하여 1 비트 미스매치인 매치라인과의 마진을 확보하고 M2는 크기를 크게 하여 매치상태인 매치라인을 빠르게 충전할 수 있도록 한다. 또한 MLSA는 ML의 매치여부를 감지하여 ML 감지출력 MLSO(Match Line Sensing Output)를 출력한다.

2.3 제안하는 TCAM의 동작

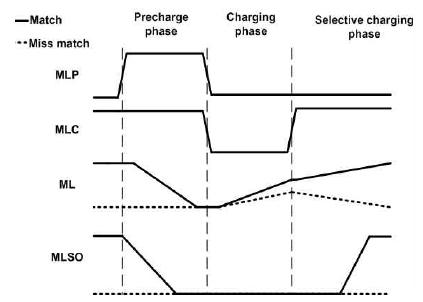

그림 3은 제안하는 매치라인 기법을 적용시킨 n개의 TCAM 셀을 가지는 ML의 구조를 나타낸 것이다. 제안하는 매치라인 기법의 검색동작은 매치라인의 이전상태를 초기화하기 위한 ‘프리차지 단계’, 매치라인의 전압을 충전제어부가 선택적으로 충전할 수 있을 만큼 충전시키는 ‘충전 단계’, 마지막으로 매치라인을 선택적으로 충전하는 ‘선택적 충전 단계’의 세 가지 단계로 이루어진다.

먼저 프리차지 단계에서 제어신호 MLC는 이전부터 ‘high’를 유지하고 있으며 MLP는 ‘low’에서 ‘high’로 입력된다. MLC는 ‘high’를 계속 유지하고 있으므로 M1은 이전부터 OFF를 유지하고 있다. MLP로 인하여 M3는 ON 되고 M2에 high를 전달하여 M2 또한 OFF 되므로 ML로의 충전경로는 없다. 또한 이전 매치결과 값을 가지고 있는 ML은 M7을 통해 방전되어 초기화된다. MLSA는 MLP에 의해 M7이 ON되어 이전의 MLSO값을 0으로 초기화하고 유지한다. 다음으로 충전 단계에서 MLP와 MLC는 모두 ‘low’로 입력된다. M1은 ON 되어 ML의 충전을 시작한다. M6는 OFF 되어 MML들을 제외한 접지로의 경로는 차단된다. 매치상태의 워드에서 MML은 모두 OFF 되므로 접지로의 방전경로가 형성되지 않고 ML만을 충전하게 된다.

그러나 미스매치인 TCAM 셀이 하나라도 존재하면 접지로의 경로가 형성되어 ML에서 충전과 방전이 동시에 일어나게 된다. M1의 크기는 최소로 설정되어 있으므로 미스매치인 ML들은 매우 느린 속도로 충전된다. 따라서 매치와 미스매치 ML간의 충전 속도는 차이가 발생한다. 충전단계는 매치상태인 ML의 전압이 M4가 ON 시킬 수 있을 만큼 지속된다. TCAM 셀의 구조로 인해 ML의 커패시턴스가 감소되었기 때문에 ML을 충전하기 위한 전력소모는 이전의 구조에 비해 적게 소모되고 최소크기의 M1을 사용하더라도 충전은 빠르게 이루어진다.

마지막으로 선택적 충전 단계가 되면 MLP는 ‘low’를 유지하고 MLC는 ‘high’로 입력된다. MLC로 인하여 M1은 OFF 되어 충전을 중단하고 미스매치인 ML들은 MML을 통해 방전된다. 그러나 매치상태인 ML은 접지까지의 방전경로가 존재하지 않으며 이전단계에서 M4를 ON시킬 만큼 충전되어있다. 따라서 매치상태의 ML은 MLC로 인해 ON된 M5를 통하여 M2의 게이트는 방전되게 된다.

이후 매치상태의 ML은 크기가 큰 M2가 ON 되어 VDD까지 빠르게 충전되며 MLSO의 값을 플립시킨다. 결과적으로 매치인 ML에서의 출력 MLSO는 ‘high’가 되고 미스매치인 ML은 ‘low’를 유지한다. 그림 4는 제안하는 매치라인 구조의 타이밍 다이어그램이다.

2.4 제안하는 매치라인의 전력소모

ML의 충전은 매치인 ML이 M4를 ON 시킬 만큼 충전된다. 충전시간은 매치상태인 ML을 기준으로 할당하기 때문에 모든 ML은 매치된 매치라인과 동일한 충전시간을 갖는다. 미스매치 상태의 ML은 충전 단계 이후 더 이상 충전되지 않는다. 또한 매치인 ML의 수는 미스매치인 ML에 비해 무시할 수 있는 수준이므로 미스매치인 ML의 전력소모를 구한다. NMOS 트랜지스터의 문턱전압을 Vtn라고 할 때 미스매치상태인 ML의 검색동작에서 소모되는 전력소모는 다음과 같다.

| (1) |

여기서 VDD는 공급전압, f는 동작주파수, CMLtotal은 ML의 총 커패시턴스이며 메탈로 인한 커패시턴스 Cmetal과 NMOS로 인한 커패시턴스 CNMOS의 합이다. 따라서 n bit인 워드 m개를 가지는 TCAM의 전체 ML 전력소모 PMLtotal은 식 (2)와 같다.

| (2) |

이 경우 NMOS가 두 개인 기존의 NOR형 매치라인 구조와 비교하였을 때 전체 ML의 전력소모는 워드의 비트 수가 증가할수록 더욱 감소한다.

2.5 제안하는 TCAM의 설계

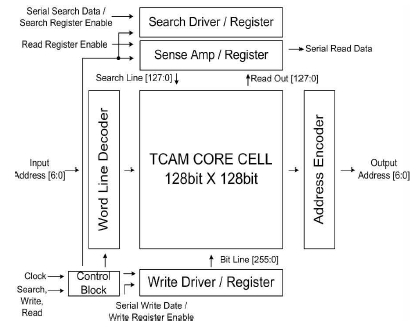

그림 5는 본 논문에서 제안하는 128비트×128비트 TCAM 설계의 전체 구조를 보여주는 블록도이다. 제안하는 TCAM 셀과 충전제어기 및 MLSA로 구성된 128비트×128비트 코어 셀 블록이 존재한다.

또한 제어신호를 생성하는 제어블록, 주소 입출력을 위한 인코더와 디코더 그리고 단일 칩으로 구현하기 위하여 입, 출력 데이터를 직렬 및 병렬로 변환할 수 있는 레지스터 및 드라이버로 구성되어 있다. 읽기와 쓰기 동작을 위한 드라이버와 레지스터는 편의를 위해 하나의 블록으로 표현하였다.

Ⅲ. 시뮬레이션 결과

그림 6은 본 논문에서 제안한 TCAM의 HSPICE 시뮬레이션 한 결과이다. ML0는 매치상태인 ML이며 ML1부터 1 비트 씩 점점 미스매치가 증가한 상태이다. 2장의 타이밍 다이어그램과 동일하게 MLP와 MLC의 입력에 따라 세 가지 단계로 동작하는 것을 확인할 수 있다.

표 2는 시뮬레이션 환경과 성능을 표로 정리한 것이다. MLD(Match-Line Delay)는 매치라인의 충전신호 MLC의 입력으로부터 매치결과 MLSO0가 출력될 때까지의 지연시간이다. MLE(Match-Line Energy)는 한주기의 검색동작에 1비트당 소모되는 매치라인의 에너지이다. EDP는 MLD와 MLE의 곱으로 표현되는 TCAM의 매치라인 성능지표이다.

표 3은 이전에 제안된 CAM들과 본 논문에서 제안하는 TCAM의 성능을 나타낸 표이다. 다른 공정의 이전에 제안된 CAM들과 비교하였을 때 공정 및 공급전압을 고려해도 좋은 성능을 보인다[3]-[9].

NOR형 TCAM의 경우 프리차지 단계와 평가 단계에서 미스매치인 셀이 존재할 경우 SC(Short-Circuit) 전류가 발생한다[10][11]. 제안하는 TCAM은 ML을 저 전압 프리차지 하므로 충전 단계에서 미스매치인 셀이 존재하면 SC 전류가 발생한다. 본 논문의 시뮬레이션 환경에서 SC 전류로 인하여 발생하는 매치라인의 소모 전력은 검색동작에서 소모되는 매치라인 전체 전력의 약 45.5%이다.

Ⅳ. 결 론

본 논문에서는 TCAM에서 전력소모의 큰 비중을 차지하는 매치라인의 전력소모를 감소시키기 위하여 매치라인의 커패시턴스를 감소시킬 수 있는 15-T TCAM 셀과 선택적 충전 매치라인 방식을 적용한 TCAM을 설계하고 검증하였다. 제안한 TCAM은 이전의 선택적 충전 매치라인 기법과 비교하여 동일 사이즈에서 최소 사이클 시간은 28.2% 증가하였고 매치라인의 에너지 (fJ/bit/search)는 48.5% 감소하였으며 EDP는 28.4% 감소되었다.

Acknowledgments

본 논문은 2016년도 강원대학교 학술연구조성비로 연구하였음(관리번호:520160247)

본 연구에 사용한 CAD S/W는 반도체설계교육센터(IDEC)의 지원에 의한 것임.

References

- N. F. Huang, W. E. Chen, J. Y. Luo, and J. M. Chen, "Design of multi-field IPv6 packet classifiers using ternary CAMs", 2001 IEEE Global Telecommunications Conference, 3, p1877-1881, Nov), (2001.

-

B. D. Yang, Y. K. Lee, S. W. Sung, J. J. Min, J. M. Oh, and H. J. Kang, "A Low Power Content Addressable Memory Using Low Swing Search Lines", IEEE Transaction on Circuits And Systems. I: Regular papers, 58(12), p2849-2858, Dec), (2011.

[https://doi.org/10.1109/tcsi.2011.2158703]

-

S. H. Yang, Y. J. Huang, and J. F. Li, "A low-power ternary content addressable memory with pai-sigma matchlines", IEEE Transaction on Very Large Scale Integration System, 20(10), p1909-1913, Oct), (2012.

[https://doi.org/10.1109/tvlsi.2011.2163205]

- J. W. Zhang, Y. Z. Ye, and B. D. Liu, "A current-recycling technique for shadow-ML sensing in content-addressable memories", IEEE Transaction on Very Large Scale Integration System, 16(6), p677-682, Jun), (2008.

-

I. Hayashi, et al. , "A 250-MHz 18-Mb full ternary CAM with low-voltage matchline sensing scheme in 65-nm CMOS", IEEE Journal Solid-State Circuits, 48(11), p2671-2680, Nov), (2013.

[https://doi.org/10.1109/jssc.2013.2274888]

-

A. T. Do, S. Chen, Z. H. Kong, and K. S. Yeo, "A high speed low power CAM with a parity bit and power-gated ML sensing", IEEE Transaction on Very Large Scale Integration System, 21(1), p151-156, Jul), (2013.

[https://doi.org/10.1109/tvlsi.2011.2178276]

-

P. T. Huang, et al. , "0.339 fJ/bit/search energy-efficient TCAM macro design in 40nm LP CMOS", 2014 IEEE Asian Solid-State Circuit Conference, p129-132, Nov), (2014.

[https://doi.org/10.1109/asscc.2014.7008877]

- C. Wang, C. Hsu, C. Huang, and J. Wu, "A self-disabled sensing technique for contentaddressable memories", IEEE Transaction Circuit and System II: Express Briefs, 57(1), p31-35, Jan), (2010.

- S. Mishra, and A. Dandapat, "EMDBAM: A low-power dual bit associative memory with match error and mask control", IEEE Transaction on Very Large Scale Integration System, 24(6), p2142-2151, Jun), (2016.

-

M. Zackriya V, and H. M. Kittur, "Precharge-Free, Low-Power Content-Addressable Memory", IEEE Transaction on Very Large Scale Integration System, 24(8), p2614-2621, Aug), (2016.

[https://doi.org/10.1109/tvlsi.2016.2518219]

-

M. M. Hasan, A. B. M. H. Rashid, and M. M. Hussain, "A Novel Match-line Selective Charging Scheme for High-Speed, Low-Power and Noise-Tolerant Content-Addressable Memory", 2010 International Conference on Inteligent and Advanced System, p1-4, Jun), (2010.

[https://doi.org/10.1109/icias.2010.5716226]

2016년 2월 : 강원대학교 전자공학과(공학사)

2018년 2월 : 강원대학교 의료융합학과 전자공학전공(공학석사)

2018년 4월 현재 : 강원대학교 의료 융합학과 전자공학전공 박사과정

관심분야 : SRAM 설계, 저 전력회로 설계

1985년 2월 : 인하대학교 전자공학과(공학사)

1987년 2월 : 인하대학교 전자공학과(공학석사)

1997년 2월 : 포항공대 전자전기공학과(공학박사)

1987년 ~ 1992년 : 금성반도체 중앙연구소 선임연구원

1997년 ~ 1998년 : 현대전자 시스템IC 연구소 책임연구원

1999년 ~ 현재 : 강원대학교 전자공학과 교수

관심분야 : VLSI 설계, 저 전력회로 설계