교류형 플라즈마 디스플레이 패널에서 기입 전압을 낮추기 위한 중첩 주사파형

초록

교류형 플라즈마 디스플레이 패널에서 기입 전압을 낮추기 위하여 주사 전극들이 겹치게 인가되는 중첩 주사 파형이 제안되었고 기입 방전의 특성이 연구된다. 기입 기간에는 주사 및 기입 펄스가 동시에 인가될 때 선택된 셀에서 방전이 발생한다. 일반적으로 기입 전압을 낮추면 방전의 지연 시간이 길어지기 때문에 기입기간에 인가되는 펄스의 폭을 늘여야한다. 그러나 1 TV 프레임 시간이 제한되어 있으므로 기입 펄스의 폭은 무한정 늘일 수 없다. 한편, 주사 전극에 인가되는 펄스는 주사 선에 의해 순차적으로 펄스가 인가되므로 펄스의 폭을 중첩시켜서 늘일 수 있다. 즉 기입 펄스의 폭은 종래의 시간과 동일하고 주사 펄스의 폭들만 각각 늘여서 주사 라인들이 중첩된 파형이 제안되었다. 낮은 기입 전압의 인가에 의해 방전 지연시간은 당연히 늦어질 것이나 길어진 주사 펄스의 폭에 의해 기입 방전은 펄스의 폭 안에서 안정적으로 발생하였고 기입 전압을 종래보다 약 13V 낮출 수 있었다.

Abstract

In order to lower the write voltage in the AC type plasma display panel, a superposed scan waveform in which the scan electrodes are overlapped is proposed and the characteristics of the write discharge are studied. The discharge occurs in the selected cell when the scan and write pulses are simultaneously applied during the write period. In general, when the write voltage is lowered, the delay time of the discharge becomes longer, so that the width of pulse applied during the write period must be increased. However, since the TV frame time is limited, the width of the write pulse can not be extended indefinitely. On the other hand, since the pulses applied to the scan electrodes are sequentially applied with the scanning lines, the widths of the pulses can be superposed and extended. That is, a waveform in which the widths of the write pulses are equal to the conventional time and the scan lines are superposed by extending only the widths of the scan pulses has been proposed. Due to the application of the low writing voltage, the discharge delay time will be delayed naturally, but the writing discharge stably occurs within the width of the pulse due to the width of the scan pulse and the write voltage can be lowered by about 13V than the conventional one.

Keywords:

discharge characteristics, superposed scan, plasma display, write voltage, discharge delayⅠ. 서 론

교류형 플라즈마 디스플레이 패널(AC PDP)은 한때 대형 디스플레이로서 유망한 소자였으나 높은 소비전력등과 같은 몇 가지 문제 때문에 현재는 생산되지 않고 있다[1][2]. 그러나 만약 몇 가지 문제점을 해결한다면 대형 디스플레이로서 아주 매력적인 소자가 될 것이라고 기대된다[3][4]. AC PDP에서 발생되는 소비전력은 두 가지의 종류가 있는데, 하나는 방전에 의해 발생되는 유효 소비전력과 다른 하나는 외부 인가 전압에 의해 만들어지는 무효 소비전력이다[5]. 방전에 의한 빛의 세기와 관련된 유효 소비전력은 제어가 불가능하므로, 전체 소비전력을 낮추기 위해서는 무효 소비전력을 낮춰야한다. AC PDP의 구동파형은 크게 3가지 기간으로 나누어져 있다. 초기화, 기입, 그리고 유지 기간이 그것이다[6]. 초기화 기간 동안은 파형이 급격히 변하지 않으므로 소비되는 전력은 적다. 유지 기간에서는 수백 볼트의 사각 파형이 두 개의 상판 전극에 교대로 인가되므로 소비전력이 매우 높으나 에너지 회수회로 기술을 이용하여 소비 전력을 낮출 수 있었다[7]. 그러나 기입 기간 동안에는 수백 개의 주사와 기입 펄스가 인가되지만, 에너지 회수 회로를 사용하기가 매우 어렵다[8]. 그러므로 기입 기간에서 소비전력을 낮추기 위해서는 주사 및 기입 전압을 낮춰야 한다. 그중 주사 전압은 소비전력에 큰 영향을 주지 않으므로 기입 전압을 낮추는 방법이 제일 효과적이다.

기입 기간에서 주사 펄스가 수평 라인의 처음부터 마지막까지 시간에 따라 일정한 간격으로 인가되는 동안 수직 라인에 기입 펄스가 인가되면 서로 만나는 셀에서 기입 방전이 발생된다. 이 기입 방전이 주사 및 기입 펄스의 폭 내에서 안정적으로 발생되어야만 유지 기간에서 정상적으로 빛이 생성된다. 그런데 만약 기입 전압을 낮춘다면 기입 방전이 불안정하게 발생하거나 방전이 실패하여 유지 기간에 빛이 발생하지 않게 된다.

플라즈마 디스플레이 패널에서 전압이 인가되면 필연적으로 방전 지연 현상이 발생한다. 기입 기간의 주사 및 기입 펄스의 폭 내에서 기입 방전이 발생되어야만 안정적인 벽전하 축적이 이루어지고 유지 기간에서도 안정적인 방전에 의해 정상적인 빛이 생성된다. 기입 방전의 지연 시간은 기입 전압이 높을수록 짧아지지만 소비전력은 상승하는 역효과를 유발한다. 그러므로 만약 기입 방전을 안정적으로 발생시키면서 기입 전압을 낮출 수 있다면 AC PDP의 소비전력을 낮출 수 있을 것이다.

본 연구에서는 소비전력을 낮추기 위하여 기입전압을 낮추더라도 방전을 안정적으로 발생시키기 위하여 중첩 주사 파형이 제안된다. 중첩 주사 파형은 기입 펄스의 폭은 기존 그대로 두고 주사 펄스의 폭을 각각 늘려서 서로 중첩되는 파형이다. 즉, 하나의 주사 펄스의 폭을 기존보다 늘려서 다음의 주사 펄스와 중첩되도록 설계된 파형이다. 기입 펄스의 폭은 종래와 같으므로 전체 기입 시간의 변화는 발생하지 않는다. 먼저 종래의 구동파형을 인가할 때 주사 시간에 따른 기입 전압의 최대와 최소 전압을 측정하고 각 기입 방전의 지연시간을 측정한다. 또한 중첩 주사파형을 인가 할 때 기입 전압의 최대와 최소 전압을 측정하여 종래와 비교할 것이다.

Ⅱ. 패널 및 구동파형

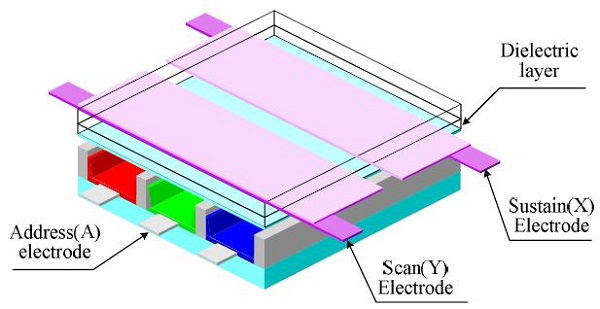

그림 1은 실험에 사용된 세 개의 셀을 가진 AC PDP의 구조를 나타낸다. 상판에는 두 개의 전극이 있는데, 각각 유지 (X) 및 주사 (Y) 전극으로 구분된다. 이 전극은 버스 전극이라고도 불린다. 그리고 각 버스 전극에서 중앙 부분으로 투명 전극인 ITO가 도포되어있다. 투명한 ITO 전극은 셀 내에서 발생된 빛을 가리지 않으므로 상판의 두 전극 사이에서 방전이 쉽게 발생하도록 전극의 간격을 가깝게 설계할 수 있는 장점이 있다. 상판에서 마지막으로 방전 공간에 접하는 부분인 유전체 층은 직접적으로 전극을 노출시키지 않고 보호하는 역할을 한다. 하판에서는 기입 전극 (A)이 상판의 두 전극과 수직 방향으로 나열되어 있으며 각각 격벽으로 분리된다. 기입 전극 위에 빛의 삼원색인 레드, 그린, 블루 형광체로 도포되어 있다. 셀 내부에 사용된 가스는 Ne-Xe 혼합 가스가 사용되었다.

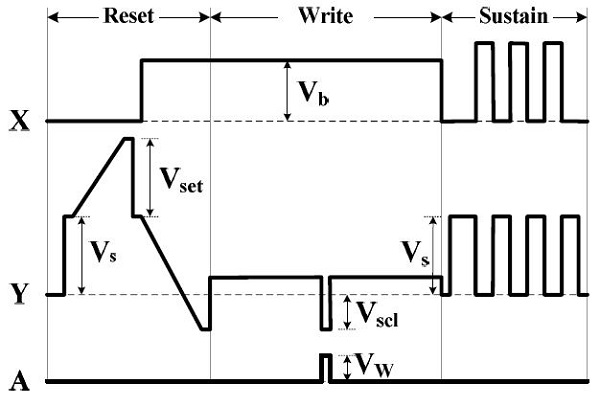

그림 2는 실험에 사용된 하나의 부화면 시간 동안 세 개의 전극에 인가된 종래의 구동파형을 나타낸다. AC PDP는 하나의 TV 프레임 시간 동안에 여러 개의 부-프레임으로 나눈 계조의 조합으로 휘도를 표시하고, 부-프레임은 각각 초기화, 기입, 유지 기간으로 나누어진다. 초기화 기간은 전체 셀의 내부에서 이전에 쌓인 벽전하들을 동일한 상태로 만들어주고 기입 방전을 발생시키기 위한 벽전하 상태로 재배열하는 역할을 한다. 기입 기간에서는 X 전극에 일정 전압이 인가된 상태에서 Y 전극에 주사 파형이 셀마다 순차적으로 인가되고 A 전극에 선택적으로 펄스가 인가될 때, 선택된 셀에서만 기입 방전이 발생된다. 기입 방전이 발생되면 셀 내부에는 벽전하가 쌓이게 되고 유지 기간에서 X와 Y전극에 교대로 인가된 사각 파형에 의해 빛이 발생된다. 그림 2에서 각각 Vs는 유지전압, Vset은 초기화 전압, Vb는 X 전극의 바이오스 전압, Vscl은 주사펄스의 전압, Vw는 기입 전압을 나타낸다.

Ⅲ. 방전 지연시간의 측정

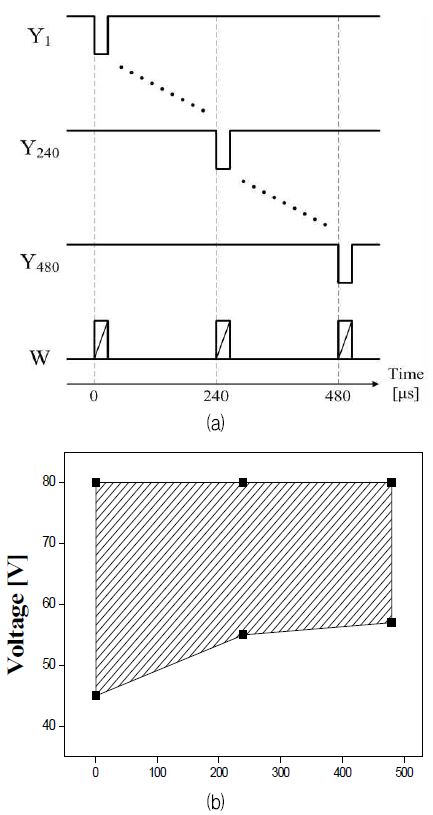

그림 3(a)에서는 기입 기간에서 수평 라인의 수가 480개인 Y 전극에서 하나의 주사 펄스의 폭이 1μs 일 때, 각 주사 파형과 기입 파형을 그린 것이다. Y1은 첫 번째 주사 라인에서의 파형, Y240은 중간 라인에서의 파형, 그리고 Y480은 마지막 라인에서의 구동 파형이다. 그 외의 시간에서의 파형들은 생략되었다. 기입 전압은 주사 전극의 주사 파형과 동일한 시점에서 같은 폭을 갖도록 인가되었다. 기입 펄스에서 사선은 선택적으로 인가되었음을 가리킨다.

Driving waveform applied to Y electrodes in write period over time (a) and margin of write voltage (b)

그림 3(b)는 그림 3(a)에서의 각 위치에 기입 펄스를 인가하였을 때 기입 전압의 마진을 나타낸다. 플라즈마 디스플레이 패널에서 전압의 마진이란 방전이 실패하지 않고 성공적으로 발생하는 영역을 의미한다. 즉, 그림 3(b)에서 선의 외부에서는 방전이 실패하거나 오방전이 발생함을 의미한다. 그런데, 그림에서 최대 전압이 80V로 같은 이유는 기입 회로에서 IC가 견딜 수 있는 최대 전압이기 때문이고 높은 기입전압에 의해 소비전력이 높아지기 때문에 실제로 사용되지 않는 부분이다. 방전을 발생시킬수 있는 최소 전압은 첫 번째 라인에서 제일 낮고 중간과 마지막 라인에서는 높다.

첫 번째 라인에서 기입 전압이 제일 낮은 이유는 그림 2에서의 초기화 기간에서 생성된 많은 프라이밍 입자와 벽전하들이 첫 번째 방전에 큰 영향을 주기 때문이다. 반대로 중간과 마지막에서는 프라이밍 입자와 벽전하들이 시간에 따라 줄어들기 때문에 방전을 발생시키기 위하여 높은 기입 전압이 필요하다.

그림 3에서의 결과에 의해 실험에서 사용된 패널의 조건에서 종래의 구동 파형에 의해 방전이 안정적으로 발생하기 위해서는 기입 전압이 최소한 60V 이상이 되어야 한다는 것을 볼 수 있다.

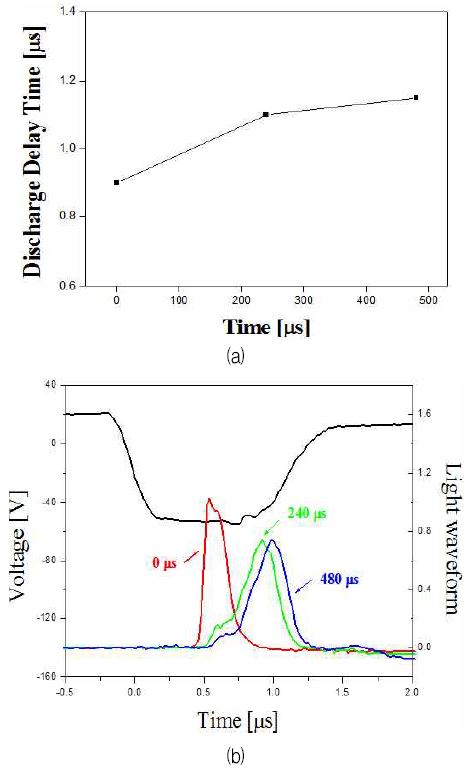

그림 4(a)는 기입 펄스 폭이 1μs이고 전압이 60V일 때, 기입 기간에서 시간의 변화 따른 방전의 지연 시간을 나타낸 것이고, 그림 4(b)는 주사 및 기입펄스가 인가될 때 시간에 따른 광 파형을 보이고 있다. 그림 3(b)의 기입 전압 마진에서 전압을 고정시켰을 때 기입 방전은 시간이 지남에 따라 지연됨이 확인되었다. 방전의 크기 또한 시간이 지나면서 약해지고 방전의 분포도 넓어졌다. 한편 중간 및 마지막 시간에서의 방전의 세기는 큰 차이가 없었다.

Ⅳ. 중첩 주사 파형

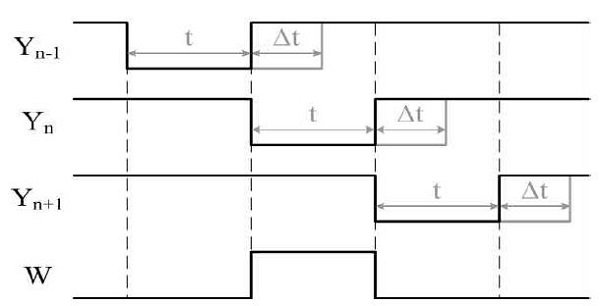

본 연구에서는 방전 지연 시간을 단축시키는 것보다는 낮은 기입 전압에 의해 방전이 지연되더라도 셀 내부의 벽전하를 안정적으로 축적하고 유지 방전을 정상적으로 발생시키기 위하여 중첩 주사파형을 적용하였다. 다시 말하면, 소비전력을 낮추기 위하여 낮은 기입 전압을 사용하면 필연적으로 기입 방전이 지연되고, 중첩 주사 파형은 각 주사전극에서 펄스 폭이 일정 시간만큼 늘여서 방전을 안정적으로 발생시킬 수 있는 파형이다. 그러나 전체 기입 시간은 동일하게 유지하기 위하여, 제안된 중첩 주사 파형에서는 각 주사 라인에서 펄스의 인가 시간을 늘린 만큼 중첩시키고 기입 펄스는 종래와 동일한 펄스 폭으로 인가되었다.

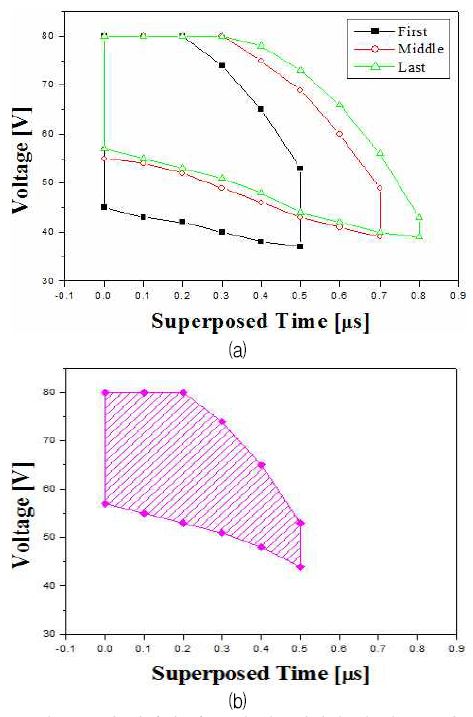

그림 5는 기입 기간에서 Y 전극에 인가된 중첩주사 파형과 W 전극에서의 기입 펄스를 보이고 있다. 세 개의 주사 파형 중에 W 전극에서 기입 펄스를 중간의 파형에만 인가한 이유는 앞선 주사 파형에서의 중첩된 시간에 의한 오방전의 발생 여부를 조사하기 위한 것이다. 즉, Yn과 W 전극의 펄스에 의해 방전이 발생되어야 정상이지만, Yn-1 전극에서 중첩된 펄스 폭(△t)에 의해 오방전이 발생할 가능성이 있다. 또한 Yn+1 전극에서의 펄스는 이전의 주사 전극에서의 방전에 의한 영향이 존재하는지의 여부를 측정하기 위한 것이다.

그림 6(a)에서는 그림 5에서의 구동파형을 적용하였을 때 중첩 시간(△t)에 따른 세 위치에서의 전압 마진을 측정한 것이다. 첫 번째 시간에서는 이전의 주사 펄스가 없으므로 인접 라인과의 오방전 여부를 측정하기 위하여 두 번째 주사 시간에서 측정이 되었다. 다른 실험 결과와 비교해서 첫 번째 시간에서 중첩 시간이 늘어날수록 최대 전압이 급격히 하강하는 이유는 빠른 기입 방전의 발생에 의해 이전 전극에서의 펄스와 겹치는 시간에 오방전이 발생되기 때문이다. 즉 Y1 전극에서 △t 시간과 W전극에서의 시간 t와 중첩되기 때문에 잘못된 방전이 발생되었다. 만약 기입 전압이 낮아질수록 방전이 늦게 발생하므로 오방전도 줄어든다.

Each write voltage margin at three positions with superposed time (a), and common voltage margin area at total panel

또한 최소 전압은 중첩 시간에 의해 전압이 조금씩 낮아짐을 볼 수 있다. 중첩시간이 늘어날수록 방전 지연시간은 길어지지만 낮은 전압에서도 방전이 성공하였다. 중간 및 마지막 시간의 측정 결과도 첫번째 시간과 비슷한 경향을 가지지만, 중첩될수록 첫 번째 시간에서보다 더 긴 중첩시간에서도 오방전이 발생하지 않고 기입 방전이 성공적으로 발생한다는 것을 확인할 수 있다. 전체 패널에서의 기입전압 마진은 그림 6(b)에서 보인바와 같이 측정된 세 가지 마진을 겹쳤을 때 맨 안쪽 영역을 가리킨다. 0 시간에서의 전압 레벨이 종래의 구동법에서의 최소 기입 전압인 반면에, 0.1 부터 0.8μs 시간까지의 중첩시간이 제안된 구동 방법에서의 최소 기입전압이다. 중첩된 시간이 0.5μs에서 최소 전압은 종래의 구동법과 비교해 볼 때, 약 13V 낮출 수 있었다. 최소 기입 전압을 낮춘다는 것은 기입 전극에 사용되는 데이터 IC 부품의 가격을 낮출 수 있고, 여러 패턴에서 얼마나 많은 기입 펄스가 사용되느냐에 따라 달라지겠지만 소비전력을 낮추는데도 기여할 것이다.

Ⅴ. 결 론

교류형 플라즈마 디스플레이 패널에서 기입 전압을 낮추기 위하여 기입 펄스의 폭은 유지하고 주사펄스의 폭만 늘이는 중첩 주사 구동방법이 제시되었다. 먼저 1μs의 기입 펄스폭에서 주사 시간동안의 최대와 최소 기입 전압이 측정되었고, 기입 전압을 60V로 고정하였을 때 기입 방전 지연시간이 측정되었다. 셀 내부에 프라이밍 입자와 벽전하의 소실에 의해 시간에 따라 기입 방전 지연시간은 늘어났다. 길어진 방전 지연시간을 이용하여 주사 전극의 파형끼리 중첩시켜 기입 방전이 안정적으로 발생하도록 하였고 그 결과 최저 기입 전압을 종래의 57V에서 44V로 약 13V 정도 더 낮출 수 있었다.

References

- L. F. Weber, "The Promise of Plasma Displays for HDTV", Proc. SID 00, p402-405, May), (2000.

-

H. D. Park, J. H. Kim, B. J. Shin, J. H. Seo, and H. S. Tae, "Improving luminous efficacy using dual sustain pulse waveform associated with short sustain pulse width in AC-plasma display panels", AIP Advances, 5(5), p057119, Jun), (2015.

[https://doi.org/10.1063/1.4921030]

-

S. S. Park, and B. G. Cho, "Improvement of Luminous Efficiency in AC Plasma Display Panel with Long Distance between Top Plate Electrodes", Journal of KIIT, 15(2), p41-46, Feb), (2017.

[https://doi.org/10.14801/jkiit.2017.15.2.41]

-

B. H. Lee, and I. S. Lee, "Development of a High –Capacity Power Supply Using IGBT for Plasma Devices", Journal of KIIT, 11(6), p25-32, Jun), (2013.

[https://doi.org/10.14801/kiitr.2013.11.6.25]

-

S. I. Park, J. S. Huh, W. S. Moon, D. H. Kim, and J. C. Kim, "Control Scheme Using Active Power Regulation for DC Voltage of VSC HVDC Under Unbalanced Voltage", Trans. KIEE, 64(2), p232-239, Feb), (2015.

[https://doi.org/10.5370/kiee.2015.64.2.232]

- T. Shinoda, M. Wakitani, T. Nanto, K. Yoshikawa, A. Ohtsuka, and T. Hirose, "Development of Technologies for Large-Area Color ac Plasma Displays", Proc. SID 93, p161-164, May), (1993.

- J. H. Yang, J. K. Kim, and K. W. Whang, "An energy recovery circuit for AC plasma display panel with series CLC resonance-SER1", IEEE Trans. Consumer Electronics, 51(2), p718-724, Jul), (2005.

- S. Yuji, T. Akihiro, and S. Yasuhiro, "A Study of Effective Power-Reduction Methods for PDP Address-Driver ICs by Applying a Power- Dispersion Scheme(Electronic Displays)", IEICE Trans Electronics, 86(8), p1774-1781, Aug), (2003.

1979년 2월 : 경북대학교 전자계산전공(공학사)

1984년 2월 : 일본 니혼대학교 전자공학과(공학석사)

1992년 2월 : 일본 도호쿠대학교 정보공학과(공학박사)

1986년 ~ 현재 : 부경대학교 컴퓨터공학과 교수

관심분야 : 컴퓨터네트워크, 네트워크관리, IPv6, IPTV, 컴퓨터시스템

2001년 2월 : 경북대학교 전자전기공학부(공학사)

2003년 2월 : 경북대학교 전자공학과(공학석사)

2006년 8월 : 경북대학교 전자공학과(공학박사)

2008년 3월 ~ 현재 : 부경대학교 융합디스플레이공학과 교수

관심분야 : 디스플레이 시스템, 고전압 회로, 영상정보시스템