디지털 주파수 고정 루프를 가지는 1 ~ 3.2 GHz 서브 샘플링 위상 고정 루프

초록

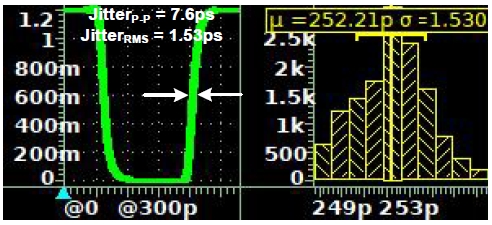

본 논문은 메모리 콘트롤러의 클록 발생기를 위해 1 ~ 3.2 GHz의 출력 주파수를 가지는 서브 샘플링 위상 고정 루프(SSPLL, Sub-Sampling Phase-locked Loop)를 제안한다. 설계된 SSPLL은 서브 샘플링 위상 검출기, 전하 펌프, 루프 필터, 전압 제어 발진기와 펄스 발생기로 구성되며, 넓은 범위의 출력 주파수를 가지는 클록을 생성하기 위하여 디지털 주파수 고정 루프가 추가된다. 20 MHz의 기준 클록을 사용하는 제안된 SSPLL은 1 MHz의 루프 대역폭을 가지기 위해 SSPD의 높은 이득을 줄이기 위한 CML 버퍼를 이용하며, 출력 클록의 주파수 변화에 따른 KVCO의 변화를 보상하기 위해 펄스 폭을 제어할 수 있는 펄스 발생기를 이용한다. 제안된 SSPLL은 1.2V의 공급 전압을 가지는 CMOS 65-nm 공정에서 설계된다. 제안된 SSPLL은 1.8 GHz 주파수를 가지는 클록을 출력할 때 8.92 mW의 전력을 소모하며, 각종 노이즈를 고려한 출력 클록의 피크-투-피크 타임 지터와 RMS 타임 지터는 각각 7.6 ps와 1.53 ps이다.

Abstract

This paper proposes a Sub-Sampling Phase-Locked Loop (SSPLL) with an output frequency range of 1 to 3.2 GHz for the clock generator of a memory controller. The proposed SSPLL consists of a Sub-Sampling Phase Detector (SSPD), a charge pump, a loop filter, a Voltage-Controlled Oscillator (VCO), and a pulse generator, and a digital frequency-locked loop is added to generate a clock with a wide output frequency range. The proposed SSPLL, using a 20 MHz reference clock, employs a CML buffer to reduce the high gain of the SSPD for a 1 MHz loop bandwidth. It also utilizes a pulse generator capable of controlling pulse width to compensate for changes in the KVCO due to variations in the output clock frequency. The proposed SSPLL is implemented in a 65‑nm CMOS process with a supply voltage of 1.2 V. When generating a 1.8 GHz clock, the SSPLL consumes 8.92 mW of power, and the peak-to-peak and RMS time jitters of the output clock, considering various noise sources, are 7.6 ps and 1.53 ps, respectively.

Keywords:

clock generator, sub-sampling phase-locked loop, digital frequency-locked loop, sub-samping phase detector, pulse generatorⅠ. 서 론

최근 모바일과 인공지능 기술이 급속히 발전함에 따라, 데이터 센터와 프리미엄 모바일, 그래픽 시스템 등 주요 분야에서는 대용량 데이터를 빠르게 저장하고 처리할 수 있는 능력이 필수적으로 요구되며, 고대역폭, 저지연, 고용량, 고신뢰성 스토리지 기술의 중요성이 더욱 커지고 있다[1]. 메모리는 데이터를 저장하고 전달하여 프로세서가 효율적으로 연산을 수행하게 돕는 핵심 요소로, 메모리 성능 향상은 시스템 전체 정보 처리 속도 개선에 크게 기여한다. 메모리 업계는 요구되는 기술들을 만족하기 위하여 메인 메모리, 모바일 메모리, 그리고 그래픽 메모리의 DRAM은 핀당 800 ~ 2133 MT/s의 전송 속도를 지원하는 DDR3 및 핀당 1600 ~ 3200 MT/s의 전송 속도를 DDR4 등 메모리의 고속화를 진행하며[2], 메모리 컨트롤러를 포함하는 고속의 메모리를 지원하는 시스템에서는 고속 동작을 지원하면서 저잡음 특성을 가지는 클록 발생기가 필요하다. 기존의 전하 펌프 위상 고정 루프(CPPLL, Charge Pump Phase-Locked Loop)는 낮은 기준 주파수 환경에서 높은 출력 주파수를 만들기 위해 큰 분주 비를 사용할 경우, 위상 잡음을 악화시켜 성능 저하를 초래한다[3]. 본 연구에서는 높은 분주 비로 인한 위상 잡음의 악화 문제를 해결하기 위해 높은 분주 비를 제거할 수 있는 서브 샘플링 위상 고정 루프(SSPLL, Sub-Sampling Phase-Locked Loop)를 구현한다. 피드백 루프에서 주파수 분주를 하지 않는 구조의 SSPLL은 좁은 범위의 출력 주파수를 생성한다[4][5]. 메모리 경우, 한 제품에서 지원하는 주파수 대역이 최소 주파수 대비 2배 이상의 최대 주파수를 지원한다. 따라서, 본 논문은 20 MHz의 주파수를 가지는 기준 클록에 대해 1 ~ 3.2 GHz의 주파수를 가지는 클록을 생성하면서 저잡음 특성을 유지하는 SSPLL을 설계한다.

Ⅱ. 디지털 FLL이 포함된 SSPLL의 설계

기존 SSPLL은 주파수 체배를 수행하는 경우 출력 클록에 대한 피드백에서 주파수 분배 없이 VCO의 동작 주파수 범위를 매우 좁게 설계하고 위상 locking 동작을 통해 일반적인 PLL의 동작을 수행한다[3]. 이를 통해 PLL의 출력 클록에 대해 주파수 분배로 인한 노이즈 발생을 최소화되지만, SSPLL의 주파수 locking 범위가 좁게 결정된다. 따라서, 기존 SSPLL은 CPPLL의 구조를 사용하여 주파수 고정 루프(FLL, Frequency Locked Loop)를 추가한다. CPPLL을 사용한 FLL은 단일 혹은 좁은 범위의 주파수를 찾아갈 수 있도록 하여, dead zone이라고 불리는 블록으로 주파수 고정 루프를 끊은 후, 위상을 쫓아갈 수 있도록 한다.

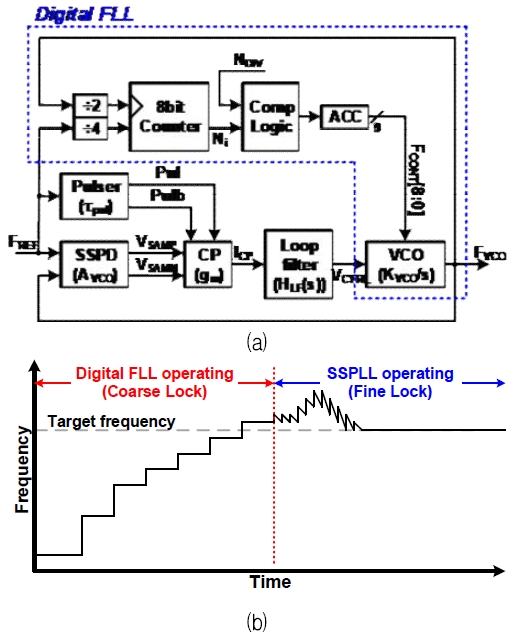

본 논문에서 제안하는 SSPLL은 그림 1(a)와 같이 기본적으로 서브 샘플링 위상 검출기(SSPD, Sub-Sampling Phase Detector), 전하 펌프(CP, Charge Pump), 펄스 발생기(Pulser), 루프 필터(Loop filter), 그리고 전압 제어 발진기(VCO, Voltage Controlled Oscillator)로 구성된 SSPLL의 구조를 기반으로 한다. SSPLL의 전달함수 H(s)는 식 (1)과 같이 나타나는데, 일반 전하 펌프 PLL과 달리 주파수 체배에 대한 영향은 포함되지 않는다[3].

| (1) |

여기서, HLF(s)와 KVCO는 각각 루프 필터의 전달함수와 VCO의 이득이다. 그리고, βSSPD,CP는 SSPD와 CP의 이득이며 식 (2)와 같이 나타난다.

| (2) |

여기서, AVCO는 SSPD의 이득이며, gm은 입력 전압을 전류로 변환하는 CP의 트랜스-컨덕턴스이다. 또한, τpul은 pulser 블록에서 생성하는 펄스의 폭이며, TREF는 입력 기준 클록의 주기이다. 제안된 SSPLL의 넓은 출력 주파수의 범위를 지원하기 위해 KVCO의 값이 일정하게 유지되지 못할 수 있는데, 이 경우 H(s)의 stability는 βSSPD,CP의 제어를 통해 확보가 가능하게 한다.

그림 1(b)는 넓은 범위의 출력 주파수를 가지는 클록을 생성하기 위해 디지털 FLL이 추가된 제안된 SSPLL의 동작의 개념을 보여준다. 제안된 SSPLL은 먼저 digital FLL의 동작을 통해 목표 주파수를 주파수에 대한 coarse locking을 수행한다. 이후 기존의 SSPLL의 동작을 통해 출력 클록에 대해 별도의 주파수 분주 없이 SSPD로 피드백함으로 주파수 체배로 인한 출력 클록의 잡음 증가가 되지 않도록 한다.

2.1 전압 제어 발진기

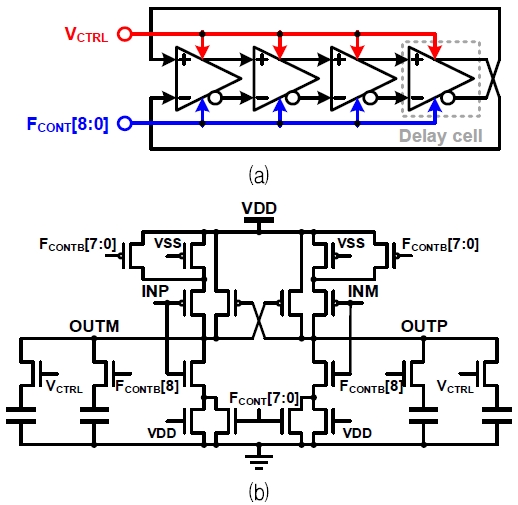

그림 2(a)에 나타난 VCO는 4단 지연 셀로 구현된다. 각 지연 셀은 그림 2(b)의 회로도로 구현되는데, VCO의 넓은 발진 주파수를 제어하기 위해 coarse tuning과 fine tuning을 위한 신호를 입력받는다. VCO를 위한 coarse tuning 신호는 8비트 디지털 신호(FCONT[8:0])이고 fine tuning 신호는 루프 필터에서 출력되는 제어 전압(VCTRL)이다. Coarse tuning을 위한 FCONT[8:0]는 디지털 FLL에서 생성된다. FCONT[7:0] 코드는 지연 셀의 가변 저항 역할을 하는 스위치를 구동하는 신호로 사용되어 PMOS와 NMOS 트랜지스터의 게이트에 인가된다. 각 트랜지스터는 스위치처럼 동작하여 입력값에 따라 온저항이 결정되고, 이 저항들이 병렬로 연결되어 각 지연 셀의 전류가 변화되어 결과적으로 VCO 발진 주파수가 조절된다. FCONT[8] 코드는 각 지연 셀 출력단에 접속된 커패시터의 크기를 제어함으로 VCO의 발진 주파수 coarse tuning이 가능하게 한다. Fine tuning을 위한 제어 전압(VCTRL)은 각 지연 셀의 출력단의 커패시터와 직결된 NMOS 트랜지스터 게이트에 공급되어 전압의 변화를 통해 VCO의 주파수를 세밀하게 제어한다.

2.2 디지털 주파수 고정 루프

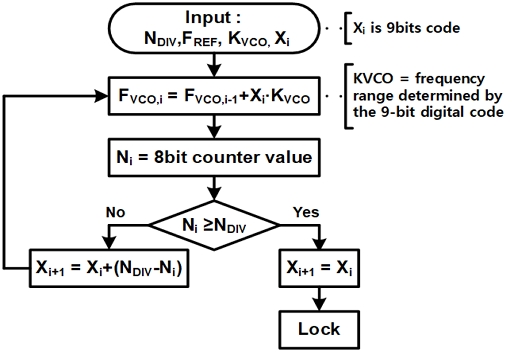

VCO는 넓은 출력 주파수 범위를 위해 전류를 제어하는 코드와 부하를 제어하는 FCONT[8:0] 코드를 입력받는데, 이 코드들은 디지털 방식으로 구현된 FLL을 통해 생성된다. 설계된 FLL은 그림 1(a)의 digital FLL 블록과 같이 기준 클록(FREF)과 VCO 출력 클록(FVCO)을 각각 4와 2로 분주한 신호를 비교·연산하여 최종적으로 9비트 제어 코드 FCONT[8:0]을 출력한다. 기준 신호와 VCO 출력 신호는 각각 8비트 카운터의 데이터와 클록 신호로 입력되며, 기준 신호가 ‘1’일 때 카운터 값이 출력되고, 이는 비교 로직으로 전달되어 분주 비와 비교된다. FLL의 동작 순서는 그림 3에 자세히 나타나 있다[6]. FVCO 수식의 KVCO는 FCONT[8:0]에 따른 VCO 주파수 변화를 의미하며, FLL 동작 중에는 VCO 제어 전압 VCTRL가 1/2∙VDD로 고정되어 주파수 루프만으로 동작한다.

설계된 FLL은 8비트 카운터 값 Ni와 입력된 분주 비 NDIV 간의 차이를 이득으로 설정하여, 바이너리 출력 코드가 초기값 0에서 시작할 때 비교적 높은 이득으로 빠르게 목표 주파수에 근접하도록 하고, 이후 차이가 줄어들면 이득을 감소시켜 세밀하고 안정적으로 목표 주파수에 도달할 수 있도록 한다. 특히, 디지털 방식으로 구현된 FLL은 주파수 설정을 코드화함으로써 기존 아날로그 중심 FLL 대비 훨씬 넓은 캡처 및 추적 범위를 제공한다. 이를 통해 초기 주파수 오프셋이 큰 경우에도 빠르고 안정적인 주파수 획득이 가능하며, 주파수 변환도 용이하다. 또한, 디지털 구현은 알고리즘 변경과 최적화가 용이하고, 공정 이식성과 재사용성이 뛰어나다. 결과적으로, 디지털 FLL 구조는 PLL 본루프가 정밀 위상 정합에 집중할 수 있도록 하여 전체 락 시간을 단축하고 저지터 클록을 생성할 수 있게 하며, 넓은 출력 주파수 범위와 높은 안정성을 동시에 확보한다.

2.3 서브 샘플링 위상 검출기

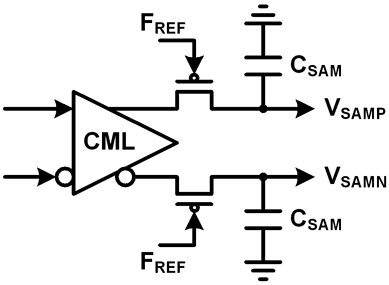

SSPD는 그림 4와 같이 전류 모드 논리(CML, Current Mode Logic) 버퍼와 금속-절연체-금속(MIM, Metal-Insulator-Metal) 커패시터, 그리고 PMOS 트랜지스터로 구성된다. SSPD는 기본적으로 트랙(Track)과 홀드(Hold) 두 모드를 수행한다. 기준 신호(FREF)가 low 상태일 때는 트랙 모드로 동작하여, SSPD 출력이 CML 출력 신호를 따른다. 홀드 모드에서 FREF가 high 상태로 전이하는 상승 에지에서는 해당 시점의 위상 전압이 샘플되어 유지된다. SSPLL의 SSPD는 입력 클록의 전압값을 샘플하여 출력하기 때문에 입력되는 신호의 진폭과 기울기가 가파를수록 높은 이득 특성을 가진다. 따라서, SSPD가 포함된 전하 펌프 이득을 줄이기 위하여 CML 버퍼를 추가하여 식 (2)에 나타난 SSPD에 입력되는 신호의 기울기인 AVCO를 줄인다[7]. CML 버퍼는 SSPD에 입력되는 신호의 상승 및 하강의 시간을 증가함으로 루프 필터의 커패시터 크기를 줄여 면적 효율을 높이고, 동시에 목표 루프 대역폭의 구현을 용이하게 한다.

2.4 펄스 발생기

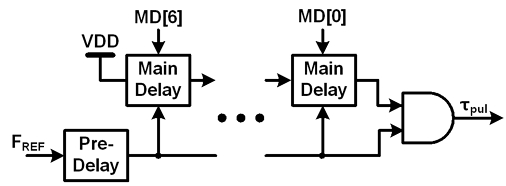

그림 5는 설계된 pulser의 블록도이다. Pulser는 하나의 pre-delay 블록과 7개의 main delay 블록으로 구성된다. Pulser는 SSPD가 홀드 모드에서 동작할 때, 일정 시간 동안 전하 펌프가 루프 필터의 전하를 더하거나 뺄 수 있도록 τpul의 펄스 폭을 가지는 신호를 발생시킨다. 제안하는 SSPLL의 넓은 주파수를 대역을 가지는 클록을 생성하는데, 동작 주파수에 따라 일정하지 못한 KVCO에 대해 안정적인 PLL의 동작을 확보하기 위해 pulser는 7 bits의 제어 코드에 따라 τpul의 값을 결정한다. 또한, SSPD는 홀드와 트랙 모드를 수행할 때, 스위치에 의존하여 동작한다. 스위칭 동작은 샘플된 전압에 순간 잡음을 주며, 발생된 잡음을 제거하기 위하여 pre-delay 블록을 통해 펄스폭이 출력되는 시간을 지연한다.

Ⅲ. SSPLL 구현 및 시뮬레이션 결과

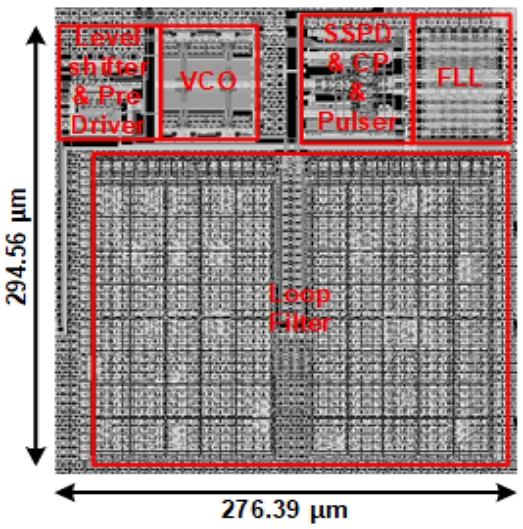

그림 6은 CMOS 65nm 공정으로 구현된 디지털 FLL이 포함된 SSPLL의 레이아웃이다. 제안된 SSPLL은 276.39 μm × 294.56 μm의 면적을 가진다. 그 중, 디지털 FLL과 VCO는 각각 42.98 μm × 64.33 μm와 64.7 μm × 79.8 μm를 차지한다. 그리고 SSPD, CP, 그리고 pulser는 58.645 μm × 75.08 μm의 면적을 가진다. Level shifter와 pre-driver는 45.195μm × 50.775 μm의 면적을 가며며, 루프 필터는 265.96 μm × 209.88 μm로 가장 큰 비중을 차지한다.

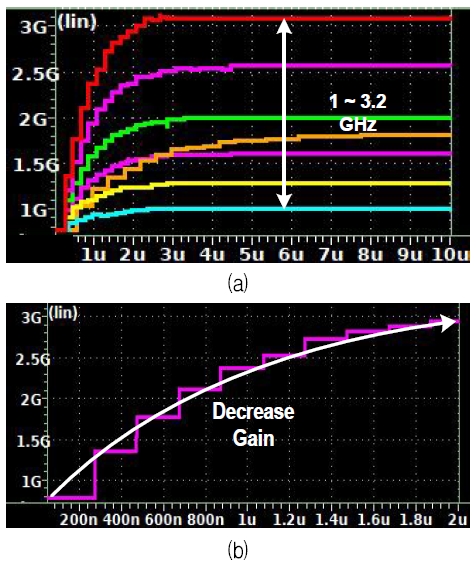

설계된 SSPLL은 1.2V의 공급 전압으로 사용하는 CMOS 65nm 공정에서 설계되었다. 또한, 설계된 SSPLL이 20 MHz의 주파수를 가지는 기준 클록에 대해 1.8 GHz의 주파수를 가지는 클록을 출력할 때 8.92 mW의 전력을 소모한다. 그림 7(a)는 FLL에 입력되는 분주 비를 변화함에 따라 출력되는 클록의 주파수를 보여주는데, 1 ~ 3.2 GHz의 범위를 가진다. 그림 7(b)는 FLL 동작 중 초기에 큰 이득을 가지고 시작하여 이득이 감소하며 세밀하게 목표 주파수를 찾아가는 것을 보여준다. 그림 8은 transient noise 포함한 post-layout simulation의 결과로써 설계된 SSPLL의 타임 지터 특성을 보여준다. SSPLL이 1.8 GHz의 출력 주파수를 가지는 클록을 생성할 때, peak-to-peak 타임 지터는 7.6 ps이며, RMS 타임 지터는 1.53 ps이다. 표 1은 본 논문에서 설계한 SSPLL과 유사한 사양을 가지는 PLL과의 특성을 비교하여 보여준다. 표 2는 기존 발표된 SSPLL과 제안된 SSPLL의 동작 주파수 범위를 포함한 특성들을 비교한다. 제안된 SSPLL은 디지털 FLL의 사용으로 넓은 주파수를 가지는 클록을 생성하면서도 SSPLL의 특성에 따라 우수한 타임 지터의 특성을 가진다.

Simulation result of FLL (a) Operating frequency range (b) Gain change according to operating frequency

Ⅳ. 결 론

본 논문에서 제안된 SSPLL은 1.2V 공급 전압 기반 CMOS 65nm 공정에서 설계되었으며, 반도체 칩으로 제작되어 평가될 예정이다. 제안된 SSPLL은 20 MHz의 주파수를 가지는 기준 클록을 가지고 디지털 FLL을 통해 1 ~ 3.2GHz의 넓은 출력 주파수 범위를 지원한다. 또한, 1.8GHz 출력 시 각각 7.6ps 피크-투-피크 타임 지터와 1.53ps RMS 타임 지터의 특성을 가짐으로 안정적인 클록 을 생성한다. 또한, 디지털 FLL을 채택함으로 기존 SSPLL 대비 넓은 캡처 및 추적 범위를 가진다.

Acknowledgments

이 연구는 국립금오공과대학교 대학 연구과제비(2024~2025)와 2025년도 교육부 및 경상북도의 재원으로 경북RISE센터의 지원을 받아 수행된 지역혁신중심 대학지원체계(RISE)-(지역성장 혁신LAB)의 결과입니다.(2025-rise-15-105)

References

-

G. Le, V. T. Hoang, S. Ferdousi, A. Marotta, S. Xu, and Y. Hirota, "Reliable Provisioning of Low-Latency and High-Bandwidth Extended Reality Live Streams", IEEE Journal on Selected Areas in Communications, Vol. 43, No. 5, pp. 1755-1766, May 2025.

[https://doi.org/10.1109/JSAC.2025.3543502]

-

H.-H. Kim, H. Lee, and Y.-C. Jang, "Design of Transceiver for LPDDR3 Memory Controller using POD Interface", Journal of Korean Institute of Information Technology, Vol. 23, No. 8, pp. 45-58, Aug. 2025.

[https://doi.org/10.14801/jkiit.2025.23.8.45]

-

X. Gao, E. A. M. Klumperink, M. Bohsali, and B. Nauta, "A Low Noise Sub-Sampling PLL in Which Divider Noise is Eliminated and PD/CP Noise is Not Multiplied by N2", IEEE Journal of Solid-State Circuits, Vol. 44, No. 12, pp. 3253-3263, Dec. 2009.

[https://doi.org/10.1109/JSSC.2009.2032723]

-

A. T. Narayanan, M. Katsuragi, K. Kimura, S. Kondo, K. K. Tokgoz, K. Nakata, W. Deng, K. Okada, and A. Matsuzawa, "A Fractional-N Sub-Sampling PLL using a Pipelined Phase-Interpolator With an FoM of –250 dB", IEEE Journal of Solid-State Circuits, Vol. 51, No. 7, pp. 1630-1640, Jul. 2016.

[https://doi.org/10.1109/JSSC.2016.2539344]

-

T.-S. Yang, H.-Y. Hsieh, and L.-H. Lu, "A 2.4-GHz Ring-VCO-Based Sub-Sampling PLL With a −70-dBc Reference Spur by Adopting a Capacitor-Multiplier-Based Sub-Sampling DLL", IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 70, No. 9, pp. 3545-3556, Sep. 2023.

[https://doi.org/10.1109/TCSI.2023.3284294]

-

C.-C. Hung, I.-F. Chen, and S.-I. Liu, "A 1.25GHz Fast-Locked All-Digital Phase-Locked Loop with Supply Noise Suppression", Proc. 2010 International Symposium on VLSI Design, Automation and Test, Hsinchu, Taiwan, pp. 237-240, Apr. 2010.

[https://doi.org/10.1109/VDAT.2010.5496733]

-

S. S. Nagam and P. R. Kinget, "A Low-Jitter Ring-Oscillator Phase-Locked Loop Using Feedforward Noise Cancellation With a Sub-Sampling Phase Detector", IEEE Journal of Solid-State Circuits, Vol. 53, No. 3, pp. 703-714, Mar. 2017.

[https://doi.org/10.1109/JSSC.2017.2788876]

-

J.-H. Bae, "Low-Power Spread Spectrum Clock Generation and Tracking PLLs for High-Speed Serial Links", Master’s thesis, Sungkyunkwan University, 2012.

[https://doi.org/10.23185/skku.000000039609.11040.0010617]

-

Y.-C. Huang, C.-F. Liang, H.-S. Huang, and P.-Y. Wang, "A 2.4GHz ADPLL with digital-regulated supply-noise-insensitive and temperature-self-compensated ring DCO", IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, pp. 270-271, Feb. 2014.

[https://doi.org/10.1109/ISSCC.2014.6757430]

2024년 2월 : 국립금오공과대학교 전자공학부(공학사)

2024년 2월 ~ 현재 : 국립금오공과대학교 반도체시스템공학과(공학석사과정)

관심분야 : 클록 발생기 포함 고속 인터페이스 회로

2020년 3월 ~ 현재 : 국립금오공과대학교 전자공학부 공학학사과정

관심분야 : 디지털 위상 고정 루프 포함 클록발생기

1999년 2월 : 경북대학교 전자전기공학부(공학사)

2001년 2월 : 포항공과대학교 전자공학과(공학석사)

2005년 2월 : 포항공과대학교 전자공학과(공학박사)

2005년 3월 ~ 2009년 8월 : 삼성전자 반도체총괄 책임연구원

2009년 9월 ~ 현재 : 국립금오공과대학교 전자공학부 교수

관심분야 : 아날로그-디지털 변환기 및 고속 인터페이스를 위한 클록발생기와 송수신기 포함 아날로그집적회로