POD 인터페이스 이용 LPDDR3 메모리 컨트롤러를 위한 송수신기 설계

초록

본 연구에서는 LPDDR3(Low-Power Double Data Rate 3) 메모리의 컨트롤러의 물리계층(PHY, Physical layer)를 위한 POD(Pseudo-Open Drain) 방식의 인터페이스를 지원하는 송수신기가 제안된다. 송신기는 임피던스 보정기를 통해 목표 임피던스를 제어하며, 전하-펌프 위상고정루프(CPPLL, Charge-Pump Phase-Locked Loop)를 이용하여 데이터(DQ)와 데이터 스트로브(DQS) 신호는 서로 90도의 위상 차이를 가지는 신호를 출력한다. Coupling capacitor와 연속시간 선형등화기(CTLE, Continuous-Time Linear Equalizer)를 이용하는 수신기는 POD 인터페이스의 수신되는 단일-종단 신호의 전압 및 시간 마진을 개선한다. 또한 read-time 보정 회로는 채널간 및 DQS와 DQ 간의 시간 스큐를 제거한다. 제안된 LPDDR3 메모리 컨트롤러 송수신기는 1.2V 공급 전압의 55nm CMOS 공정을 이용하여 설계되었으며, 1037.5 Mbps/pin에서 1867.5 Mbps/pin의 데이터 전송 속도를 지원한다.

Abstract

In this paper, a transceiver with a Pseudo-Open Drain (POD) interface is proposed for the Physical layer (PHY) of the controller of a Low-Power Double Data Rate 3 (LPDDR3) memory (DRAM). The transmitter uses an impedance calibrator to control the target impedance and a Charge-Pump Phase-Locked Loop (CPPLL) to output data (DQ) and data strobe (DQS) signals with a 90-degree phase difference between them. The receiver uses a coupling capacitor and a Continuous-Time Linear Equalizer (CTLE) to improve the voltage and time margins of the received single-ended signal of the POD interface. In addition, read-time calibration circuit eliminates time skew between channels and between DQS and DQ. The proposed LPDDR3 memory controller transceiver is designed using a 55 nm CMOS process with a 1.2 V supply voltage and supports data transfer rates from 1037.5 Mbps/pin to 1867.5 Mbps/pin.

Keywords:

LPDDR3, memory controller, transmitter, receiver, pseudo-open drain interfaceⅠ. 서 론

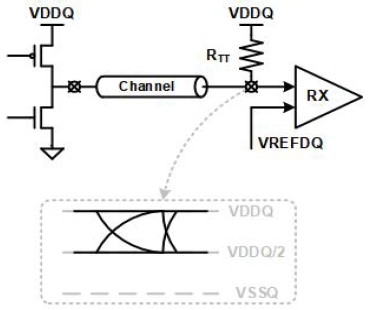

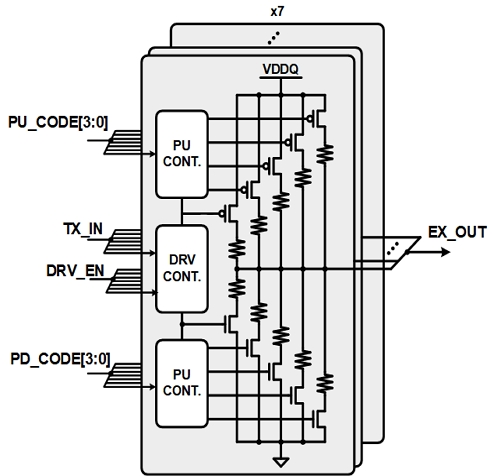

모바일 기기의 발전은 대량 데이터 처리와 저전력 동작을 동시에 요구함에 따라, 모바일용 메모리의 성능 개선이 필수적으로 대두되고 있다[1]. 특히 통신 성능을 좌우하는 메모리 인터페이스의 중요성이 지속적으로 증가하고 있으며, 이에 반도체 공학 표준화 기구인 JEDEC(Joint Electron Device Engineering Council)에서는 기존 DDR 기술을 모바일 환경에 특화된 LPDDR(Low-Power Double Data Rate)를 표준으로 규격화하였다. LPDDR3는 1333 Mbps/pin에서 1600 Mbps/pin의 데이터 전송 속도를 지원하고 있는데[2], 최근에는 메모리 제조사에서 2133 Mbps/pin까지 지원하고 있다[3]. JEDEC 기준으로 1600 Mbps/pin까지는 HSUL(High-Speed Unterminated Logic) 인터페이스를 적용하여 사용한다. 그러나 1600 Mbps/pin의 데이터 전송률 이상으로 데이터 속도가 증가할 경우, HSUL 기반 신호 전송 시 ISI(Inter-Symbol Interference)가 증가하는 등 신호 품질 열화 문제가 발생된다[4]. 이에 따라, 1600 Mbps/pin 이상의 데이터 전송 속도를 가지는 LPDDR3의 경우, POD(Pseudo-Open Drain) 인터페이스를 적용하여 신호 품질을 개선할 수 있다. 그림 1에 나타난 POD 인터페이스는 데이터 라인에 VDDQ에 연결된 종단저항이 존재하며, 풀-업과 풀-다운이 존재하는 출력 드라이버로 구성된다. 출력 드라이버의 구조는 풀-업 소자와 풀-다운 소자, 종단저항이 모두 동일한 값으로 설정되어, 오픈 드레인(Open drain) 구조와 같이 동작한다. 이는 송신 드라이버의 풀-업이 켜지는 경우, 풀-업과 종단저항이 모두 VDDQ로 연결되어 전류 경로가 생성되지 않고 VDDQ를 출력한다. 송신 드라이버의 풀-다운이 활성화되는 경우, VDDQ에서 접지(GND)로 전류의 경로가 형성되어 전압 분배가 이루어져서 VDDQ/2의 전압이 출력된다. 한편, LPDDR3의 인터페이스를 이용하는 메모리를 제어하는 컨트롤러는 메모리보다 신호 보존성 특성 측면에서 더욱 우수한 송수신기의 설계가 요구된다. 특히, 컨트롤러는 메모리와의 양방향 데이터 교환 과정에서 여러 DQ 사이, 그리고 DQ와 DQS 신호 사이 타임 스큐(Time skew)의 제거, 드라이버 임피던스 보정 등 송수신기에 대한 신호 무결성의 보장이 요구된다.

본 연구에서는 ×16 데이터를 송수신하기 위해 LPDDR3를 지원하는 메모리 컨트롤러를 위한 송수신기를 설계한다. 구현되는 송수신기는 메모리 컨트롤러에 사용되기 위해 높은 신호 보존성이 요구된다. 이에 따라 표 1에서 보인 바와 같이 단일 종단 신호(Single-ended signal)로 전송되는 데이터의 전송 속도는 1037.5 Mbps/pin에서 1867.5 Mbps/pin 범위를 가지며, 데이터 전송 속도에 따른 신호의 질을 고려하여 POD 인터페이스를 적용하여 구현한다.

Ⅱ. 송수신기의 전체 구조

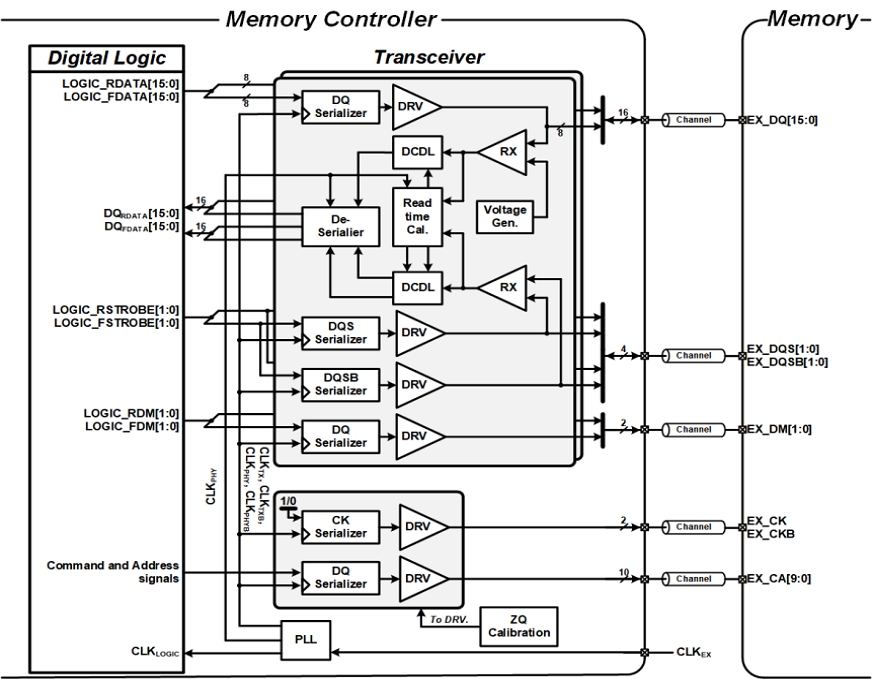

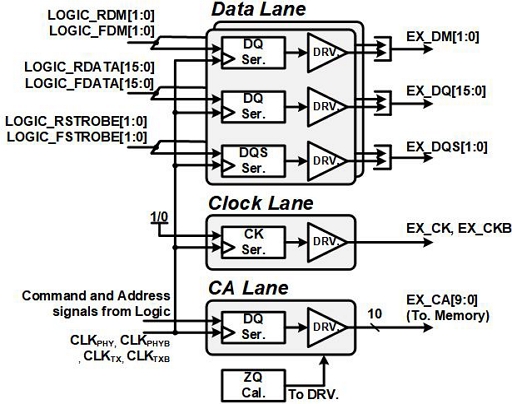

그림 2는 본 연구에서 설계한 LPDDR3 메모리 컨트롤러를 위한 송수신기의 전체 블록도를 보여준다. 메모리 컨트롤러의 송수신기는 메모리와 양방향으로 데이터를 송수신하며, 메모리를 제어하기 위한 명령 및 주소 신호를 송신한다.

또한, 디지털 로직과의 인터페이스를 통해 수신된 데이터를 전달하거나, 메모리에 기록할 데이터를 전달받는 역할을 수행한다. 전체 송수신기는 총 16개의 DQ와 두 쌍의 DQS 신호를 처리하도록 구성된다. 이때 하나의 바이트(byte)는 8개의 DQ 신호와 한 쌍의 DQS 신호를 송수신하며, 이를 두 그룹 배치하여 총 두 바이트(×16)를 가진 송수신기를 구현한다.

송수신기는 기능에 따라 크게 두 개의 블록으로 나누어진다. 수신단은 메모리로부터 수신한 데이터를 처리하여 후단의 디지털 로직에 전달하는 읽기동작을 담당하며, 송신단은 디지털 로직에서 받은 데이터를 메모리로 전달하는 쓰기 동작을 수행한다. 각 바이트 단위의 송수신기에는 기준 전압 생성기(Reference voltage generator)와 read-time 보정 회로가 각각 존재한다. 특히, read-time 보정 회로는 DQS 신호가 DQ의 값을 저장할 때 충분한 셋업 및 홀드시간을 확보하도록 위상을 조정하며, 수신된 DQS 신호의 질을 고려하여 POD 인터페이스를 적용하며, 단일 종단 신호로 전송되는 데이터의 전송 속도는 1037.5 Mbps/pin에서 1867.5 Mbps/pin 범위를 갖는다.

Ⅲ. 읽기 동작을 위한 수신단 설계

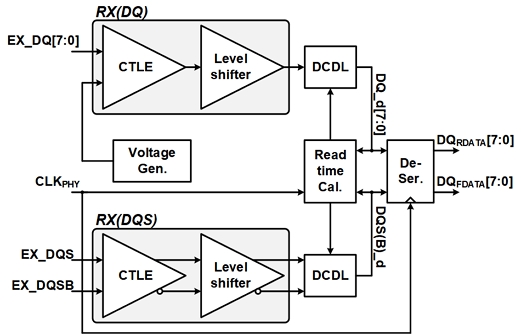

수신단은 메모리로부터 전달받는 읽기 동작을 수행하며, 그림 3과 같이 수신기(Receiver), DCDL (Digital Controlled Delay Line), 역직렬화기(De-serializer), R-2R DAC(Digital-to-Analog Converter), 그리고 read-time 보정 회로로 구성된다. 단일 종단 신호로 입력되는 DQ 신호의 수신을 위한 수신기는 기준 전압 생성기의 출력인 기준 전압과의 비교를 통해 수신 동작을 수행하며, DQS를 위한 수신기는 입력되는 차동 신호를 서로 비교함으로 수신 동작을 수행한다. 그리고 POD 구조의 인터페이스를 이용하여 신호가 공급 전압부터 그 절반까지의 진폭을 가지며 입력되기 때문에, 이를 공급 전압부터 접지까지의 레벨을 가지도록 변환하는 과정이 level shifter 블록에서 수행된다.

메모리는 그의 읽기 타이밍으로 맞춰 수신된 EX_CK의 상승 에지에 정렬하여 DQ와 DQS를 출력한다. 따라서, 메모리 컨트롤러는 데이터의 샘플을 위하여 DQ를 기준으로 DQS에 대해 90도 시간 지연이 요구된다.

Read-time 보정 회로는 입력되는 DQ, DQS, 그리고 클록(CLKPHY) 간의 위상 관계를 조정한다. 이 회로는 DQS 신호를 DQ의 유효 데이터 창(Valid data window) 중앙으로 이동시켜 역직렬화기에 사용되는 플립플롭(F/F)의 셋업 시간과 홀드 시간을 최대한 확보하도록 한다. 또한, DQS와 CLKPHY를 정렬하여 동일 위상의 클록(CLKLOGIC)을 입력받는 디지털 로직과 동기화된 동작을 가능하게 한다.

DCDL은 read-time 보정 회로에서 출력된 코드를 기반으로 DQ와 DQS 신호의 시간 지연을 조정하며, 이를 통해 각 신호의 시간 지연을 정밀하게 제어한다. 이후, 역직렬화기는 직렬화 과정을 거쳐 수신된 DQ를 DQS 및 DQSB를 기준으로 복원하여 직렬화 이전의 병렬 데이터 형태로 변환한 뒤, 병렬 데이터를 디지털 로직으로 전달한다.

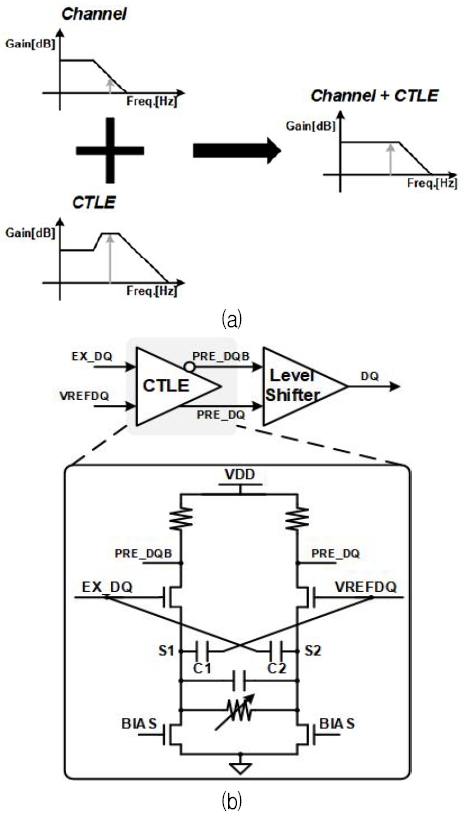

3.1 수신기

신호가 채널을 통하여 송수신되는 동안, 신호는 본래 송수신하고자 하였던 신호의 질을 유지하지 못하고, 고주파로 갈수록 그 질이 악화한다. 이는 채널이 저대역 통과 필터와 같은 역할을 하기 때문이다. 등화기(Equalizer)는 채널을 통해 입력되는 신호의 고주파 손실과 ISI 등의 왜곡을 보상하는 동작을 수행한다. 등화기는 송신단과 수신단에서 각각 사용될 수 있으며, 송신단에서는 채널의 고주파 손실을 미리 보상하여 수신단에서의 신호 복원을 용이하게 한다. 수신기의 등화기를 위해 사용된 선형등화기(CTLE, Continuous-Time Linear Equalizer)는 고속 데이터 전송 환경에서 그림 4(a)와 같이 목표 주파수 대역 내 고주파 영역의 이득을 증폭하여 채널 손실로 인한 고주파 감쇠 및 ISI를 효과적으로 보상할 수 있다. 또한, 아날로그 필터 기반으로 실시간 처리가 가능하며, 적응형 설계를 통해 다양한 채널 조건에 대응할 수 있다는 장점이 있다. DQ가 단일 신호 형태로 입력되므로, DQ들의 값을 판별하기 위한 기준 전압을 별도로 입력받아야 한다. 이 경우, 기존의 완전 차동 구조로 출력 신호를 생성하는 데 어려움이 발생한다. 이를 해결하기 위해 본 연구에서는 그림 4(b)에서 보이는 것처럼 입력 노드를 CTLE 입력 트랜지스터의 소스(Source) 노드와 커패시터(Capacitor)를 통해 교차 연결한다. 이러한 구조를 통해 두 입력 트랜지스터의 드레인(Drain)이 차동 출력을 효과적으로 생성한다. CTLE 회로에 의해 생성된 완전 차동 출력 신호는 level shifter에 입력되어 원하는 전압 레벨로 변환된다.

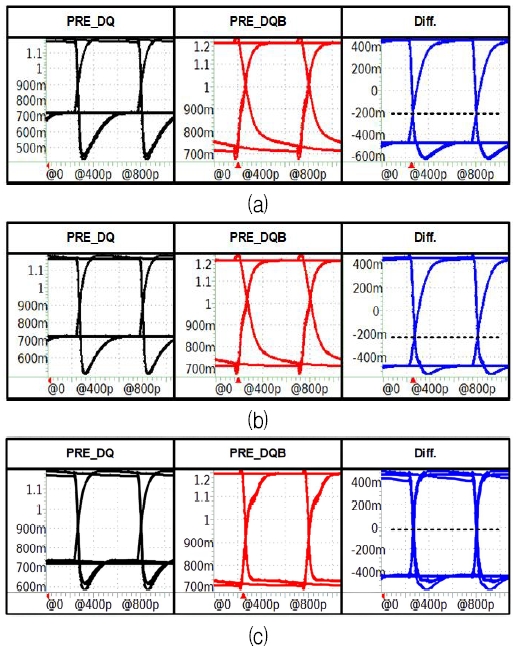

그림 5는 3가지의 CTLE 구조에 대하여 transient 시뮬레이션을 진행한 결과이다. 이들은 각각 PRE_DQ, PRE_DQB와 두 신호의 차동 신호에 대한 아이 다이어그램을 보여준다. 그림 5(a)는 C1은 제거하고 EX_DQ와 S2 사이에 C2 연결한 구조에 관한 결과이다. 이 구조에 대한 차동 신호의 아이 다이어그램을 확인하면 두 차동 출력의 교차 전압이 약 –200mV 정도 변하였다. 그림 5(b)의 경우, 동일하게 C1은 제거하고 EX_DQ와 S1 사이에 C2를 배치하여 얻은 결과이다[5]. 이 경우도 앞선 구조와 비슷한 결과를 보이며 차동 신호에 왜곡이 발생한다. 그림 4(b)와 같이 본 연구에 적용된 CTLE에 대한 시뮬레이션 결과는 그림 5(c)에 보여준다. 차동 신호의 아이 다이어그램에서 교차 전압이 거의 차동적으로 0V에 위치하는 것을 볼 수 있고, 구현된 CTLE는 그림 5(a)와 (b)의 구조에 비하여 두 입력을 차동 신호로 출력하고 있음을 보여준다.

3.2 Read-time 보정 회로

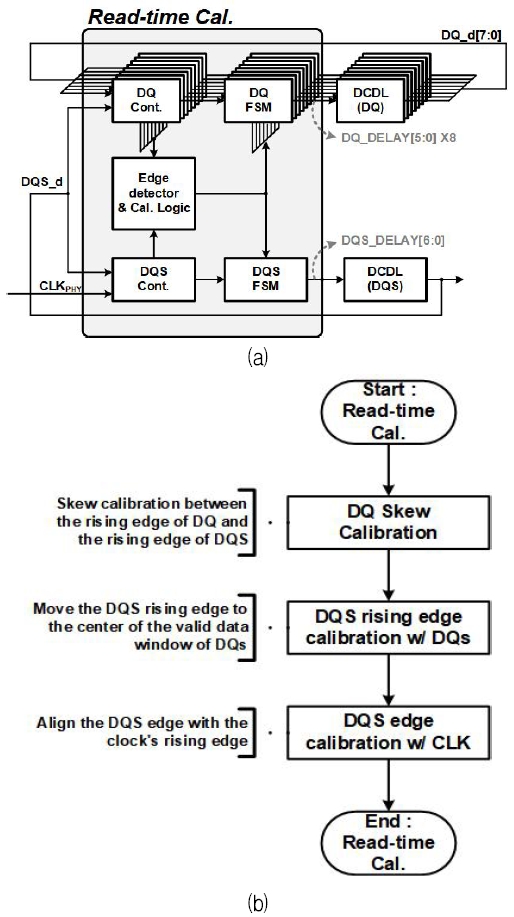

Read-time 보정 회로는 8bit의 DQ, 하나의 DQS와 하나의 CLKPHY가 입력되어 각 신호 간의 타임 스큐를 보정한다. 본 회로는 그림 6(a)의 블록도와 같이 에지 감지기(Edge detector)와 DQ와 DQS를 위한 제어 블록(DQ & DQS Cont.) 및 유한 상태 기계(DQ & DQS FSM)로 구성하여 앞서 언급한 동작을 수행한다. 그림 6(b)는 read-time 보정의 전체 순서이다. 보정이 시작되면, DQ들의 상승 에지는 수신단으로 입력되면서 발생한 각 DQ 별 시간 지연을 DQS의 상승 에지 기준으로 보정하는데, DQ들과 DQS는 상승 에지에 정렬되어 들어오기 때문이다.

이후, DQS의 상승 에지는 수신단에서 DQ 신호를 수신하기 위해 90도 시간 지연을 진행한다. 마지막으로, DQS의 에지를 역직렬화기의 동기화를 위해 CLKPHY의 상승 에지에 정렬하여 클록 도메인 변환한다.

참고문헌[6]에 발표된 LPDDR2를 위한 메모리 컨트롤러에 존재하는 read-time 보정 회로는 각 DQ 지연을 위한 컨트롤러와 하나의 FSM이 존재하여, 하나의 DQ 지연이 끝나면 다음 비트가 활성화되는 방식으로 진행된다. 여기서 사용된 read-time 보정은 여러 DQ 스큐 보정을 순차적으로 진행함으로 스큐 보정에 많은 시간이 요구된다. 제안하는 LPDDR3를 위한 메모리 컨트롤러에서는 보정 시간을 단축하기 위하여 하나의 FSM을 각 DQ 별로 나누어 배치함으로써 동시 동작이 이루어진다. 그림 7은 DQ 스큐 보정 과정에 대하여 순서도로 나타낸 것이다. 우선, read-time 보정 회로는 메모리로부터 DQS의 상승 에지에 정렬되어 ‘0’과 ‘1’로 토글하는 DQ 신호를 DQS 신호와 함께 수신한다.

DQS가 DQ의 DQ의 스큐 보정을 위한 기준 신호가 되는데, 이를 위해서 8개의 DQ가 ‘1’이 될 때까지 지연된다. 이 과정의 수행으로 DQ 스큐 보정을 위한 1단계가 종료된다. 다음으로, 모든 DQ의 상승 에지들은 DQS의 상승 에지에 정렬되는 과정이 수행된다. 이 경우 8개의 DQ들에 의한 DQS 에지 스캔의 동작이 동시에 수행되어 본 수행 시간을 단축한다. 모든 DQ들이 DQS의 상승 에지를 찾게 되면, 각 DQ들은 현재 지연 코드를 저장 후 DQ 스큐 보정이 종료된다.

3.3 DCDL

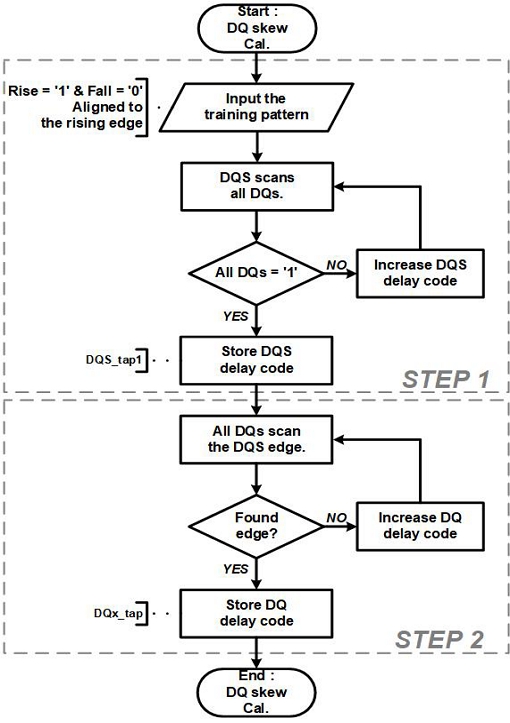

그림 8(a)에 나타난 NAND 게이트로 구성된 DCDL은 read-time 보정 회로에서 생성된 지연 코드(DQ_DELAY[5:0], DQS_DELAY[6:0])를 입력받아 수신된 신호를 지연하는 역할을 수행한다. DCDL은 DQ와 DQS를 위한 lane에 각각 적용되며, DQ는 6비트, DQS는 7비트의 지연 코드를 사용한다. 각 코드 당 지연 시간은 TT corner 기준 20 ps로 설정하여, 보정 완료 후 DQ와 DQS 간의 위상 차이 및 DQS와 CLKPHY 간의 위상 차이를 CLKPHY의 최대 주기의 4% 이내로 제한하기 위함이다. 또한, DCDL은 비트 수가 많아질수록 하드웨어 크기가 증가하는 문제를 고려하여, 지연 코드를 그림 8(a)에서 보는 것과 같이 coarse 제어와 fine 제어의 두 단계로 나누어 설계한다. DQ의 경우 coarse 제어를 위한 5비트와 fine 제어를 위한 1비트가 입력되고, DQS의 경우 coarse 제어를 위한 6비트와 fine 제어를 위한 1비트가 입력된다[7].

DQ를 위한 DCDL은 공정, 전압, 그리고 온도의 변화(PVT, Process, Voltage, and Temperature)를 고려하여 코드 당 지연 값이 가장 작은 FF에서 그림 8(b)의 DCDL 시뮬레이션 결과와 같이 최소 목표 데이터 전송 속도인 1037.5 Mbps/pin에서의 1-unit interval(UI)을 지연 범위로 확보하도록 구현한다. Read-time 보정 과정 중 DQS의 에지와 CLKPHY의 상승 에지 간 보정이 이루어질 때, 가장 큰 지연 값이 1-UI이고, DQ는 DQS와 CLKPHY 간 보정 과정에서 DQS와 동일하게 지연 코드가 증가하기 때문이다.

DQS는 CLKPHY와 보정하는 것과 DQ와 보정을 하는 것이 필요하므로, DQ보다 DCDL의 지연 코드가 한 코드 더 필요하다. DQ와 보정을 진행할 때, DQS는 DQ의 1-UI를 스캔해야 하며, CLKPHY 간 보정에서 최악의 상황이 발생하는 것을 고려하여 DQS의 최대 지연은 FF에서 1037.5 Mbps/pin에서의 1-UI 2배로 설정한다.

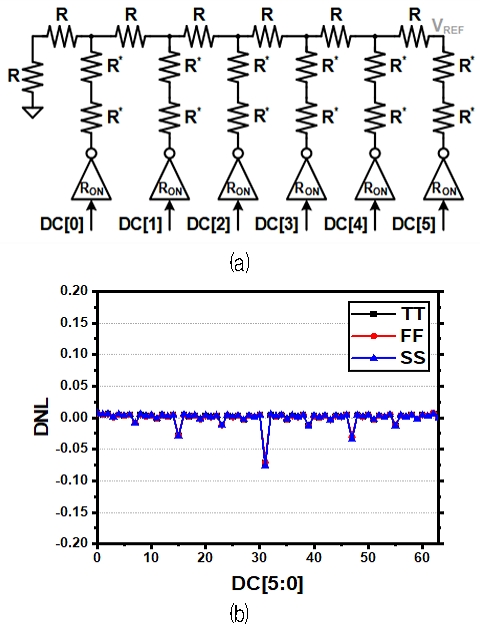

3.4 R-2R DAC

단일 신호를 입력받는 수신기는 기준 전압을 통해 입력 신호가 '1'인지 '0'인지 구분하기 위해 기준 전압 발생기가 요구된다. 이를 위해 본 연구에서는 R-2R DAC를 사용하여 기준 전압 발생기를 구현한다. R-2R DAC는 그림 9(a) 같이 단위 저항이 직렬로 2개 연결되며, 2R에 해당하는 저항이 병렬로 배치되어 사용된다. R-2R DAC는 다른 DAC에 비하여 고해상도, 작은 면적, 저전력으로 구동할 수 있다는 장점이 있다. 하지만, 스위치의 온저항이 존재하기에 선형성이 떨어진다는 단점이 있다. 선형성을 개선하기 위해 그림 9(a)와 같이 2R을 스위치의 온저항을 고려하여 R보다 작은 값을 가지는 R’으로 구현한다. 이를 통해 설계된 R-2R DAC는 그림 9(b)에 나타난 바와 같이 +0.01/-0.08 LSB의 DNL (Differential Non-Linearity)의 특성을 가진다[8].

Ⅳ. 쓰기 동작을 위한 송신단 설계

송신기는 디지털 로직에서 데이터를 입력받아, 메모리로 데이터를 전송하는 쓰기 동작을 수행한다. 송신기는 그림 10과 같이 직렬화기, 출력 드라이버, 그리고 임피던스 보정 회로로 구성된다. DDR 인터페이스에서는 메모리로 송신하는 클록의 한 주기 동안 두 개의 데이터를 전송함으로 송신기는 메모리 컨트롤러의 디지털 로직으로부터 CLKLOGIC에 동기된 두 개의 데이터를 병렬로 입력받는다.

입력된 병렬 데이터는 직렬화기에서 정해진 타이밍에 따라 순차적으로 직렬화된다. 직렬화된 데이터는 출력 드라이버를 통해 외부 메모리로 전송되며, 출력 드라이버의 임피던스와 전송선의 임피던스 차이로 인해 발생하는 신호 반사를 줄이기 위해, 출력 드라이버에는 임피던스 보정 회로가 포함된다.

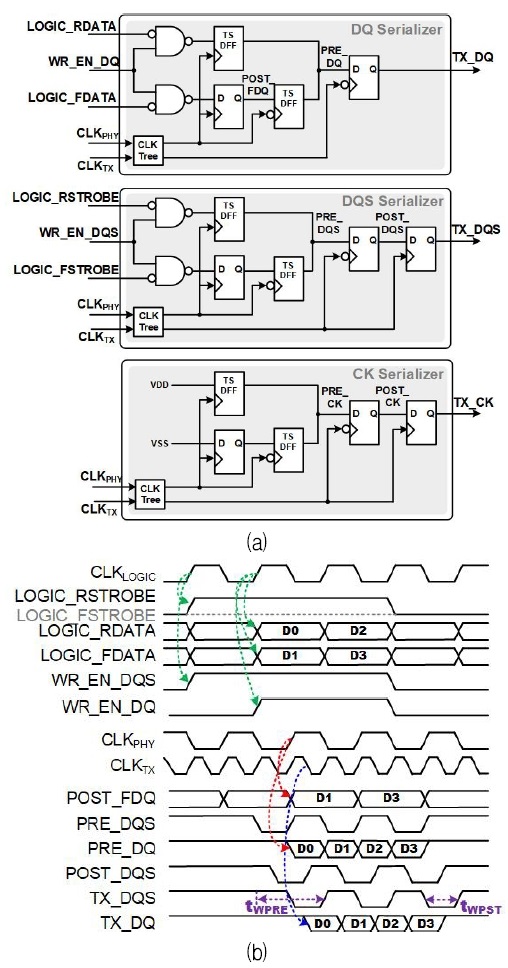

4.1 직렬화기

그림 11은 설계된 직렬화기의 블록도와 타이밍도를 보여준다. 데이터 직렬화기(DQ serializer)와 스트로브 직렬화기(DQS serializer)는 NAND 게이트의 출력이 F/F의 입력으로 연결되는 형태를 가진다. 이 구조는 쓰기 동작 시 WR_EN_DQ 신호와 WR_EN_DQS 신호가 ‘1’로 인가되어야 정상적으로 동작하며, ‘0’일 경우에는 ‘1’을 출력하도록 설계한다. 이는 메모리의 read 동작 중 수신기에서 필요한 종단저항을 형성함으로써 반사파를 최소화하고 데이터 수신의 신뢰성을 높이기 위함이다. 클록 직렬화기(CK Serializer)의 경우, 쓰기 및 읽기 동작과 관계없이 메모리에 EX_CK를 송신해야 하므로 DQS 직렬화기에서 NAND 게이트가 제외된 형태로 설계되지만, 동작 방식은 DQS 직렬화기와 동일하다. 디지털 로직의 출력이 직렬화기에 인가될 때, 타이밍이 어긋날 가능성이 있다. 직렬화기의 첫 번째 F/F은 CLKPHY의 상승 에지에 동기화하여 신호의 타이밍 여유를 확보한다. 그림 11(b)에 따르면, 쓰기 동작을 시작할 때 DQS 직렬화를 위한 신호(LOGIC_RSTROBE, LOGIC_FSTROBE, WR_EN_DQS) 가 DQ 직렬화를 위한 신호(LOGIC_RDATA, LOGIC_FDATA, WR_EN_DQ)보다 한 주기 앞서 수신되어 메모리 쓰기 과정에서 필요한 pre-amble(tWPRE)의 설계 타이밍을 만족시키고, 쓰기 동작을 종료할 때는 LOGIC_RSTROBE, LOGIC_FSTROBE, WR_EN_DQS, LOGIC_RDATA, LOGIC_FDATA 그리고 WR_EN_DQ가 동일한 타이밍에 수신되어 post-amble(tWPST) 타이밍을 만족시킨다. 또한, DQS와 CK 직렬화기는 DQ 직렬화기와 달리 PLL에서 출력된 CLKTX의 상승 에지로 동작하는 F/F을 추가해서 출력 신호를 생성한다. 이를 통해 TX_DQ 대비 90도 시간 지연된 TX_DQS와 TX_CK를 생성함으로 쓰기 동작을 수행한다.

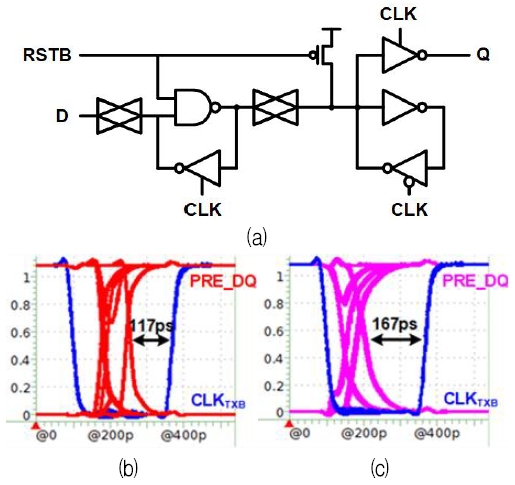

본 직렬화기는 일반적으로 널리 사용되는 멀티플렉서 기반 구조와 달리, 멀티플렉서로 인한 지연 시간을 제거하기 위해 3-상태 D-플립플롭(TS DFF)을 설계하여 멀티플렉서 기능을 대체한다. 제안하는 TS DFF은 기존의 인버터 출력을 사용하는 F/F 구조와 달리, 그림 12(a)와 같이 출력부에 3-상태 인버터를 사용하여 데이터를 출력한다. 그림 12(b)와 (c)는 트랜지스터의 속도가 가장 느린 SS에서 데이터 직렬화기에 대한 시뮬레이션한 결과이다. PRE_DQ와 CLKTXB의 상승 에지 간 시간 차이는 멀티플렉서 기반 직렬화기보다 제안한 TS DFF의 구조가 50 ps 정도 타이밍 여유를 확보한다.

4.2 출력 드라이버 및 임피던스 보정 회로

송신기에 사용되는 출력 드라이버는 그림 13의 단일 종단 구조를 가진다. Pull-up을 위해 PMOS 트랜지스터를 pull-down을 위해 NMOS 트랜지스터를 이용하되 트랜지스터 온저항의 비선형 특성을 개선하기 위해 저항이 추가된다. 출력 드라이버는 34.4Ω에서 240Ω의 출력 임피던스를 가지기 위해 240Ω을 가지는 unit 드라이버 7개를 병렬로 연결하여 설계된다. 출력 임피던스의 가변은 온도계 코드인 DRV_EN[6:0]에 의해 제어된다. 각 unit 드라이버가 240Ω의 출력 임피던스를 가지기 위해 PMOS 트랜지스터와 NMOS 트랜지스터는 4비트 디지털 코드(PU_CODE[4:0], PD_CODE[3:0])에 의해 제어된다. 이들 코드의 자동 제어를 위해 본 연구에서는 임피던스 보정 회로가 사용된다.

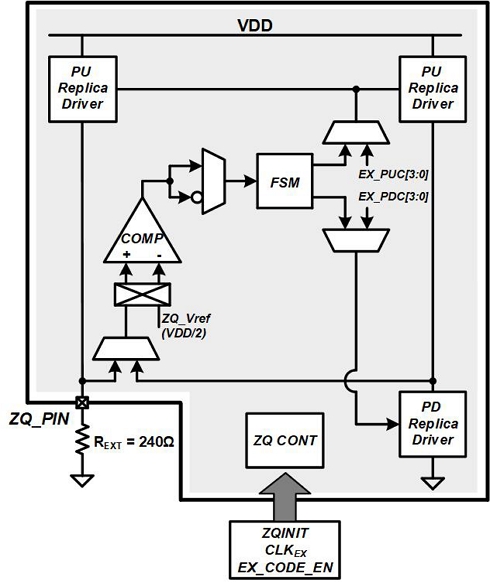

그림 14는 임피던스 보정 회로의 블록도이다. 임피던스 보정 회로는 출력 드라이버의 unit 드라이버의 pull-up path를 모사한 PU Replica Driver와 pull-down path를 모사한 PD Replica Driver로 구성된다. 또한, pull-up path와 pull-down path 사이의 전압 분배 값을 비교할 수 있는 비교기 및 이의 결과로부터 PU Replica Driver와 PD Replica Driver를 제어하기 위한 FSM으로 구성된다. 한편, ground로 연결된 240Ω의 REXT은 메모리 컨트롤러의 외부에 위치한다.

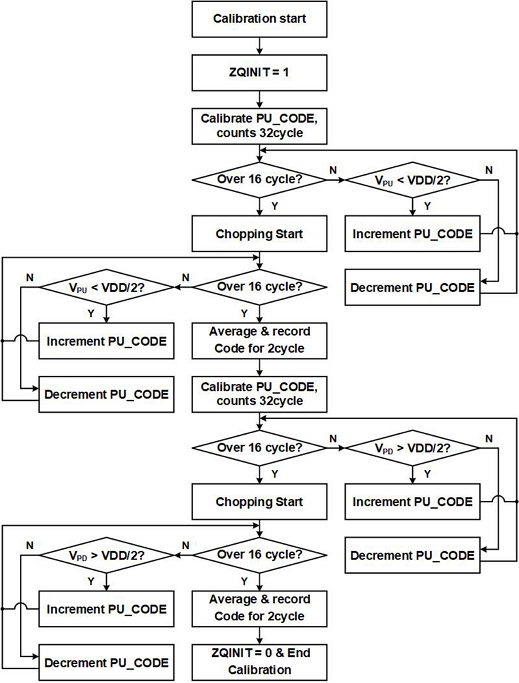

그림 15는 임피던스 보정 회로의 동작 알고리즘을 보여준다. 보정 회로는 두 단계의 과정을 거쳐 출력 드라이버의 임피던스를 조정한다. ZQINIT 신호가 활성화되면 첫 번째 단계에서 외부에 연결된 240Ω의 기준 저항(Rext)을 이용하여 PU Replica Driver의 출력 임피던스를 240Ω이 되도록 보정 한다. PU Replica Driver와 REXT 사이의 전압은 보정 회로 내부에서 생성된 기준 전압(ZQ_Vref)과 비교기를 통해 비교된다. 일반적으로 ZQ_Vref은 VDD/2의 값을 가진다. 16사이클 동안 비교 결과에 따라 디지털 코드의 값이 증가 또는 감소하고 수렴된 디지털 코드가 저장됨으로 출력 임피던스는 목표값으로 보정된다. 그리고 저장된 PU_CODE[4:0]는 모든 출력 드라이버에 공급된다. 이 과정에 사용되는 비교기에 존재하는 오프셋 전압은 임피던스 보정의 정확도를 악화시킬 수 있다. 비교기의 오프셋 전압으로 인해 발생하는 보정 오차를 제거하기 위해, 본 설계에서는 쵸핑 기법을 적용한다[9]. 적용된 쵸핑 기법은 비교기의 입력을 반전시켜 얻은 디지털 코드와 반전 이전의 코드를 평균화해 오프셋 전압의 영향을 제거한다. 이 기법을 적용하기 위해 비교기의 입력을 반전시켜 동일한 과정을 16사이클 동안 진행한 후 쵸핑 기법 전후의 디지털 코드들을 평균 처리하여 오프셋 전압의 영향을 제거하고, 최종 코드로 저장한다. 평균 처리 및 코드 저장에는 2사이클이 소요된다. PU Replica Driver의 보정이 완료되면 두 번째 단계가 시작된다. 두 번째 단계에서는 기준 저항을 이용하지 않고, 앞서 보정된 PU Replica Driver를 기준으로 PD Replica Driver의 임피던스 보정을 진행하는데, PU Replica Driver의 보정 과정과 동일하게 진행된다. 보정이 완료되면, ZQINIT 신호를 비활성화하여 보정 절차를 완료한다. 임피던스 보정은 20.75 MHz의 주파수를 가지는 PLL 외부 입력 클록(CLKEX)를 기준으로 총 68 클록 주기 동안 진행되며, 약 3.28 us의 시간이 소요된다.

Ⅴ. 송수신기 구현 및 시뮬레이션 결과

5.1 ×8 송수신기 구현

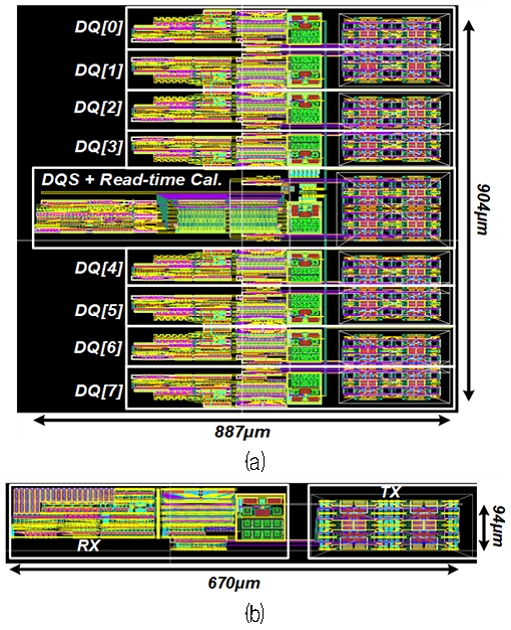

제안된 LPDDR3 메모리 컨트롤러 송수신기는 1.2V 공급 전압의 55nm CMOS 공정을 이용하여 설계되었다. 그림 16(a)는 1-바이트의 송수신기의 레이아웃이다. 하나의 DQS lane을 배치 후, DQS lane을 기준으로 1-바이트를 구성하는 8개의 DQ lane을 4개로 나누어 위아래로 배치한다. 1-바이트로 구현된 송수신기는 887 μm × 904 μm의 면적을 가지며, 하나의 DQ lane의 면적은 그림 16(b)에 나타난 바와 같이 670 μm × 94 μm이다. 1-바이트로 구현된 송수신기를 기반으로 시뮬레이션을 진행한 결과를 다음 절에서 나타낸다. 시뮬레이션 결과들은 Calibre의 xRC를 이용하여, R+C+CC PEX(Parasitic Extraction)로 추출된 기생 성분들을 포함한다. 그리고, FR4 채널 및 패키지 모델을 구현하고 JEDEC 기준 LPDDR3의 최대 CIO를 패드의 capacitance로 설정하여 입력되는 신호의 손실을 일으켜 결과를 확인한다.

5.2 수신단의 시뮬레이션 결과

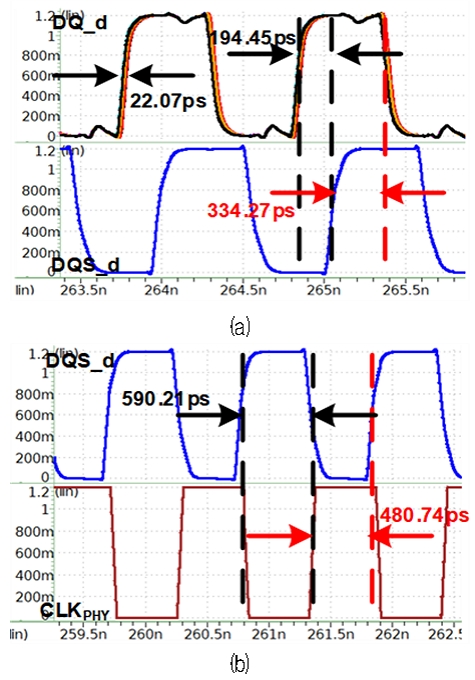

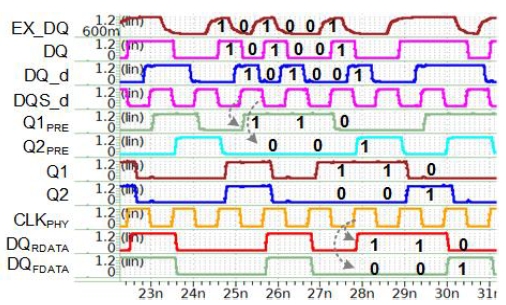

그림 17은 1867.5 Mbps/pin의 데이터 전송률에 대한 신호를 입력받아 수행된 read-time 보정의 시뮬레이션한 결과를 보여준다. DQ들 사이의 시간 스큐는 DCDL의 1비트당 지연 값과 유사한 22.074 ps로 나타난다. DQS의 상승 에지 기준으로 DQ의 상승 에지는 194.55 ps, DQ의 하강 에지는 334.27 ps의 간격을 두고 보정된다. 수신단에 사용된 F/F의 셋업 시간을 고려하여 DQS의 에지를 DQ의 유효 데이터 창 중앙에 위치시키기 위함이다. 또한, read-time 보정을 통해 DQS의 반 주기에 CLKPHY의 상승 에지가 정렬이 되었는데, 이를 통해 DQS와 CLKPHY 간의 클록 도메인 크로싱이 원활하게 진행된다. 그림 18은 수신단에 대해 시뮬레이션을 진행한 결과이다. EX_DQ는 POD 인터페이스로 인하여 VDDQ에서 VDDQ/2의 진폭을 가지며, 메모리로부터 직렬 데이터 ‘101001’을 수신받고 있다. DQ는 VDDQ/2의 진폭을 가지는 EX_DQ를 VDD의 레벨로 변환되어 출력되는 것을 확인할 수 있다. DQ_d와 DQS_d는 DCDL에 의하여 지연이 발생한 결과이며, DQS_d가 DQ_d의 유효 데이터 창 안에 있는 것을 볼 수 있다. 이후, DQS_d의 상승 에지와 하강 에지는 직렬 데이터인 DQ_d를 ‘110’의 데이터값을 가지는 Q1PRE와 ‘001’의 데이터값을 가지는 Q2PRE로 병렬화함을 알 수 있다. Q1과 Q2는 역직렬화기 내부에서 Q1PRE와 Q2PRE를 클록 도메인으로 변환 후, 정렬한 데이터이다. DQRDATA와 DQFDATA는 Q1과 Q2를 디지털 로직에서 사용하는 클록(CLKLOGIC)과 동일한 위상인 CLKPHY를 사용하여 얻은 결과이며, 각각 Q1PRE와 Q2PRE의 데이터값인 ‘110’과 ‘001’을 가지고 있는 것을 확인할 수 있다. 1867.5 Mbps/pin의 데이터 전송률을 가지는 각 DQ의 수신단의 전력 소모는 3.64 mW이다.

5.3 송신단의 시뮬레이션 결과

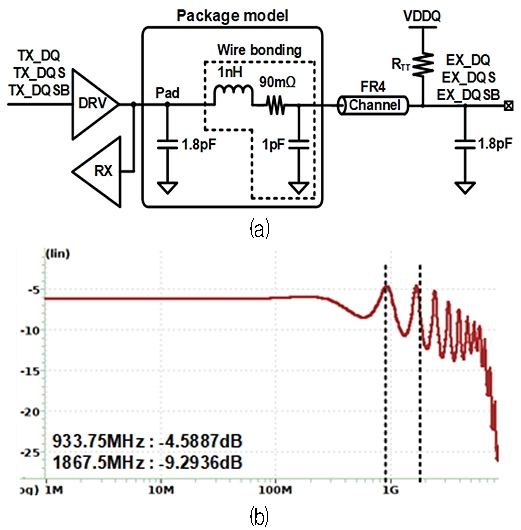

그림 19(a)는 송신단의 시뮬레이션을 위한 채널 모델을 보여준다. 패드 모델은 LPDDR3 규격을 기준으로 CIO(Input/Output Capacitance)의 최대값인 1.8 pF로 설정하고, 메모리의 수신단의 기생 커패시터 또한 CIO 최대값인 1.8 pF으로 설정한다. 와이어 본딩은 1 nH의 기생 인덕터와 90mΩ의 기생 저항, 그리고 1 pF의 기생 커패시터를 가지도록 한다. 출력 드라이버의 출력 임피던스와 종단저항(RTT)의 값은 48Ω으로 설정하고, 50Ω의 특성 임피던스를 가지는 10 cm의 FR4 채널을 모델링하여 배치한 후 시뮬레이션을 진행한다.

시뮬레이션에 사용된 채널의 AC 특성은 그림 19(b)에 나타난 바와 같이 1867.5 Mbps/pin의 전송률을 위한 기본 주파수인 933.75 Hz에서는 –4.5887 dB의 손실을 가지며, 1867.5 Hz에서는 –9.2936 dB의 손실을 가진다.

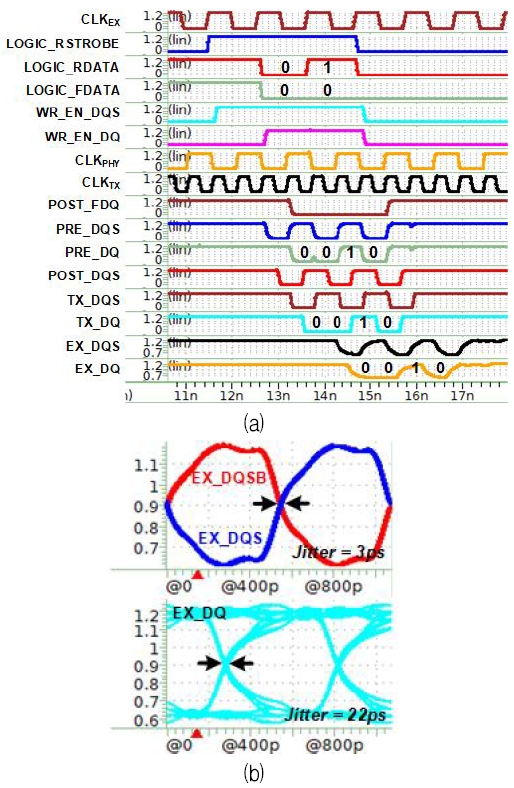

그림 20(a)는 1867.5 Mbps/pin의 데이터 전송률을 가지는 송신단의 실시간 파형에 대한 시뮬레이션 결과이다. 디지털 로직으로부터 입력된 신호들인 LOGIC_RSTROBE, LOGIC_RDATA, LOGIC_FDATA, WR_EN_DQS, WR_EN_DQS는 CLKLOGIC의 상승 에지에 동기화되어 직렬화기로 전달된다. 이후, 상승 에지 데이터인 ‘01’과 하강 에지 데이터 ‘00’를 병렬로 입력받은 직렬화기는 CLKPHY와 CLKTX에 동기화되어 직렬 데이터(TX_DQ)로 변환시켜 ‘0011’이 출력되는 것을 확인 할 수 있다.

또한 WR_EN_DQ 신호가 ‘0’일 경우 LOGIC_FDATA와 LOGIC_RDATA 신호가 ‘0’으로 인가되어도 종단저항을 위해 직렬화기가 ‘1’ 신호를 계속 출력하는 것을 확인 할 수 있다. 마찬가지로 WR_EN_DQS가 ‘0’이면 TX_DQS도 ‘1’ 신호를 출력한다. 이후 직렬화기의 출력은 출력 드라이버로 전달되어 메모리로 신호를 전송한 결과(EX_DQ)가 확인된다. 그림 20(b)는 1867.5 Mbps/pin의 전송률을 가지는 송신단의 아이 다이어그램의 시뮬레이션 결과이다. EX_DQ의 지터는 22 ps이며, 1-UI는 약 535.5 ps이다. 또한, EX_DQS 및 EX_DQSB의 교차 지점에서 측정된 지터는 3 ps이며 유효 데이터 창 중앙에 상승 및 하강 에지가 위치하는 것을 확인할 수 있다. 1867.5 Mbps/pin의 데이터 전송률을 가지는 각 DQ 송신단의 전력 소모는 그림 19의 채널을 사용할 경우 10 mW이며, 그림 19에서 RTT 가 제거될 경우 2.8 mW이다. 구현된 송수신기의 전체 전력 소모는 DQ 핀당 3.45 mW/Gbps이며, [6]에서 구현된 송수신기의 전체 전력 소모는 DQ 핀당 3.36 mW/Gbps와 비교하여 유사한 전력 소모를 가진다.

Ⅵ. 결 론

본 연구에서는 POD 인터페이스를 가지는 LPDDR3 메모리 컨트롤러의 송수신기를 설계하였다. 구현된 송수신기는 1.2V의 공급 전압을 가지며, CMOS 55nm 공정을 사용하여 설계되었다. 설계된 LPDDR3 메모리 컨트롤러의 송수신기는 1037.5 Mbps/pin에서 1867.5 Mbps/pin의 데이터 전송률을 지원한다. 수신단은 CTLE를 이용하면서 교차 커패시터를 이용하여 단일 종단 신호의 수신에 차동적 동작을 개선함으로 신호 보존성을 향상시켰다. 또한, read-time 보정 회로는 각 바이트의 DQ 신호들과 DQS, 그리고 DQS와 메모리 컨트롤러의 CLKPHY를 동기시킴으로 안정된 수신 동작을 지원한다. 송신단의 직렬화기는 3-상태 D-플립플롭를 이용하여 시간 여유를 확보하였으며, 출력 드라이버의 출력 임피던스는 34.3Ω ∼ 240Ω의 범위를 가진다. 1867.5 Mbps/pin의 전송률에서 동작하는 송신단에서 출력된 DQ는 수신단에서 0.96 UI의 시간 윈도우를 가진다.

Acknowledgments

This research was supported by the ITRC support program (IITP-2025-RS-2024-00438288) through the IITP funded by the MSIT and the HRD Program for Industrial Innovation (P0017011) through the KIAT grant funded by the MOTIE, Korea

References

- Video Experts Group, "What is LPDDR(Low-Power Double Data Rate)?", https://www.videoexpertsgroup.com/glossary/lpddr, . [accessed: Apr. 02, 2025]

- JEDEC, "Low Power Double Data Rate 3(LPDDR3)", https://www.jedec.org, . [accessed: Jan. 21, 2025]

- Samsung, "LPDDR3", https://semiconductor.samsung.com/kr/dram/lpddr/lpddr3/, . [accessed: Apr. 22, 2025]

- Marc Greenberg, "LPDDR3 and LPDDR4 : How Low-Power DRAM Can Be Used in High-bandwidth Applications", https://www.jedec.org/sites/default/files/M_Greenberg_Mobile%20Forum_May_%202013_Final.pdf, . [accessed: Jan. 22, 2025]

-

H. Kim, et al., "A 32-Gb/s Single- Ended PAM-4 Transceiver With Asymmetric Termination and Equalization Techniques for Next-Generation Memory Interfaces", IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 71, No. 11, pp. 4912-4923, Nov. 2024.

[https://doi.org/10.1109/TCSI.2024.3408648]

-

J. Lee, C. Song, and Y.-C. Jang, "Chip Implementation of 830-Mb/s/pin Transceiver for LPDDR2 Memory Controller", Journal of IKEEE, Vol. 26, No. 4, pp. 659-670, Dec. 2022.

[https://doi.org/10.7471/ikeee.2022.26.4.659]

-

P.-H. Lee, et al., "A 10-Gbps Receiver Bridge Chip with Deserializer for FPGA-based Frame Grabber supporting MIPI CSI-2", IEEE Transactions on Consumer Electronics, Vol. 63, No. 3, pp. 209-215, Aug. 2017.

[https://doi.org/10.1109/TCE.2017.014908]

-

D.-G. Jeong, et al., "Active-RC Channel Selection Filter with 40MHz Bandwidth and Improved Linearity", Journal of the Korea Institute of Information and Communication Engineering, Vol. 19, No. 1, pp. 149-155, Jan. 2015.

[https://doi.org/10.6109/jkiice.2015.19.1.149]

-

Y.-S. Kim, et al., "A 110 MHz to 1.4 GHz Locking 40-Phase All-Digital DLL", IEEE Journal of Solid-State Circuits, Vol. 46, No. 2, pp. 435-444, Feb. 2011.

[https://doi.org/10.1109/JSSC.2010.2092996]

2024년 2월 : 국립금오공과대학교 전자공학부(공학사)

2024년 2월 ~ 현재 : 국립금오공과대학교 반도체시스템공학과 석사과정

관심분야 : 고속 인터페이스를 위한 클록 발생기

2025년 2월 : 국립금오공과대학교 전자공학과(공학사)

2025년 3월 ~ 현재 : 국립금오공과대학교 전자공학과 석사과정

관심분야 : 저전력 클록 발생기

1999년 2월 : 경북대학교 전자전기공학부(공학사)

2001년 2월 : 포항공과대학교 전자공학과(공학석사)

2005년 2월 : 포항공과대학교 전자공학과(공학박사)

2005년 3월 ~ 2009년 8월 : 삼성전자 반도체총괄 책임연구원

2009년 9월 ~ 현재 : 국립금오공과대학교 전자공학부 교수

관심분야 : 아날로그-디지털 변환기 및 고속 인터페이스를 위한 클록발생기와 송수신기 포함 아날로그집적회로