능동 위상 배열 안테나의 빔 조향 위상 연산 최적화 기법

초록

본 논문에서는 FPGA(Field Programmable Gate Array)를 활용한 능동 위상 배열 안테나의 빔 조향 위상 연산 최적화 기법을 제안한다. 시스템에서 빔 조향을 구현하기 위해서는 소자 수에 비례하는 빔 조향 연산이 필요하다. 이러한 연산은 고속 처리 성능과 많은 자원이 요구되며, 이를 해결하기 위해 연산기를 병렬로 구성하거나 부 배열 단위로 연산을 수행하는 기법이 일반적으로 사용된다. 그러나 이와 같은 방식은 FPGA 자원의 과도한 사용, 설계 복잡도 증가 등의 단점이 있다. 제안된 기법은 안테나의 단위 좌표의 값을 구하고 누적과 덧셈 기법을 이용하여 FPGA 자원을 효율적으로 활용하면서도 빔 조향 연산의 레이턴시를 최적화하였다. 제안된 기법은 FPGA의 하드웨어 자원 사용을 최대 89%까지 최적화하며, 처리 레이턴시를 약 88% 감소시킬 수 있음을 실험을 통해 확인하였다. 또한, 조향 오차는 분해능의 0.005% 수준으로 매우 낮은 오차를 보였다.

Abstract

This paper proposes an optimization technique for veam steering phase calculation in active phased array antennas using Field Programmable Gate Array (FPGA). Beam steering requires calculations proportional to the number of antenna elements, demanding high processing performance. Generally methods use parallel processing or sub-array division, but they increase FPGA resource usage and design complexity. The proposed method computes unit coordinate values and applies accumulation and addition to reduce resource consumption. It optimizes hardware resource usage by up to 89% and reduces latency by approximately 88%. Experimental results confirm the method’s efficiency in both speed and resource usage. The beam steering error is extremely low, at just 0.005% of the resolution.

Keywords:

FPGA, beam steeing, signal processing, AESA, floating point, fixed pointⅠ. 서 론

위상 배열 안테나는 여러 개의 안테나 소자를 배열하여 특정 방향으로 신호를 송수신할 수 있는 시스템으로 통신, 레이더, 전자전 등 다양한 분야에서 중요한 역할을 한다[1][2]. 위상 배열 안테나는 크게 수동 위상 배열 안테나(Passive phased array antenna)와 능동 위상 배열 안테나(Active phased array antenna)로 나눌 수 있다. 수동 위상 배열 안테나는 송수신 부와 안테나 부가 분리되어 있으며, 각 안테나 소자에서 신호의 위상만을 조정 할 수 있고, 신호의 증폭은 송수신 부에서 처리된다. 반면, 능동 위상 배열 안테나는 각 안테나 소자마다 위상을 개별적으로 조절하여 신호의 방향성을 정밀하게 제어할 수 있다. 이러한 안테나는 신호의 방향을 효과적으로 조정하여 신호의 포착 및 전파 효율성을 극대화하는 장점을 가지고 있다[3][4]. 능동 위상 배열 안테나 시스템에서 중요한 요소 중 하나는 빔 조향(Beam steering) 연산의 정확성이다[5]. 빔 조향 연산은 신호의 방향을 정밀하게 제어하는 과정으로, 빠른 연산 처리 과정과 정확한 조향 각도를 요구한다[6]. 이를 실현하기 위해서는 고속 연산이 가능하고, 실시간으로 신호를 제어할 수 있는 시스템이 필요하다.

FPGA(Field Programmable Gate Array)는 하드웨어 설계에 최적화된 프로그래밍 가능한 플랫폼으로, 병렬 처리를 통해 고속 데이터 처리가 가능하고, 실시간으로 제어 처리가 가능하여 능동 위상 배열 안테나 시스템에서 중요한 역할을 한다[7]. 따라서 본 논문에서는 FPGA를 활용하여 위상 배열 안테나의 빔 조향 연산을 최적화하는 기법을 제안한다[8]. 구체적으로, 빔 조향 연산 값의 정확성을 높이기 위하여 연산 중 부동 소수점(Floating point) 연산을 사용하였으며, 연산 속도를 높이기 위해 중간에 고정 소수점(Fixed point) 연산으로 변경하고, 누적과 덧셈 연산을 사용함으로써 레이턴시와 로직 사용량을 동시에 최적화하였다. 제안된 방식의 빔 조향 연산 기법은 안테나 단위가 크면 클수록 큰 효과를 낼 수 있을 것으로 기대된다. 본 논문의 구성은 다음과 같다. 2장에서는 배경과 기존의 빔 조향 연산 방식에 대하여 논의하고 3장에서 개선된 빔 조향 연산 방식에 대하여 설명한다. 4장에서는 기존의 빔 조향 연산 기법과 개선된 빔 조향 연산 기법의 하드웨어 성능을 비교하며 5장에서 결론에 관해 기술하고 마무리한다.

Ⅱ. 배 경

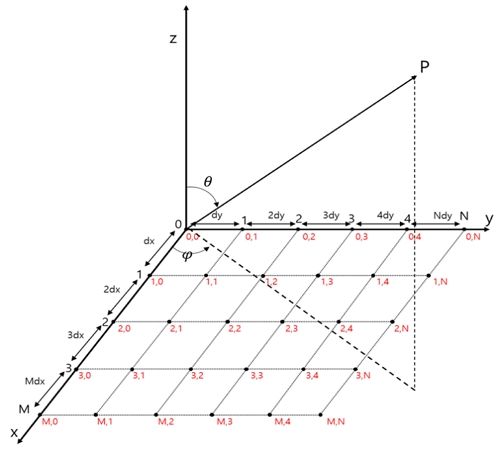

그림 1은 M×N개의 소자를 가진 위상 배열 안테나 배열의 구성을 나타낸다. 각 소자는 dx와 dy의 간격으로 구성되어 있고 Target P의 방향은 방향 코사인 cosαx, cosαy, cosαz로 표현되며 이는 sinθcosϕ, sinθsinϕ, cosθ로 표현할 수 있다[9]. 위 식을 응용하여 빔 조향 연산의 U-V 좌표계의 수식으로 변경할 수 있다. U-V 좌표계는 레이다가 방사하는 면적을 표현하기 위한 좌표계로 레이다가 방사하면 특정 면적에 조사 되고, 이를 2차원 면적으로 모델링한 것이다[10]. 또한 3차원 공간에 있는 표적을 x-y Plane에 매핑하기 위해 방위각(Azimuth)와 고각(Elevation)을 사용[11]하여 아래의 식 (1)~(4)를 도출할 수 있다.

2.1 빔 조향 연산

| (1) |

| (2) |

| (3) |

| (4) |

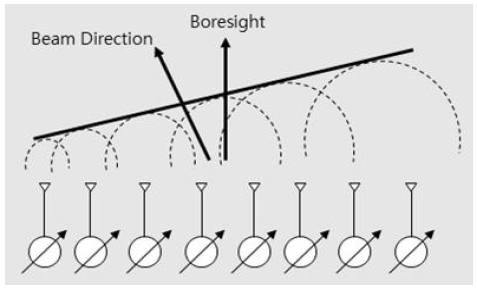

식 (1)은 각 안테나 소자에 적용되어야 하는 위상 변위 값을 계산하는 식을 나타내며, 식 (2)는 파장과 관련된 관계식을 설명한다. 여기서 c는 광속도, f는 운용주파수를 의미한다. 변수 u와 v에 대한 정의는 각각 식 (3)과 (4)에서 제시되며, 이때 az는 방위각(Azimuth), el은 고각(Elevation)을 나타낸다. 이 식들을 이용하여 각 소자의 위상 변위 값을 구하고 변위 값을 각 안테나 소자에 적용함으로써 그림 2와 같이 빔을 형성하고 조향할 수 있다.

2.2 빔 조향 연산기

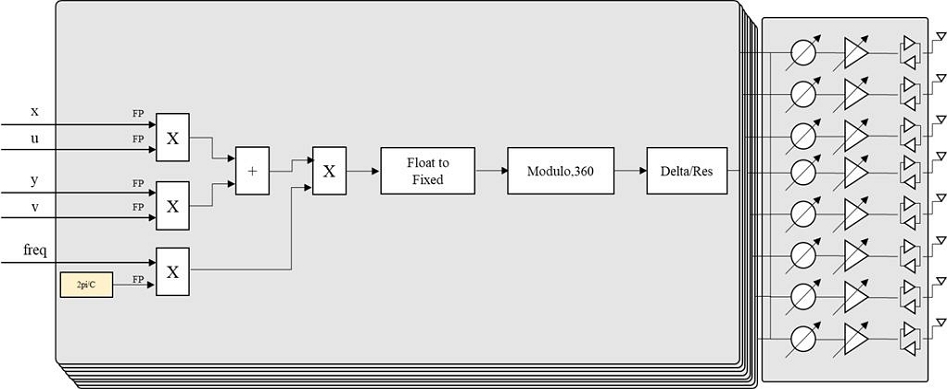

기존의 빔 조향 연산의 외부로부터 특정 주기마다 입력되는 u, v, x, y, frequency의 값을 기반으로 각 소자가 조향해야 하는 위상 변위 값을 계산하였다[12]. 그림 3과 같이, 각 인자의 값을 IEEE 754 표준에 맞게 입력하면, FPGA는 이 데이터를 순차적으로 처리하여 각 안테나 소자에 필요한 위상 변위 값을 연산한다. 연산 과정은 부동 소수점의 곱셈과 덧셈 연산 후, 부동 소수점 값을 고정 소수점 값으로 변환한다. 이후 나머지 연산을 통해 계산된 값을 360도 범위로 조정한다. 마지막으로, 위상 변위기에서 처리할 수 있는 해상도로 값을 나누고 각 안테나 소자에 해당하는 위상 변위 값을 입력하는 것을 끝으로 빔 조향 연산을 마무리한다. 그에 대한 내용은 그림 3을 보면 보다 세부적인 이해가 가능하다.

실시간 조향을 위해서 각각의 안테나 소자마다 연산해야 하는 방식에서는 안테나 소자의 수가 늘어나면 데이터 처리 시간이 길어져 실시간 조향 응답성이 저하되는 문제가 발생할 수 있다. 또한, 입력값을 순차적으로 처리하는 방식은 대형 안테나 배열에서 빠르게 변하는 신호에 대하여 조향이 원활하게 이루어지지 않아 성능 저하가 발생할 수 있다. 이러한 문제를 해결하기 위하여 부 배열 단위로 안테나 소자를 분리하여 다수의 FPGA에서 빔 조향 연산을 수행하거나, 연산기를 병렬로 처리하는 처리 기법을 적용하여 연산 속도를 향상시키는 방법들이 활용되고 있다. 그러나 다수의 FPGA를 활용하는 방식은 설계 비용과 설계 복잡도를 증가시키고 연산기를 병렬로 처리하는 방식은 FPGA 내 자원 소비가 많아지는 단점이 있다.

Ⅲ. 개선된 빔 조향 연산

개선된 빔 조향 연산 수식에서는 단위 좌표의 위상 변위 값을 계산한 후, 이 값을 활용하여 각 복사 소자에 적용할 값을 덧셈 연산을 이용하여 도출하는 방식으로 구현하였다. 개선된 빔 조향 연산의 수식은 아래의 식 (5)~(10)과 같다.

| (5) |

| (6) |

| (7) |

| (8) |

| (9) |

| (10) |

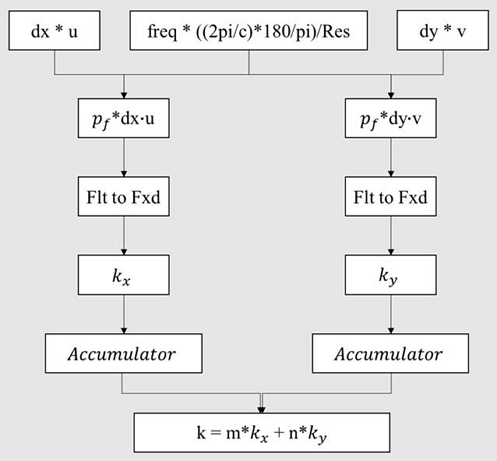

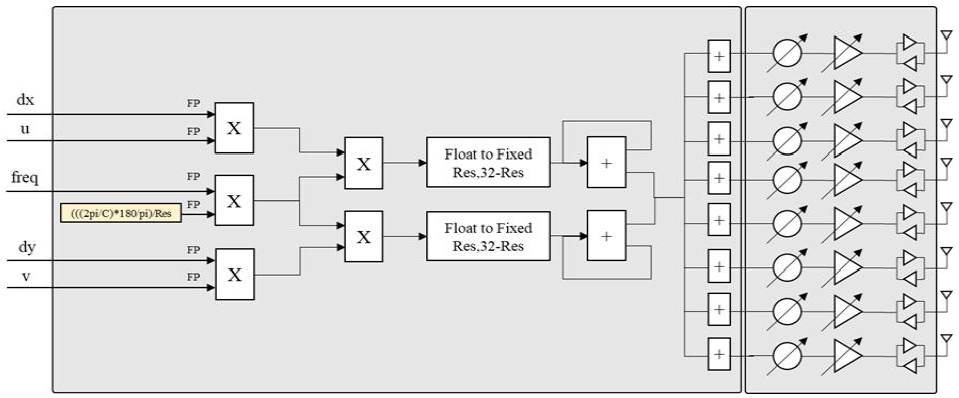

식 (6)에서 P는 2 pi를 광속도로 나눈 값에 해당하며, 이를 라디안에서 도 단위로 변환하는 과정이 포함된다. 또한 Res값은 위상 변위기의 해상도에 따라 최종적으로 나누어지는 계수로 사용되며, 이를 통해 연산 결과를 위상 변위기에 바로 적용 가능한 형태로 변환할 수 있다. 여기서 해상도는 위상 변위기가 처리할 수 있는 최소 위상 변화 단위를 의미하며, 본 논문에서는 8비트 위상 변위기를 기준으로 1.40625도의 해상도를 적용하였다. 식 (7)에서는 식 (6)을 통해 도출된 값과 운용 주파수 간의 곱 연산이 수행되며, 이어지는 식 (8) 및 (9)에서는 dx와 dy 각각의 값과 곱 연산을 통해 단위 좌표의 값을 구할 수 있다.

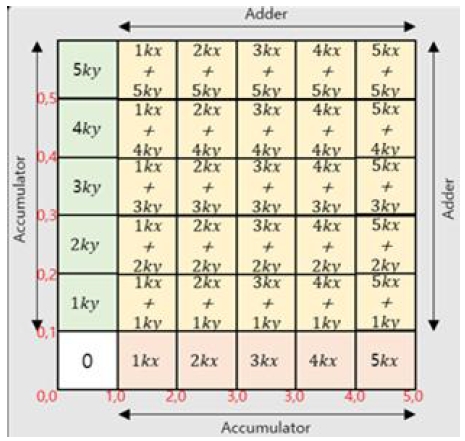

그림 4에서 보이는 것과 같이, 각 연산을 거쳐 나온 kx와 ky의 값은 안테나 배열에서의 (1,0) 및 (0,1)의 위치에 해당하는 값을 의미한다. 한 번의 수식을 통해 kx와 ky의 값을 구한 후, 누산기와 덧셈기를 활용하여 각 복사 소자의 값을 산출하는 방식이다. 이 과정에서 첫 연산에서 발생할 수 있는 누적 오차를 최소화하기 위해 부동 소수점 연산을 사용하였다. 이후, 처리 로직과 레이턴시를 최소화하기 위해 고정 소수점 방식으로 변환하여 누산기와, 덧셈기를 적용하였다.

식 (8)와 식 (9)를 통해 구한 값을 2, 3, 4배 등 누적하면 안테나 소자 거리에 따라 2, 3, 4배 등으로, 선형적으로 증가하는 것을 알 수 있다. 이를 통해 구해진 값을 덧셈 연산을 통해 조합하면 그림 5와 같이 안테나 소자 전체의 위상 변위 값을 구할 수 있다. 식 (6)에서 고정 소수점의 정수부를 위상 변위기의 해상도에 맞춤으로써 누적되는 데이터에 대해 오버플로우(Overflow)를 유도하여 자원의 사용량을 최소화하였다. 제안된 빔 조향 연산기의 구조는 그림 6에서 세부적으로 표현하였다.

Ⅳ. 하드웨어 성능 비교

하드웨어 성능 비교는 Xilinx FPGA의 Artix-200T 모델을 사용하여 시뮬레이션, 합성, 배치 및 배선 과정을 진행되었으며, 144×144개의 배열 안테나를 기준으로 빔 조향 연산 로직의 자원 사용량과 레이턴시를 비교 분석하였다. 로직 사용량은 Vivado를 이용한 구현의 결과로 레이턴시는 연산 시작 시점부터 종료 시점까지 소요 되는 시간을 측정하여 비교하였다. 또한, 제안된 설계 방식의 성능을 이상적인 값과 비교하기 위해 엑셀을 사용하여 오차를 계산하고 성능을 평가하였다.

4.1 FPGA 로직 사용량

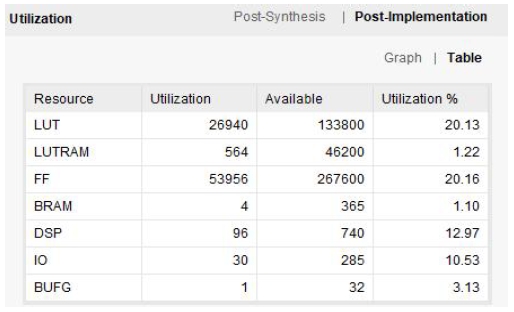

일반적으로 빔 조향 연산에서 위상 변위 값을 계산하기 위해서는 안테나 소자의 수에 비례하는 연산량이 필요하다. 이에 따라 실시간 시스템 운용을 위해 주어진 시간 내에 연산을 수행하려면, 연산기의 병렬 구성을 통해 레이턴시를 줄이는 방식이 주로 사용된다. 그러나 연산기의 수가 증가함에 따라 레이턴시는 비례적으로 감소하는 반면, 전체 로직 사용량은 병렬 수에 따라 선형적으로 증가하게 되어 성능과 로직 사용량 간에 상충 관계가 발생한다. 본 논문에서는 기존의 지상 레이다 장치에 사용되었던 연산기를 8개 병렬로 구성하여, 144×144 안테나 배열을 대상으로 빔 조향 연산을 수행하였으며, 이 방식과 제안하는 연산기 구조 간의 성능 차이를 비교하였다.

그림 7에서는 8개의 연산기를 사용하는 경우 전체 FPGA 로직 자원의 약 20%를 소모하는 것을 확인할 수 있다. 연산기의 병렬 수를 8개에서 1개까지 순차적으로 줄이는 경우, 제안된 방식과 자원 사용량은 유사한 수준으로 보이나, 연산 레이턴시는 1배에서 최대 8배까지 증가할 수 있음을 알 수 있다.

표 1은 연산기 자체의 자원 사용량을 정밀하게 비교하기 위해, 기존 방식에서 8개의 연산기를 사용한 경우의 총사용량을 1/8로 나눈 값을 수치상으로 표현한 지표이다. 이 비교를 통해 1개의 연산기의 관점에서도 제안하는 연산 구조에 이점이 있음을 알 수 있다. 단일 연산기 구조에서 차이가 나는 이유는 제안된 구조에서는 덧셈 연산의 비중이 다소 증가하였지만, 나눗셈 연산 및 나머지 계산 등 복잡도가 높은 연산들이 제거되어 전체적인 연산 효율성은 향상되었다고 볼 수 있다.

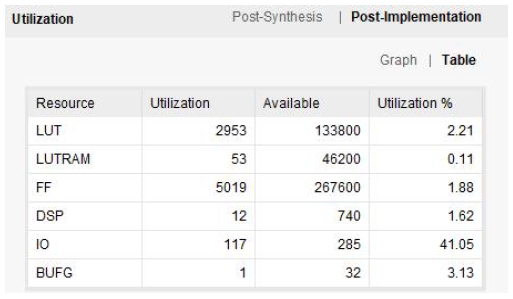

그림 8은 개선된 방식의 하드웨어 자원 사용량을 보여준다. 이 그림 8을 표 1과 비교해 보면 단일 연산기 기준에서도 기존 방식 대비 효율적이라는 것을 알 수 있다.

표 2에서 확인할 수 있듯이, 연산기를 8개 병렬로 처리하는 것에 비해 개선된 방식은 하드웨어 자원 사용에서 약 89%의 절감 효과를 보인다.

4.2 FPGA 레이턴시

각 연산 방식의 레이턴시는 연산에 필요한 데이터 입력 후, 전체 데이터 출력까지의 시간을 시스템 클록 기준으로 측정하였다.

| (11) |

| (12) |

| (13) |

기존 방식의 빔 조향 연산에서의 레이턴시는 식 (11)로 표현된다. 식 (12)의 Cal은 데이터 입력 시점부터 초기 연산 결과가 출력되기까지의 연산 시간을 의미하며, 초기 연산 과정에는 총 120 클록이 소모된다. 또한 M×N은 전체 안테나 배열 소자 수를 의미하고, 테스트에 적용된 M과 N의 개수는 각각 144개를 사용하였다. 이는 곧 안테나의 소자가 144×144 배열을 가지고 있고, 144×144번의 연산이 필요함을 의미한다. 여기서 적용되는 레이턴시는 Arr 수에 비례하여 선형적으로 감소하게 된다. 여기서의 Arr는 병렬로 처리된 연산기의 개수를 나타내며 본 시험에서는 8개의 연산기를 병렬로 사용하였다. 각 연산 모듈은 파이프라인 방식으로 구성되어 있어, 초기 데이터 연산 이후 매 클록 한 개의 데이터가 출력된다. 시스템 클록은 100MHz로 설정하였으며 이를 기반으로 전체 소자에 대한 빔 조향 연산 시간은 27.12 us가 소요된다. 여기서 연산기를 1개만 사용한다고 가정했을 때의 소요시간은 약 208.56 us로 대폭 증가하는 것을 알 수 있다.

다음은 제안하는 방식의 레이턴시를 표현한 식으로 다음과 같이 계산된다.

| (14) |

| (15) |

| (16) |

개선된 방식의 레이턴시는 식 (14)~(16)을 통해 계산할 수 있다. 개선된 방식의 빔 조향 연산기에서는 단위 좌표의 값을 먼저 계산한 후 누산기와 덧셈기를 이용하여 나머지 소자들의 값들을 구하는 방식으로 레이턴시를 감소시킬 수 있다.

개선된 빔 조향 연산에서는 나머지 연산, 위상 변위기의 해상도로 나누기 연산 등의 절차가 제거되기 때문에 Cal에 소요되는 시간은 30 클록으로 감소된다. 조금 더 구체적으로 단위 좌표의 값을 구하고, 누적을 통해 구해지는 mkx 값과 nky 값은 최대 m과 n번의 클록을 소모하면 모두 구할 수 있다. 따라서 전체 소자 연산에 필요한 시간은 식 (15)로 표현할 수 있다. 다음은 덧셈기를 이용하여 각각의 값들을 더해주는 방식으로 모든 소자의 값을 구하는데 필요로 하는 레이턴시는 식 (16)로 정의할 수 있다. 이를 기반으로 전체 소자의 빔 조향 연산에 걸리는 시간은 3.18 us로 대폭 감소하는 것을 확인할 수 있다.

표 3는 기존 방식과 개선된 방식의 하드웨어 레이턴시 차이를 나타낸다. 차이에서 알 수 있듯 기존 방식에 비해 개선된 방식은 약 88%의 레이턴시 감소를 보인다.

4.3 빔 조향 성능

개선된 빔 조향 연산 로직의 성능 비교를 위해 엑셀을 이용한 이상적인 연산 결과와 실제 하드웨어 구현을 통한 결과를 비교하고 분석하였다. 시험은 임의의 값을 frequency, u, v, dx, dy에 입력한 후, 오차가 가장 적은 (0,1), (1,0) 전체 배열의 중간값인 (72,72), 오차가 가장 큰 (144,144) 소자의 값을 기준으로 결과를 산출하였다.

표 4과 표 5에서 볼 수 있듯이, 엑셀로 계산된 값과 실제 로직에서 출력된 값의 최대 오차는 약 0.005%로 나타났다. 이를 통해 제안된 빔 조향 연산 방식이 이상적인 값과 비교해 작은 오차를 보이며, 각각 연산기를 두는 방식에 비해 로직 사용량과 레이턴시가 크게 개선되었음을 확인 할 수 있었다.

Ⅴ. 결 론

본 논문에서는 FPGA를 활용한 능동 위상 배열 안테나 시스템에서 실시간 빔 조향 연산의 성능을 향상시키기 위한 개선된 연산 구조를 제안하였다. 각 안테나 소자별로 독립적인 연산을 수행해야 하는 시스템에서는 연산기의 수에 따라 레이턴시가 줄어드는 반면, FPGA 로직 자원의 사용량은 급증하는 단점이 있었다. 이를 해결하기 위해 제안된 방식은 단위 좌표의 위상 변위 값을 기준으로 누산 및 덧셈 연산을 적용하여 전체 소자의 위상값을 계산하는 방식으로 구조를 단순화하였고, 부동 소수점과 고정 소수점 연산을 활용하여 연산 정확도와 속도를 향상시키고, 하드웨어 로직 사용량을 최소화 하는 데 목표를 두었다. 하드웨어 성능 비교 결과, 제안된 방식은 독립적으로 연산을 수행하는 방식에 비해 약 89%의 FPGA 로직 사용량을 감소시켰으며, 88%의 레이턴시 감소를 달성하였다. 또한 이상적인 값과의 오차는 0.005% 이내로, 높은 정확도를 유지하였다. 이러한 결과는 제안된 연산 방식이 특히 대규모 안테나 배열 구조에서 실시간 조향 응답성과 하드웨어 효율성을 크게 향상시킬 수 있음을 의미한다.

향후에는 다양한 안테나 구조와 주파수 조건에 대해 범용적으로 시스템 통합을 할 수 있는 연구가 필요할 것이다. 이 연구가 향후 능동 위상 배열 안테나 시스템의 효율적인 구현에 기여할 수 있기를 기대한다.

References

-

E. Yang, Y. H. Jang, W. Kim, and D. Yeom, "Beam domain localized adaptive beamforming for fully digital active array radar", The Journal of Korean Institute of Electromagnetic Engineering and Science, Vol. 32, No. 5, pp. 494-504, May 2021.

[https://doi.org/10.5515/KJKIEES.2021.32.5.494]

-

R. Karimian, S. Taravati, M. D. Ardakani, S. Ahmadi, and M. E. Zaghloul, "Nonreciprocal-beam phased-array antennas based on transistor-loaded phase shifters", IEEE Transactions on Antennas and Propagation, Vol. 69, No. 11, pp. 7572-7581, Nov. 2021.

[https://doi.org/10.1109/TAP.2021.3076674]

-

D. Jang, "The calibration method of airborne active electrically scanned array (AESA) antenna using near-field measurement", The Journal of Korean Institute of Information Technology, Vol. 21, No. 12, pp. 121-128, Dec. 2023.

[https://doi.org/10.14801/jkiit.2023.21.12.121]

-

S. H. Talisa, K. W. O’Haver, T. M. Comberiate, M. D. Sharp, and O. F. Somerlock, "Benefits of digital phased array radars", Proceedings of the IEEE, Vol. 104, No. 3, pp. 530-543, Mar. 2016.

[https://doi.org/10.1109/JPROC.2016.2515842]

-

Y. Park, J. Yang, J. Choi, I. Han, T. Kim, Y. Han, and M. Kim, "Design of wide transmit-beam using phase tapering of outer aperture element of active array radar", The Journal of Korean Institute of Information Technology, Vol. 22, No. 12, pp. 85-94, Dec. 2024.

[https://doi.org/10.14801/jkiit.2024.22.12.85]

-

J. Jung, Y. Kim, and J. Seo, "A study on maximum beam pointing error according to resolution of phase shifter for phased array antenna", Journal of the Institute of Electronics and Information Engineers, Vol. 57, No. 1, pp. 42-49, Jan. 2020.

[https://doi.org/10.5573/ieie.2020.57.1.42]

-

M. Wirthlin, "High-reliability FPGA-based systems: Space, high-energy physics, and beyond", Proceedings of the IEEE, Vol. 103, No. 3, pp. 379-389, Mar. 2015.

[https://doi.org/10.1109/JPROC.2015.2404212]

-

D. G. Rao, Y. Shakya, A. N. Margaret, and A. N. Kothari, "A design and implementation of control logic of beam steering unit for phased array radar", Proc. 2006 International Waveform Diversity & Design Conf., Lihue, HI, USA, pp. 1-5, Jan. 2006.

[https://doi.org/10.1109/WDD.2006.8321409]

-

Y. Wang, et al., "Effect of temperature on electromagnetic performance of active phased array antenna", Electronics, Vol. 9, No. 8, pp. 1211, Aug. 2020.

[https://doi.org/10.3390/electronics9081211]

-

G. Kim, K. Yoo, K. Lee, S. Gil, E. Yang, K. Lee, and H. Lee, "Development of radar environmental signals simulator for simulating sub-array receiving signals of active phased array multi-function radar", The Journal of Korea Institute of Military Science and Technology, Vol. 23, No. 5, pp. 452-458, Oct. 2020.

[https://doi.org/10.9766/KIMST.2020.23.5.452]

-

I. Park, "Efficient beam steering calculator design of active electronically scanned array (AESA)", The Journal of Korean Institute of Information Technology, Vol. 22, No. 10, pp. 79-84, Oct. 2024.

[https://doi.org/10.14801/jkiit.2024.22.10.79]

-

T.-W. Yang, C.-H. Bae, S.-M. Kang, and J.-Y. Lee, "Design and performance analysis of a fixed-point based beamforming coefficient calculator for beamforming of a digital active array radar", The Journal of Korean Institute of Electromagnetic Engineering and Science, Vol. 34, No. 12, pp. 918-926, Dec. 2023.

[https://doi.org/10.5515/KJKIEES.2023.34.12.918]

2017년 2월 : 건양대학교 전자정보공학과(공학사)

2024년 8월 ~ 현재 : 한화시스템 선임 연구원

관심분야 : 디지털 하드웨어, 디지털 신호처리, 레이다, FPGA