3-Gsymbol/s/lane MIPI C-PHY 수신기를 위한 듀티 사이클 추적 회로를 포함한 클록 복원 회로

초록

MIPI C-PHY의 수신기를 위한 클록 복원 회로가 복원된 클록에서 발생되는 글리치 노이즈를 제거하기 위해 제안된다. 글리치 노이즈는 클록 복원 회로의 오작동을 유발하며, 이는 복원된 클록의 주파수와 듀티 사이클 비율의 왜곡을 초래할 수 있다. 제안된 보정 회로는 복원된 클록의 듀티 사이클 비율을 샘플링된 전압으로 변환하고, 이 전압의 변화를 추적하여 클록 복원이 올바르게 이루어지고 있는지 판단한다. 효과적인 보정을 수행하기 위해, 보정 회로는 클록 복원 오작동이 가장 빈번하게 발생하는 프리엠블 데이터의 프로그래머블 시퀀스 패턴을 활용하며, 패킷 데이터 입력 전에 보정 작업을 완료한다. 제안된 클록 복원 회로는 3 Gsymbol/s의 전송 속도를 가진 MIPI C-PHY 버전 1.2를 목표로 1.2V의 공급 전압을 가지는 65-nm CMOS 공정을 사용하여 설계되었으며, 보정 작업 중 3.4 mW의 전력을 소비한다.

Abstract

A clock recovery circuit for the receiver of the MIPI C-PHY is proposed to eliminate the glitch noise generated in the recovered clock. The glitch noise can cause malfunctions in the clock recovery circuit, which can distort the frequency and duty cycle ratio of the recovered clock. The proposed calibration circuit converts the duty cycle ratio of the recovered clock into a Sampled voltage and tracks the movement of this voltage to ensure that the clock recovery is performed properly. To perform calibration effectively, the calibration circuit utilizes a programmable sequence pattern of preamble data where clock recovery malfunctions are most frequent to complete the calibration operation before packet data input. The proposed clock recovery circuit, targeting the MIPI C-PHY version 1.2 with a transmission speed of 3 Gsymbol/s/lane, is designed using a 65-nm CMOS process with a supply voltage of 1.2 V and consumes 3.4 mW of power during calibration operations.

Keywords:

MIPI C-PHY, clock recovery, glitch noise, duty cycle ratioⅠ. 서 론

최근 모바일 기기의 해상도가 증가하고 디스플레이 패널들이 대형화되는 등 디지털 시스템들의 성능이 향상됨에 따라 이들 사이에 전송되는 데이터의 대역폭이 급격히 증가하고 있다[1]-[3]. 이를 만족시키기 위해 칩 간 인터페이스의 속도는 계속하여 상승하고 있으나, 이에 따른 인터페이스 회로에서의 전력 소모가 증가하고 있다. 이를 해결하는 방법으로 다중 레벨 신호(Multi-level signaling)가 주목받고 있다. 다중 레벨 신호는 하나의 신호에 더 많은 비트의 정보를 인코딩할 수 있어 동일한 전송 대역폭 내에서 더 많은 데이터를 전송할 수 있다. 특히, 모바일 산업 프로세서 인터페이스(MIPI, Mobile Industry Processor Interface) C-PHY[4]는 일반적으로 사용되는 NRZ(Non-Return-to-Zero)[5] 방식과 달리 low, middle, high의 세 가지 상태를 사용하여 데이터를 전송한다. 또한, 현재 상태 자체는 의미가 있지 않으며, 이전 상태와 현재 상태 사이의 관계를 기반으로 데이터가 정의된다. 또한, 인터페이스를 위한 회로에서의 전력 소모를 줄이기 위해 별도의 클록 신호의 전송 없이 클록 정보가 포함된 데이터를 송수신한다. 이를 위해 MIPI C-PHY에서의 송수신되는 데이터는 이전 상태와 현재 상태가 항상 변화하게 되는데, 수신되는 데이터의 엣지를 검출함으로 클록 신호를 복원한다[6]-[8].

MIPI C-PHY에서 3개의 신호 중 두 개 이상의 신호에 변화가 발생되고 이들 신호의 타임 스큐가 발생될 경우 한번의 데이터 변화에서 복수의 엣지가 발생될 수 있다. 이 경우 클록의 복원 과정에서 글리치 노이즈가 발생될 수 있다. 참고문헌 [6]에서는 펄스 생성 회로를 이용한 클록 복원 회로를 제안하였는데, 펄스 생성 회로에 이용되는 지연 회로를 이용하여 글리치 노이즈를 제거하였다. 그러나 해당 방법은 채널에 상황 및 데이터 속도에 따른 최적화가 어렵다. 이용한다. 이 방법은 일반적인 클록 복원 회로로 글리치 노이즈의 영향을 개선하기 어렵다. 참고문헌 [7]에서는 높은 데이터 속도를 지원하는 수신단을 제안하였으나, 클록 복원 회로에서의 글리치 노이즈 보정회로를 포함하지 않았다. 본 논문에서는 프로토콜의 프리엠블 데이터를 활용하여 데이터 엣지에서 펄스를 생성 회로에 이용되는 지연 회로를 적응적으로 제어하는 클록 복원 회로를 제안한다.

Ⅱ. 제안하는 MIPI C-PHY 클록 복원 회로

2.1 전체 블록도와 글리치 노이즈

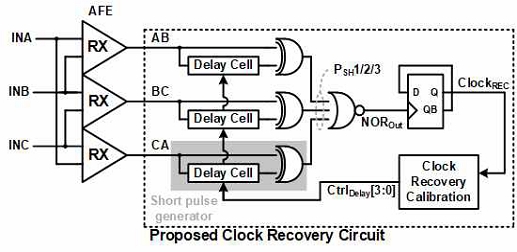

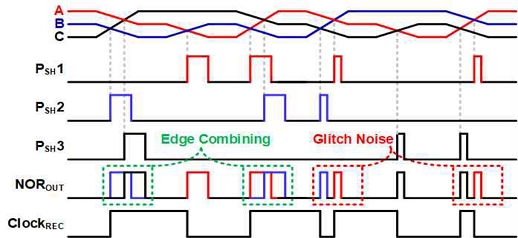

MIPI C-PHY에서 클록 복원은 각 주기마다 상태 변화가 발생하는 입력의 특성을 이용하여 데이터의 엣지를 검출한다. 그림 1은 설계된 MIPI C-PHY를 위한 수신단의 블록도를 보여준다. MIPI C-PHY 수신단은 3개의 wire를 통해 심볼을 입력받는 수신 회로, 클록 복원 회로, 그리고 보정 회로로 구성되며, 클록 복원 회로는 3개의 pulse generator와 NOR logic, D flip-flop, 그리고 보정 회로로 구성된다. 각 수신기는 수신된 세 개의 신호 중 두 개를 서로 비교하여 CMOS 신호로 변환한다. 클록 복원 회로는 세 개의 수신기가 출력하는 AB, BC, 그리고 CA의 세 개의 CMOS 신호의 엣지를 감지하여 펄스 신호를 생성한다.

그림 2에 나타난 바와 같이, 수신기의 세 출력 신호의 엣지는 short pulse generator 회로에 의해 펄스 신호를 생성하고, 펄스 신호 중 가장 늦게 발생한 펄스의 falling edge는 NOR logic 출력 신호의 rising edge를 생성한다. NOR logic의 출력 신호에 연결된 D flip-flop의 동작에 의해 클록 신호가 복원된다.

Timing diagram of clock recovery circuit using edge detection method and concept of glitch noise generation

MIPI C-PHY는 3가지 전압 레벨을 사용하는 방식을 채택하기 때문에 수신기 세 신호의 교차점 간 시간 차이가 발생한다. Short pulse generator의 지연 회로가 입력 신호 간 시간 차이보다 큰 펄스를 생성하게 된다면 PSH1, PSH2, PSH3가 각각 다른 시간에 펄스를 생성하더라도 NOR logic에 의해 하나의 falling edge로 변환되기 때문에 클록 복원이 가능해지며 이 방법을 edge combining이라 칭한다. 하지만 입력 신호 간 시간 차이보다 작은 펄스를 생성하게 된다면 한 심볼의 변화에 대해 두 개의 펄스가 생성되어 왜곡된 클록이 복원되며 이를 글리치 노이즈라 칭한다. 글리치 노이즈 발생 시 심볼 엣지에서 2회의 토글이 발생하기 때문에 듀티 사이클 비율이 왜곡되는 문제가 발생한다. 듀티 사이클 비율 왜곡은 클록 복원 실패를 의미하며 데이터 복원 시 손실을 유발한다. 따라서 시스템 검증 시 입력 신호의 특성, 칩 간 산포마다 달라지는 펄스의 폭으로 인해 칩마다 이를 최적화하는 과정이 요구된다. 일련의 최적화 과정을 최소화하기 위해 클록 복원 회로의 제어 신호를 스스로 결정하는 보정 회로를 제안한다. 보정 회로는 복원된 클록의 듀티 사이클을 추적하며 글리치 노이즈와 같은 이상 동작으로 인해 발생하는 복원된 클록의 왜곡을 감지하여 short pulse generator의 지연 시간을 제어한다.

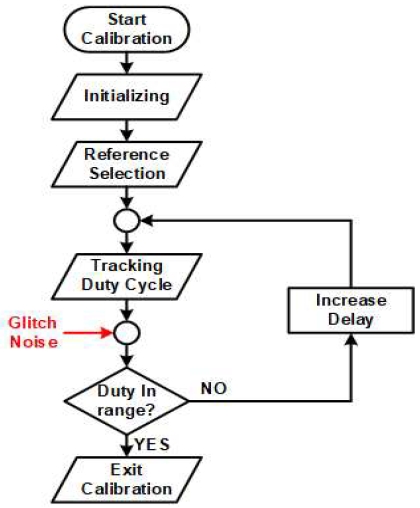

2.2 클록 복원 회로의 보정 기법

클록 복원 회로에서 발생할 수 있는 이상 현상은 크게 세 가지로 분류할 수 있다. 첫 번째는 short pulse generator 출력의 펄스 폭이 좁아 클록이 생성되는 않는 경우이다. 두 번째는 펄스 생성은 가능하지만 채널 손실에 의해 입력 심볼 간 간격이 short pulse generator가 생성한 펄스 폭보다 큰 경우로 그림 2에서 보인 것과 같이 복원된 클록의 듀티 사이클에 왜곡이 발생한다. 세 번째는 펄스 폭이 커서 다음 심볼이 입력될 때까지 NOR의 출력이 falling edge를 만들지 못하는 경우로 이 또한 첫 번째 경우와 같이 클록이 생성되지 않는다. 앞서 제시한 클록 복원 회로에서 발생할 수 있는 이상 현상은 모두 복원된 클록의 듀티 사이클 비율에서 문제가 발생한다. 제안된 클록 복원을 위한 보정 회로는 그림 3에 나타낸 순서도에 따라 보정 동작을 수행한다. 복원된 클록의 듀티 사이클 비율을 샘플링하고 왜곡된 듀티 사이클 비율이 감지되면 short pulse generator의 지연 시간을 늘려 점진적으로 펄스 폭을 증가시키는 방식으로 진행된다.

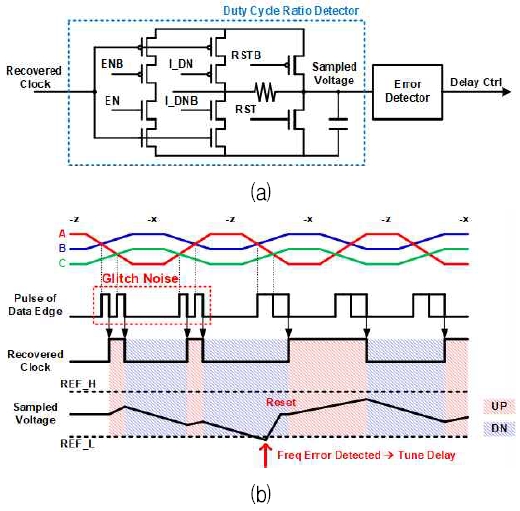

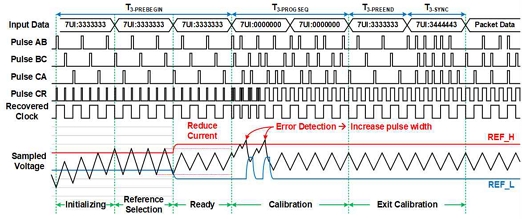

그림 4(a)에 제안된 듀티 사이클 비 추적 회로의 블록도를 나타내었다[9][10]. CLKREC가 high일 때에는 sampled voltage 노드가 VDD와 연결되어 전하가 충전된다. 반대로 CLKREC가 low일 때에는 sampled voltage 노드가 VSS로 연결되어 전하가 방전된다. 복원된 클록이 50%의 듀티 사이클 비율을 유지한다면 한 주기 동안 sampled voltage 노드에 입력된 전류와 출력된 전류의 양이 같아지며 평균적으로 1/2·VDD의 전압에 도달하게 된다.

반면 듀티 사이클 비율이 왜곡된다면 입력된 전류와 출력된 전류의 총량이 달라져 샘플된 전압이 1/2·VDD가 아닌 특정 방향으로 편향된다. 그림 4(b)는 듀티 사이클 비율 추적 회로의 타이밍도를 나타내었다. 초기 심볼인 –Z에서 –X 그리고 다시 –Z로 천이하는 과정에서 글리치 노이즈로 인해 클록이 왜곡되었다. 따라서 sampled voltage는 특정 방향으로 편향되어 특정 임계전압에 도달했을 때 듀티 사이클 비율 왜곡으로 판단하여 오류 신호를 생성하고 short pulse generator의 펄스 폭을 늘린다. 오류를 감지한 후 다음 보정을 준비하기 위해 RST 신호를 이용해 sampled voltage를 다시 1/2·VDD로 복원한다.

2.3 에러 검출기

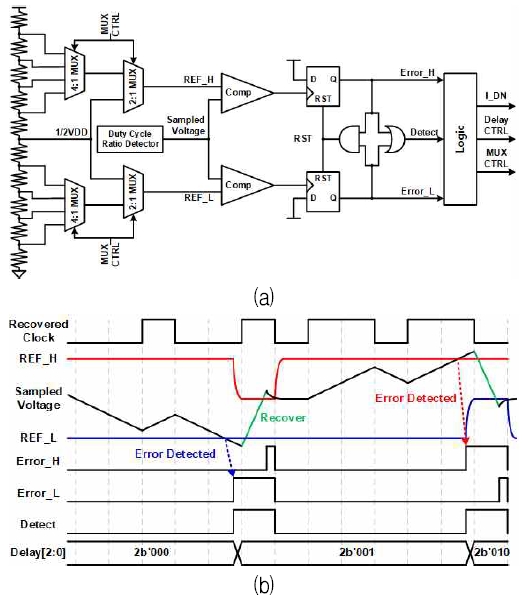

그림 5(a)는 제안된 듀티 사이클 비율 추적 회로에 사용된 오류 검출기의 블록도를 보여준다. 직렬 저항에서 REF_H와 REF_L 기준전압을 선택하고 두 개의 비교기를 이용해 sampled voltage의 노드 전압과 비교한다. Sampled voltage 노드의 전압이 편향되어 임계전압과 교차할 시에 해당 비교기의 출력에 high 신호가 출력되어 Error_H 혹은 Error_L 신호를 생성한다. 생성된 에러 신호는 로직으로 전달되어 임계전압, 듀티 사이클 비율 추적 회로, short pulse generator를 제어한다. 그림 5(b)에 오류 검출기의 타이밍도를 보여준다. 왜곡된 듀티 사이클 비에 의해 sampled voltage 노드의 전압은 임계전압 REF_L보다 작은 값에 도달하여 오류 신호를 생성한다. 이후 다음 보정을 준비하기 위해 그림 4(a)의 RSTB를 사용하여 sampled voltage 노드의 전압을 교차된 임계 전압의 반대 방향으로 복원한다.

2.4 보정 동작을 위한 programmable sequence

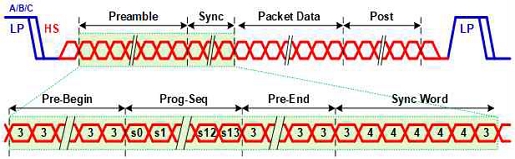

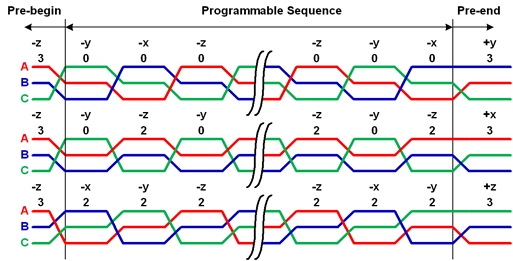

하나의 심볼 엣지가 두 번의 데이터 천이로 인식되는 문제는 주로 특정 패턴에서 나타난다. 따라서 보정 과정을 쉽게 하도록, 그림 6에 나타난 MIPI C-PHY의 프리엠블 데이터를 사용하여 해당 현상이 더욱 쉽게 발생하도록 유도한다. 심볼의 천이는 3bit의 정보(flip, rotation, polarity)에 따라 결정되며 0부터 4까지의 경우의 수를 가진다. MSB인 flip은 +X를 –X로 부호만의 변환을 의미한다. rotation은 +X를 정방향인 +Y로 혹은 역방향인 +Z로 변환할지 결정한다.

LSB인 polarity는 정방향이라는 가정하에 +X를 동일한 극성인 +Y로 혹은 반대 극성인 –Y로의 변환을 결정되고 3비트의 조합으로 다음 심볼이 결정된다. 그림 5는 MIPI C-PHY의 고속(HS) 모드에서 데이터 전송 순서를 나타낸다. 프리엠블 시퀀스는 Pre-Begin, Prog-Seq, 및 Pre-End로 구성되며, Pre-Begin과 Pre-End는 모두 3으로 이루어져 있고, Prog-Seq는 14 UI(Unit Interval) 길이의 사용자 정의 데이터로 구성된다. 그림 7은 제안된 Prog-Seq를 보여준다. Prog-Seq로 2와 0의 반복으로 구성된 심볼을 배정하면 천이 시 발생하는 교차점 중 가장 먼 두 개의 교차점이 있는 상황이 보장된다. 만약 적절한 펄스 폭이 선택되지 않으면, 제안된 보정 회로는 해당 시퀀스에서 복원된 클록의 왜곡된 듀티 사이클을 식별한다.

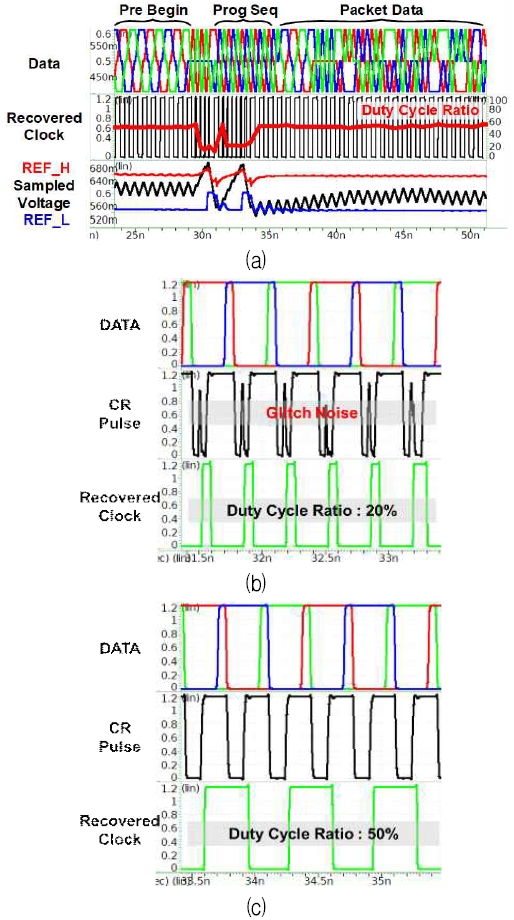

그림 8에 클록 복원 보정 회로의 전체 동작 타이밍도를 나타내었다 보정 시퀀스는 총 5단계로 구성된다. 첫 번째 단계는 초기화 단계로, Pre-Begin의 데이터는 단일 엣지만을 나타내어 왜곡되지 않은 클록을 복원하여 sampled voltage 노드의 전압을 안정시킨다. 두 번째 단계는 임계전압 선택 단계로, 안정화된 sampled voltage 노드의 전압를 이용해 보정에 필요한 REF_H와 REF_L이 선택된다. 이 참조 선택은 Pre-Begin의 데이터를 기반으로 하므로 복원된 클록의 듀티 사이클 비에 왜곡이 발생하지 않는다. Sampled voltage 노드의 전압은 변화 범위 바깥에 있는 가장 작은 전압으로 선택된다. 임계전압 선택 단계가 완료된 후, 실제 보정 작업이 시작되기 전에 듀티 사이클 비율 검출기의 전류가 절반으로 줄어들어 샘플링된 전압의 변화 범위가 감소한다. 이는 보정 작업이 일시적인 외부 잡음[11][12]에 덜 민감하게 작동하도록 돕는다. 이후 프리엠블 데이터를 활용한 보정 작업이 수행된다. 그림 7에 펄스 폭 보정을 위해 Prog-Seq로 반복된 0을 사용하는 예시를 나타내었다. 처음 선택된 펄스 폭이 적절하지 않으면, Prog-Seq로 인해 왜곡된 클록이 복원되고, 듀티 사이클 비율 추적 회로가 이를 감지하여 펄스 폭을 조정한다. 적절한 펄스 폭이 선택되고 정상적인 클록 복원이 이루어지면, 샘플링된 전압이 다시 안정된다.

Ⅲ. 시뮬레이션 결과

제안된 C-PHY 클록 복원 보정 회로는 1.2V 전원 공급전압과 65nm CMOS 공정을 이용하여 설계되었다. 이 회로는 MIPI C-PHY 1.2를 지원하여 최대 3Gsymbol/s/lane의 전송 대역폭을 가진 입력 데이터를 수신하도록 설계되었다. 그림 9(a)는 프리엠블 데이터를 사용한 제안된 C-PHY 클록 복원 보정 회로의 시뮬레이션 결과를 보여준다. Prog-Seq가 입력되었을 때, 그림 9(b)에서 부적절한 펄스 폭으로 인해 데이터의 엣지가 두 개로 인식되어 복원된 클록의 듀티 사이클 비율에 왜곡이 발생하는 것을 확인할 수 있다. 보정 회로는 이를 감지하고 펄스 폭을 조정한다. 그림 9(c)에서 펄스 폭 조정 후 회로가 그림 9(b)에서의 패턴을 단일 엣지로 해석하여 정상적인 클록 복원이 이루어지는 것을 확인할 수 있다. 보정 작업 후 샘플링된 전압은 선택된 임계 전압 사이에서 안정화된다. 클록 복원 회로의 전력 소모는 1.2V 공급전압에서 1.2mW이며, 보정 회로는 2.1mW를 소비한다. 듀티 사이클 비율 검출기는 70uW를 소비하여, 전체 전력 소모는 총 3.4mW이다.

Simulation result of clock recovery calibration (a) Calibration sequence (b) Before calibration (c) After calibration

표 1은 발표된 MIPI C-PHY 클록 복원 회로의 특성을 비교하여 보여준다. 참고문헌 [6]에 발표된 클록 복원 회로는 데이터 엣지에 발생되는 펄스의 폭을 증가시켜 글리치 노이즈를 제거하는데, 채널 환경과 데이터 속도에 따른 펄스 제어 방법이 제시되지 않았다. 또한 참고문헌 [7]의 클록 복원 회로는 높은 전송 속도를 지원하지만 글리치 노이즈를 제거하는 보정 회로를 포함하지 않는다. 이에 반에 제안된 MIPI C-PHY를 위한 클록 복원 회로는 복원된 클록의 듀티 사이클 비율을 추적하며 복원된 클록에 발생되는 클리치 노이즈를 제거한다.

Ⅳ. 결 론

3-Gsymbol/s/lane MIPI C-PHY 버전 1.2를 위한 클록 복원 회로는 1.2V 전원 공급 전압을 이용하는 65nm CMOS 공정에서 구현되었다. 제안된 보정 회로는 엣지 검출 방식을 사용하는 클록 복원 회로에서 발생하는 글리치 노이즈로 인한 클록 왜곡을 제거하는 것을 목표로 한다. 이 회로는 클록의 듀티 사이클 비율을 샘플링된 전압으로 변환하고, 샘플링된 전압이 비정상적인 듀티 사이클 비율로 인해 임계값을 초과할 경우 생성된 펄스 폭을 조정함으로써 글리치 노이즈를 제거한다. 효율적인 보정을 위해 글리치 노이즈가 발생하기 쉬운 프리엠블 데이터의 프로그래머블 시퀀스 패턴을 활용한다. 클록 복원 회로의 보정 작업은 패킷 데이터 입력 전에 완료된다.

Acknowledgments

This research was supported by the MSIT through the ITRC support program (IITP-2024-RS-2024-00438288) supervised by the IITP and the Regional Innovation Strategy (2022RIS-006) through the NRF funded by the Ministry of Education, Korea

References

-

J. Caballero, et al., "Real-time video super-resolution with spatiotemporal networks and motion compensation", 2017 IEEE Conference on Computer Vision and Pattern Recognition (CVPR), Honolulu, HI, USA, pp. 2848-2857, Jul. 2017.

[https://doi.org/10.1109/CVPR.2017.304]

-

Z. Feng, W. Zhang, S. Liang, and Q. Yu, "Deep video super-resolution using hybrid imaging system", IEEE Transactions on Circuits and Systems for Video Technology, Vol. 33, No. 9, pp. 4855-4867, Feb. 2023.

[https://doi.org/10.1109/TCSVT.2023.3250443]

-

L. Chen, M. Ye, L. Ji, S. Li, and H. Guo, "Multi-Reference-Based Cross-Scale Feature Fusion for Compressed Video Super Resolution", IEEE Transactions on Broadcasting, Vol. 70, No. 3, pp. 895-908, Sep. 2024.

[https://doi.org/10.1109/TBC.2024.3407517]

- MIPI Alliance Specification for C-PHY, version, 1.2, Picataway, NJ, USA, Nov. 2016.

- B. Razavi, "Design of Integrated Circuits for Optical Communications", 1st ed. New York, NY, USA: McGraw-Hill, pp. 14-15, Sep. 2002.

-

P.-H. Lee and Y.-C. Jang, "A 6.84 Gbps/lane MIPI C-PHY Transceiver Bridge Chip with Level-Dependent Equalization", IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 67, No. 11, pp. 2672-2676, Nov. 2020.

[https://doi.org/10.1109/TCSII.2019.2962839]

-

T.-J. Kim, J.-W. Park, H.-W. Lim, J.-Y. Lee, and J.-H. Chun, "An 18.24-Gb/s, 0.93-pJ/bit Receiver With an Input-Level-Sensing CDR Using Clock-Embedded C-PHY Signaling Over Trio Wires", IEEE Journal of Solid-State Circuits, Vol. 57, No. 3, pp. 932-941, Mar. 2022.

[https://doi.org/10.1109/JSSC.2021.3140053]

-

P. Lancheres and M. Hafed, "The MIPI C-PHY Standard: A Generalized Multiconductor Signaling Scheme", IEEE Solid-State Circuits Mag., Vol. 11, No. 2, pp. 69-77, Jun. 2019.

[https://doi.org/10.1109/MSSC.2019.2910616]

-

H.-Y. Huang, C.-M. Liang, and S.-J. Sun, "Low-power 50% duty cycle corrector", 2008 IEEE International Symposium on Circuits and Systems (ISCAS), Seattle, WA, USA, pp. 2362-2365, May 2008.

[https://doi.org/10.1109/ISCAS.2008.4541929]

-

P.-H. Yang and J.-S. Wang, "Low-voltage pulsewidth control loops for SOC applications", IEEE Journal of Solid-State Circuits, Vol. 37, No. 10, pp. 1348-1351, Oct. 2002.

[https://doi.org/10.1109/JSSC.2002.803050]

-

J. Monthie, V. Sreekumar, and R. Yashwante, "Impact of power supply noise on clock jitter in high-speed DDR memory interfaces", 2013 26th International Conference on VLSI Design and 2013 12th International Conference on Embedded Systems, Pune, India, pp. 262-266, Jan. 2013.

[https://doi.org/10.1109/VLSID.2013.198]

- W. J. Dally and J. W. Poulton, "Digital Systems Engineering", Cambridge,U.K.: Cambridge Univ. Press, pp. 225-228, 1998.

2024년 8월 : 금오공과대학교 전자공학부(공학사)

2024년 8월 : 금오공과대학교 전자공학과(공학석사)

2024년 8월 ~ 현재 : 금오공과대학교 반도체시스템공학과 박사과정

관심분야 : 클록 발생기, 고속 인터페이스 송수신기

1999년 2월 : 경북대학교 전자전기공학부(공학사)

2001년 2월 : 포항공과대학교 전자공학과(공학석사)

2005년 2월 : 포항공과대학교 전자공학과(공학박사)

2005년 3월 ~ 2009년 8월 : 삼성전자 반도체총괄 책임연구원

2009년 9월 ~ 현재 : 금오공과대학교 전자공학부 교수

관심분야 : 아날로그-디지털 변환기, 클록 발생기, 고속 인터페이스 송수신기