FPGA 기반 패턴 발생기를 위한 2.56-Gsymbol/s/lane MIPI C-PHY 송신 브릿지 칩

초록

모바일 디스플레이 구동 및 평가를 위해 사용되는 FPGA(Field Programmable Gate Array) 패턴 발생기를 위한 MIPI(Mobile Industry Processor Interface) C-PHY version 1.0 송신 브릿지 칩을 제안한다. 제안된 MIPI C-PHY version 1.0 송신 브릿지 칩은 LVDS의 3개의 차동데이터와 1개의 클록을 FPGA로부터 공급받아서 l개 레인의 MIPI C-PHY 신호를 출력한다. 연속시간 선형 등화를 수행하는 LVDS 수신기는 수신된 3개의 차동 데이터 사이의 타임 스큐를 제거하기 위해 수신된 클록을 이용하여 동기화하는 데이터 샘플러를 포함한다. MIPI C-PHY version 1.0 송신기는 3개의 전압 레벨을 송신하는데, 채널 손실을 보상하기 위한 level-dependent pre-emphasis 등화를 수행한다. 2.56-Gsymbol/s의 전송률을 가지는 제안된 MIPI C-PHY version 1.0 송신 브릿지 칩은 1.1V의 공급전압을 이용하는 40-nm CMOS 공정에서 구현된다. 측정된 MIPI C-PHY의 출력은 150 mV의 전압 크기와 79 ps의 peak-to-peak 타임 지터를 가진다.

Abstract

A mobile industry processor interface(MIPI) C-PHY version 1.0 transmission bridge chip for a field programmable gate array(FPGA)-based pattern generator used for driving and evaluating mobile displays is proposed. The proposed MIPI C-PHY transmission bridge chip receives three differential data and one clock of LVDS from the FPGA and outputs l lane of the MIPI C-PHY signal. The LVDS receiver, which performs continuous-time linear equalization, includes a data sampler that synchronizes with the received clock to eliminate time skew between the three differential data received. The MIPI C-PHY transmitter transmits three voltage levels and performs level-dependent pre-emphasis equalization to compensate for channel loss. The proposed MIPI C-PHY transmission bridge chip with a transmission rate of 2.56-Gsymbol/s is implemented by using a 40-nm CMOS process with a supply voltage of 1.1 V. The measured output of the MIPI C-PHY has an amplitude of 150 mV and a peak-to-peak time jitter of 79 ps.

Keywords:

MIPI C-PHY, transmission bridge chip, field programmable gate array, LVDS, equalizationⅠ. 서 론

최근 모바일 기기의 급속한 발전과 시장 확대로 이미지 센서와 디스플레이의 해상도가 지속적으로 증가하고 있으며, 이를 지원하기 위해 모바일 기기들을 위한 고속 인터페이스로 MIPI(Mobile Industry Processor Interface)가 널리 사용되고 있다[1]-[3]. 특히 MIPI PHY 중 C-PHY는 별도의 클록 신호를 송신 및 수신하지 않고 데이터에 임베딩함으로 클록 신호의 전송으로 요구되는 칩의 핀, 채널 그리고 전력 소모를 줄인다[1]. 또한, MIPI C-PHY는 3개의 전압 레벨로 데이터를 코딩하여 심볼로 전송하는데, 1 심볼은 2.28 비트의 유효 비트를 포함하여 인터페이스의 대역폭을 증가시키는데 이점이 있다. 한편, MIPI C-PHY의 인터페이스를 사용하는 모바일 디스플레이를 구동 및 평가하기 위해 일반적으로 FPGA(Field Programmable Gate Array)를 이용하는 패턴 발생기를 사용하는데[4][5], FPGA가 MIPI C-PHY를 지원하지 못한다. 이의 문제를 해결하기 위해 발표된 MIPI C-PHY 송수신 브릿지 칩은 1 lane의 MIPI C-PHY 데이터의 송신을 위해 FPGA로부터 21개의 병렬 데이터를 수신받는다[6]. 이 경우 MIPI C-PHY의 여러 lane을 구현할 경우, 많은 병렬 채널의 사용으로 시스템의 구현에 어려움이 있다. 이에 본 논문에서는 FPGA로부터 저전압 차동 신호(LVDS, low voltage differential signaling)를 수신하여 MIPI C-PHY version 1.0을 만족하는 신호를 모바일 application processor로 공급하는 MIPI C-PHY 송신 브릿지 칩을 제안한다. 본 논문의 II장에서는 MIPI C-PHY 송신 브릿지 칩의 구성과 동작을 회로도 및 시뮬레이션 결과를 통해 설명하고 III장에서는 본 논문에서 설계한 MIPI C-PHY 송신 브릿지 칩의 제작과 측정 결과를 서술한다. 그리고 IV장에서 결론을 제시하면서 논문을 마무리한다.

Ⅱ. MIPI C-PHY 송신 브릿지 칩

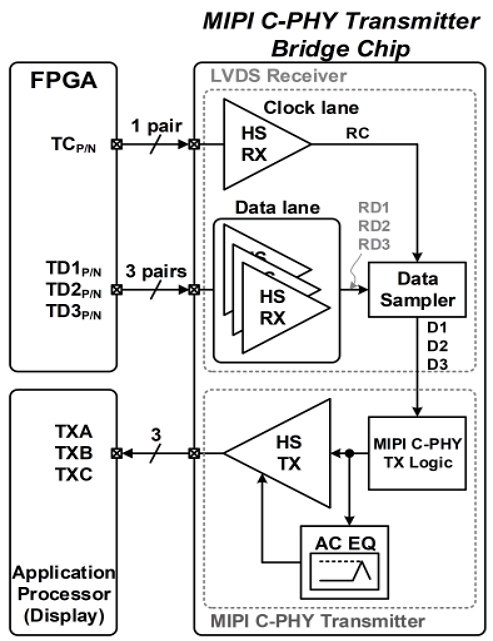

그림 1에 나타낸 제안된 MIPI C-PHY 송신 브릿지 칩은 크게 FPGA에서 송신하는 LVDS 신호를 수신하는 LVDS Receiver 블록과 MIPI C-PHY의 1 lane 데이터를 송신하는 MIPI C-PHY Transmitter 블록으로 구성된다. FPGA에서는 총 4개의 레인을 통해 3개의 데이터와 1개의 클록을 송신한다. MIPI C-PHY 송신 브릿지 칩은 수신된 클록 신호로 3개의 데이터를 수신하고 동기화한 후 MIPI C-PHY의 프로토콜에 맞추어 데이터 인코딩을 진행하여 MIPI C-PHY Transmitter를 통해 출력한다.

LVDS Receiver는 3개의 차동 데이터와 1개의 차동 클록 신호를 수신하기 위한 4개의 HS RX(high-speed receiver)와 3개의 데이터를 클록 신호로 동기하는 Data Sampler로 구성된다. HS RX는 FPGA와 MIPI C-PHY 송신 브릿지 칩 사이의 전송선에서 발생한 고주파 손실을 보상하기 위해 등화를 수행하여 데이터를 복원한다. 또한 RD1, RD2, RD3의 3개 레인에서 발생할 수 있는 타임 스큐의 영향을 제거하기 위한 Data Sampler는 RD1, RD2, RD3 세 개의 수신 데이터를 수신된 클록 신호(RC)를 이용하여 동기시킨다. 이후, 수신된 3개 데이터(D1, D2, D3)는 MIPI C-PHY Transmitter로 공급된다.

MIPI C-PHY Transmitter는 MIPI C-PHY TX Logic 블록을 통해 MIPI C-PHY 프로토콜에 따른 인코딩을 진행하며, 채널의 손실을 보상하기 위해 데이터 출력 시 AC 등화를 수행한다.

2.1 LVDS 고속 수신 회로

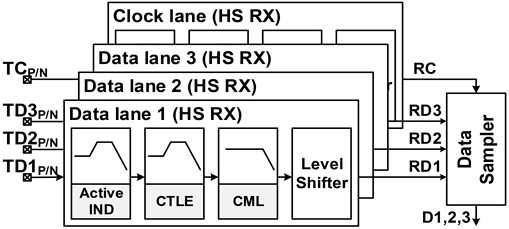

그림 2는 FPGA로부터 송신된 LVDS 신호를 수신하기 위한 LVDS Receiver의 블록도를 보여준다[7]. LVDS Receiver는 3개의 데이터와 클록 신호를 수신하기 위한 4개의 HS RX와 동기 회로인 Data Sampler로 구성된다. HS RX는 FPGA에서 공급되어 채널을 통해 수신되는 신호를 두 단의 등화기를 통해 신호의 보존성을 개선한다. 이를 위해 active inductor를 부하로 사용하는 차동 증폭기[8], 연속시간 선형 등화기(CTLE: continuous-time linear equalizer), CML(current mode logic)[9][10]을 이용한 드라이버, 그리고 수신된 신호를 CMOS 전압 레벨로 변환하는 Level Shifter로 구성된다. FPGA에서 MIPI C-PHY 송신 브릿지 칩으로 전송된 데이터 사이에 타임 스큐가 발생하여 MIPI C-PHY TX Logic에서 연산할 때 오류 혹은 클리치 노이즈가 발생할 수 있다. 따라서 Data Sampler는 수신된 클록을 이용하여 3개의 차동 데이터 동기화하여 데이터 간의 타임 스큐가 제거된 3개의 병렬 데이터(D1, D2, D3)를 출력하고 MIPI C-PHY Transmitter 블록으로 공급한다.

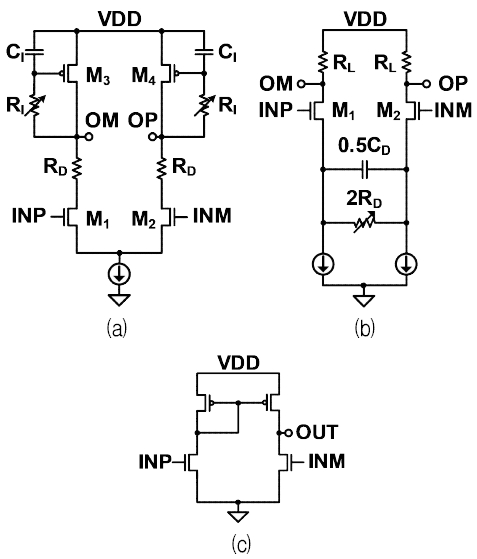

그림 3은 HS RX의 세부 회로도를 나타낸다. 그림 3(a)에 나타낸 active inductor를 부하로 사용하는 차동 증폭기는 저주파수에서는 M3와 M4를 부하로 사용하여 입력 신호를 증폭하는데, 고주파 신호에 대해서는 CI의 임피던스가 낮아져서 RI를 통해 전류가 흐르게 되어 고주파수에서 추가적인 이득을 가지게 된다. 이 원리를 통해 RI의 저항값을 조절하여 영점과 극점을 제어함으로 고주파 이득을 조절한다. 그림 3(b)의 CTLE는 식 (1)과 같은 전달함수를 가진다. CTLE의 저주파수 전압 이득은 식 (2)와 같이 source degeneration 회로의 RS의 저항값을 가변하여 변화시킬 수 있다. 또한 고주파수에서 피킹을 통한 등화를 수행하기 위해 고려되는 영점과 극점은 식 (3)과 같다. 아래 수식에서 CL은 CTLE의 출력 부하 커패시터이며, 트랜지스터의 소신호 rO는 무한대의 값으로 가정되었다.

| (1) |

| (2) |

| (3) |

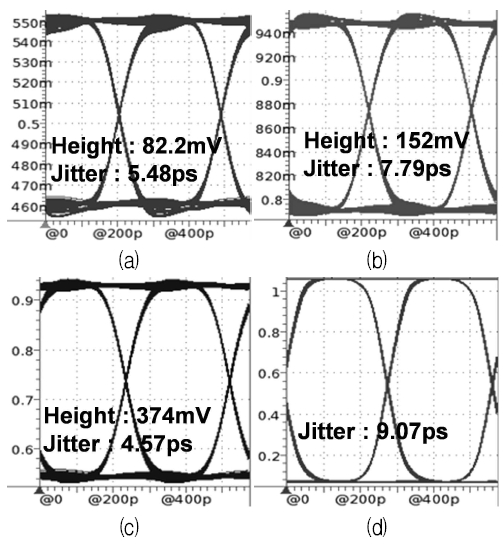

그림 3(a)와 (b)에 나타난 두 단의 등화를 통해 신호 보존성이 개선된 차동의 수신 신호는 그림 3(c)에 나타난 Level Shifter를 통해 당일 종단의 CMOS 신호로 변환된다. 그림 4는 3.5-Gsymbol/s의 데이터 전송률을 가지는 수신된 신호에 대한 HS RX의 시뮬레이션 결과를 보여준다. 4단의 세부 증폭기 및 equalizer를 통해 100mV 이하의 수신된 신호의 전압 크기는 1.2V CMOS 전압으로 변환되며, 9.07ps의 타임 지터의 특성을 가진다.

2.2 MIPI C-PHY Transmitter

MIPI C-PHY Transmitter의 MIPI C-PHY TX Logic 블록은 LVDS Receiver 블록이 출력 데이터(D1, D2, D3)를 MIPI C-PHY의 프로토콜에 따라 인코딩을 수행한다. MIPI C-PHY Transmitter의 3개의 출력을 위한 HS TX(high-speed transmitter)는 각각 3-level 시그널링을 위해 3-상태 입력이 필요하다. 표 1은 HS TX에서 3-상태 신호를 출력할 수 있도록 하는 진리표를 나타낸다. 표 1의 진리표에 따른 MIPI C-PHY TX Logic의 동작에 의해 HS TX는 표 2에 나타난 대로 TXA, TXB, 그리고 TXC를 통해 와이어 상태를 출력한다. 이때 3개의 라인에서 출력되는 MIPI C-PHY의 데이터는 H(high), L(low), M(middle)의 상태를 가질 수 있으며 3개 라인의 데이터가 중복될 수 없다. 즉, MIPI C-PHY Transmitter의 HS TX를 통해 출력할 수 있는 와이어 상태는 6가지로 결정된다[11]. 따라서, D1/D2/D3의 3비트 데이터 중 3b’011와 3b’100의 두 경우는 MIPI C-PHY 프로토콜에 의해 LVDS Receiver에서 수신되지 않는다. 또한, FPGA는 이 두 경우의 데이터를 송신하지 않도록 프로그램되어야 한다.

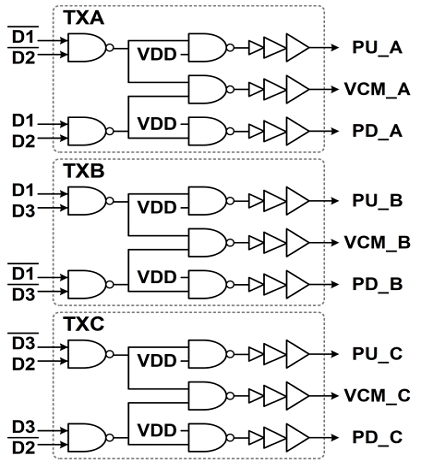

그림 5는 MIPI C-PHY TX Logic의 회로도이다. 3개의 HS TX를 구동하기 위해 3개의 블록으로 구성된다. D1과 D2의 논리 조합 연산을 통해 TXA를 출력하기 위한 HS TX를 구동하는 신호, PU_A, VCM_A, PD_A를 생성한다. 이때 PU_A, VCM_A, 그리고 PD_A 신호 사이의 타임 스큐를 제거함으로 TXA의 신호 보존성을 개선한다. 또한 D1과 D3, D2와 D3의 논리 조합 연산을 통해 각각 TXB와 TXC를 출력하기 위한 HS TX의 제어 신호를 생성한다.

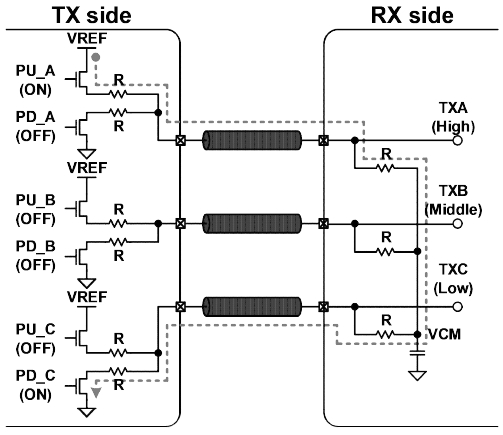

그림 6은 MIPI C-PHY TX Logic의 출력신호에 의해 동작하는 HS TX의 동작 개념도이다[2]. MIPI C-PHY는 도통된 경로의 저항값의 비에 따라 출력 전압이 결정되어 이의 전압값을 데이터로 송수신하는 전압 모드 signaling을 이용한다. 위 개념도는 TXA가 high, TXB가 middle, TXC가 low인 경우를 나타낸다. TXA가 high를 출력하기 위해 PU_A와 PD_A가 각각 high와 low가 되며, TXC가 low를 출력하기 위해 PU_C는 low 그리고 PD_C는 high의 상태를 가진다. 위 개념도에서는 트랜지스터의 턴-온 저항이 이상적으로 0 ohm으로 가정함으로 TXA와 TXC는 각각 3/4·VREF와 1/4·VREF의 전압값으로 결정된다. TXB는 수신단에서 on-die termination을 통한 전압 분배에 따라 middle 전압(2/4·VREF)으로 결정된다. 이에 따라 이상적으로는 송신단에서 PU_B와 PD_B를 모두 off 시킴으로 floating 상태를 만들어 별도의 전압을 출력하지 않아도 된다. 이와 같은 동작을 통해 3개의 HS TX는 TXA, TXB, 그리고 TXC 출력에 3-level 신호를 출력하게 된다.

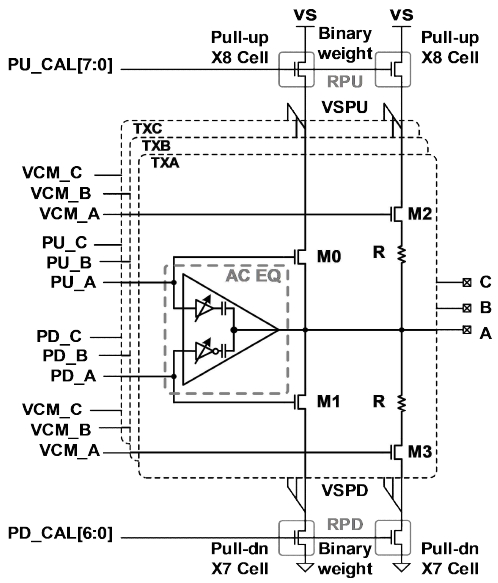

그림 7은 AC 등화기를 포함하는 HS TX의 회로도를 나타낸다[6][12]. High와 low를 출력하기 위한 M0와 M1, middle을 출력하기 위한 M2와 M3, 그리고 턴-온 저항을 조절하기 위한 RPU와 RPD로 구성된다. PU_A가 high인 경우 M0가 도통되어 신호 A는 high가 된다. 마찬가지로 PD_A가 high인 경우 M1이 도통되어 신호 A는 low가 된다. 그림 6에 따르면 M2, M3 경로가 존재하지 않아도 수신단에 형성되는 VCM 전압에 의해 middle 신호가 생성되지만, M2와 M3 경로로 이용하여 송신단의 반사파 없이 빠르게 middle 신호를 안정시킬 수 있다. 한편, RPU와 RPD의 임피던스는 각각 M0와 M1의 턴-온 저항과 더해져 터미네이션을 위한 저항을 가진다.

터미네이션 저항값은 RPU와 RPD를 제어함으로 그 값이 결정되는데, RPU와 RPD의 저항값은 각각 PU_CAL[7:0]과 PD_CAL[6:0] 코드에 의해 NMOS 트랜지스터의 크기를 조정함으로 제어된다. NMOS 트랜지스터가 턴-온이 되면 deep triode region에서 동작함으로 식 (4)와 (5)와 같이 결정된다. 일반적으로 RPU의 VSPU와 VS는 RPD의 VSPD보다 상대적으로 큰 값을 가지기 때문에 동일한 임피던스를 위해 pull-up 저항을 제어하는 RPU를 위한 NMOS 트랜지스터를 더 크게 설계한다.

| (4) |

| (5) |

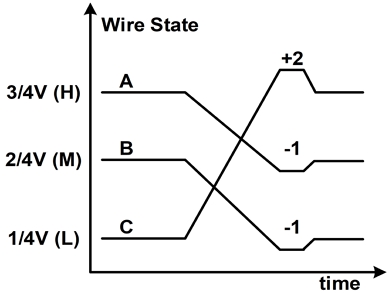

그림 7의 AC 등화기(AC EQ)는 PU_A와 PD_A를 수신하여 커패시터를 통해 합성된 고주파 신호를 TXA, TXB, TXC로 출력한다. AC_EQ에서는 PU_A 및 PD_A 신호에 대해 버퍼 및 인버팅 동작 수행에 delay 및 구동력을 제어함으로 M0와 M1의 구동하는 신호와의 타임 스큐를 제거함과 동시에 AC 등화의 strength를 조절한다. 그림 8은 AC EQ에 의해 보상되는 와이어의 상태변화를 보여준다. 3 전압 레벨을 표현해야 하는 MIPI C-PHY Transmitter의 HS TX는 데이터가 천이하는 레벨에 따라 주파수 보상의 크기를 비례적으로 가변시킨다[6]. 라인 C에서 low에서 high로 천이할 때 PU_A신호는 로직 ‘0’에서 ‘1’로 천이하고, PD_A 신호는 로직 ‘1’에서 ‘0’으로 천이한다. 이 경우 AC EQ의 strength를 +2로 설정한다. 라인 A의 경우는 high에서 middle로 천이하는 경우인데, PU_A만 ‘1’에서 ‘0’으로 천이한다. 이 경우는 –1의 strength로 AC EQ를 제어한다. 즉, 현재 상태 혹은 다음 상태, 그리고 middle 레벨로의 천이 여부를 고려하여 와이어의 상태가 변화하는 정도에 맞추어 고주파 이득을 제어하여 전송선에 의한 손실을 보상한다.

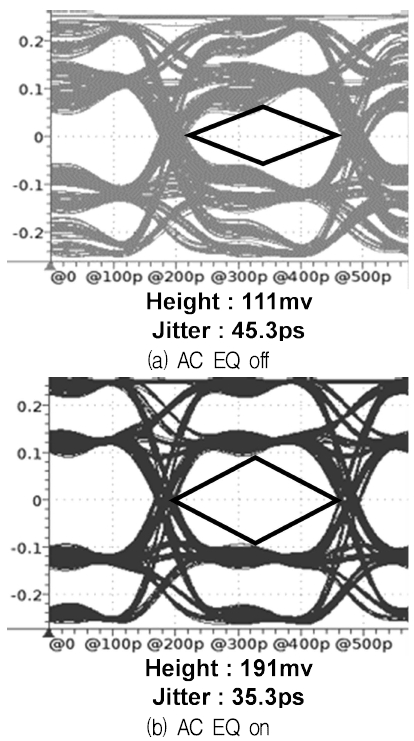

그림 9는 3.5-Gsymbol/s의 데이터 전송률에서 HS TX 블록의 시뮬레이션 결과를 보여준다. AC 등화기의 동작으로 인해 출력된 신호의 아이 다이어그램은 AC EQ를 적용하지 않은 경우 대비 27% 개선된 191 mV의 전압 크기를 가진다. AC EQ의 적용은 출력 신호의 peak-to-peak 타임 지터도 45.3ps에서 35.2 ps로 줄어들게 함으로 신호 보존성을 개선하는 것이 확인된다.

Ⅲ. 칩 제작 및 측정 결과

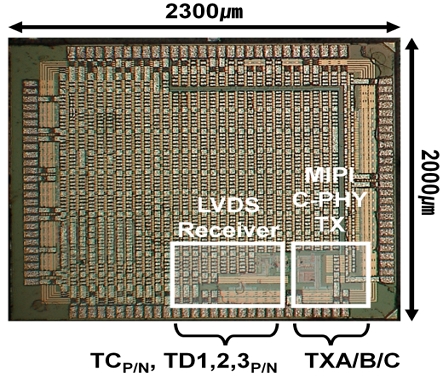

제안된 MIPI C-PHY 송신 브릿지 칩은 1.1V의 공급전압을 이용하는 40-nm CMOS 공정에서 구현되었다.

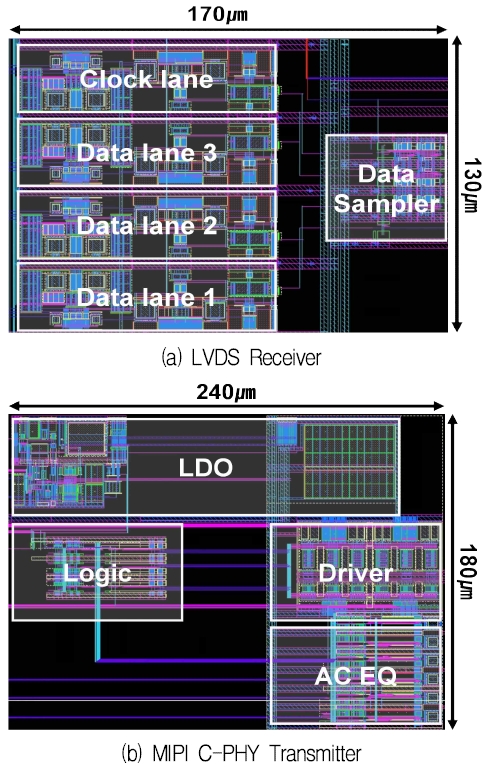

그림 10은 설계된 MIPI C-PHY 송신 브릿지 칩의 레이아웃을 보여준다. 3 개의 데이터 레인과 1개의 클록 레인으로 구성된 그림 10(a)의 LVDS Receiver는 170㎛ × 130㎛의 면적을 가진다. 1 레인당 4.5mA의 전류 소모를 하며, 전체 블록에서 18mA의 전류를 소모한다. 그림 10(b)는 MIPI C-PHY Transmitter의 레이아웃으로 라우팅을 포함하여 240㎛ × 180㎛의 면적을 가진다. Core power와 I/O power 분리를 위해 좌우로 세부 셀을 분리하였고, HS TX의 전원을 공급하는 LDO(low drop output) 블록의 패스-트랜지스터는 해당 블록의 상단에 배치되었다. MIPI C-PHY TX Logic에서 약 4.1mA, AC EQ에서 약 1.1mA 그리고 HS TX에서 약 6.9mA를 소모한다. MIPI C-PHY Transmitter는 버퍼를 포함하여 총 12.1mA의 전류를 소모한다. 그림 11은 제작된 MIPI C-PHY 송신 브릿지 칩의 사진이며, 그림 10에 나타난 블록이 포함되어 4 레인의 LVDS Receiver와 1 레인의 MIPI C-PHY Transmitter가 제작되었다.

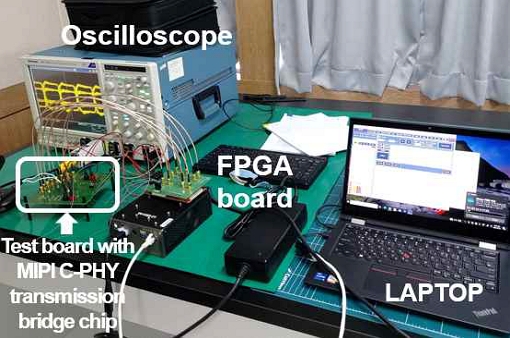

그림 12는 MIPI C-PHY 송신 브릿지 칩을 검증하기 위한 측정환경을 보여준다. LAPTOP을 통해 FPGA의 LVDS 신호와 AC 등화기의 세기 및 바이어스 전류를 조절하는 제어 신호를 설정한다. 제작된 MIPI C-PHY 송신 브릿지 칩을 포함하는 테스트 보드는 전원 잡음 감쇄를 위해 core power와 I/O power를 분리하였다. MIPI C-PHY 송신 브릿지 칩은 FPGA로부터 60 cm의 SMA 케이블과 7.5 cm의 FR4 PCB 채널을 통해 4 레인의 LVDS 신호를 수신받는다. 또한, 제작된 MIPI C-PHY 송신 브릿지 칩의 1 레인을 위한 3개의 출력 신호는 각각 1.2 cm의 FR4 PCB를 통해 출력되어 PCB 상에서 50Ω의 저항에 의해 터미네이션된다. Tektronix DPO71604C 모델의 오실로스코프 및 active probe를 이용하여 MIPI C-PHY 송신 브릿지 칩의 고속 출력 신호의 특성을 평가하였다.

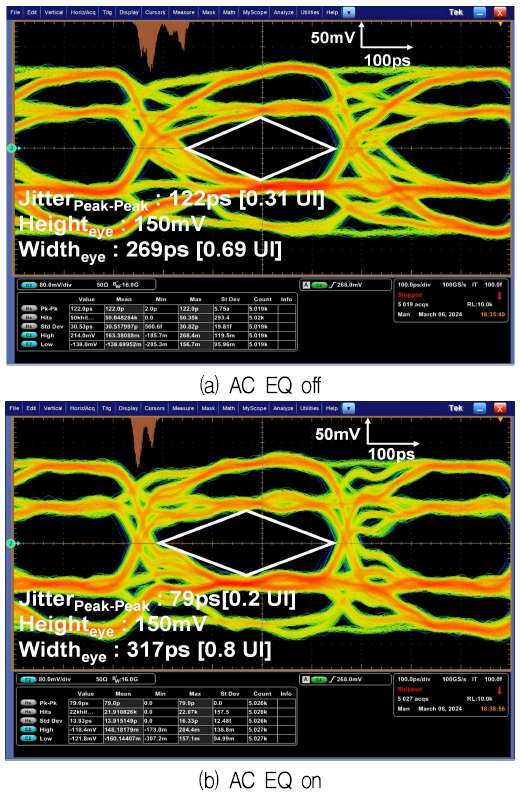

그림 13은 그림 12의 측정환경에서 평가된 MIPI C-PHY 송신 브릿지 칩의 측정 결과이다. 2.56-Gsymbol/s의 전송률을 가지는 MIPI C-PHY의 출력 파형이 측정되었다. 제작된 MIPI C-PHY 송신 브릿지 칩이 TQFP 100pin의 패키지를 사용함으로 wire bonding을 포함한 커패시터 및 인덕터의 기생 성분이 증가하여 HS TX의 출력 파형에 반사파를 포함한 신호 보존성의 손실이 나타났으나 MIPI C-PHY의 3-레벨의 전압을 가지는 signaling이 차동의 파형으로 측정되었다. 그림 13(a)는 AC 등화기가 비활성화된 상황에서 측정된 MIPI C-PHY Transmitter의 측정 결과로 아이 다이어그램의 전압 크기는 150 mV이며, peak-to-peak 타임 지터는 122 ps이다. 그림 13(b)는 AC 등화기의 적용으로 신호 보존성이 개선된 MIPI C-PHY의 출력신호의 특성을 보여준다. 측정된 아이 다이어그램의 전압 크기는 150 mV로 증가하였으며, peak-to-peak 타임 지터는 79 ps로 줄어서 약 35%의 지터 특성이 개선되었다.

Ⅳ. 결론 및 향후 과제

본 연구에서는 모바일 디스플레이 구동 및 평가를 위해 사용되는 FPGA 기반 패턴 발생기에 사용되기 위한 MIPI C-PHY 송신 브릿지 칩을 1.1 V의 공급전압을 이용하는 40-nm CMOS 공정에서 구현하였다. 제안된 MIPI C-PHY 송신 브릿지 칩은 FPGA로부터 4 레인의 LVDS 신호를 수신하여 MIPI C-PHY version 1.0을 지원하는 2.56 Gsymbol/s의 데이터 전송 속도의 데이터를 1 레인을 통해 출력한다. 구현된 MIPI C-PHY 송신 브릿지 칩은 33.11 mW의 전력을 소모한다.

Acknowledgments

This work was supported by the Regional Industry-based Talent Development and Developing Innovative Technology Program

References

- MIPI Alliance Specification for C-PHY, version 1.0, MIPI Alliance, Aug. 2014. http://www.mipi.org/specifications/c-phy, [accessed: Jun. 10, 2024]

-

P. Lancheres and M. Hafed, "The MIPI C-PHY Standard: A generalized Multiconductor Signaling Scheme", IEEE Solid-State Circuits Magazine, Vol. 11, No. 2, pp. 69-77, Jun. 2019.

[https://doi.org/10.1109/MSSC.2019.2910616]

- S.-W. Park and Y.-H. Lee, "Serial Interface for Mobile Processors", The Journal of Korean Institute of Information Technology, Vol. 7, No. 1, pp. 38-43, Feb. 2009.

-

H.-S. Kim, P.-H. Lee, J.-W. Han, S.-H. Shin, S.-W. Baek, D.-I. Park, Y. Seo, and Y.-C. Jang, "A 10 Gbps D-PHY Transmitter Bridge Chip for FPGA-based Frame Generator supporting MIPI DSI of Mobile Display," IEICE Transaction on Electronics, Vol. E100-C, No. 11, pp. 1035-1038, Nov. 201.

[https://doi.org/10.1587/transele.E100.C.1035]

-

P.-H. Lee and Y.-C. Jang, "A 3 Gbps/lane MIPI D-PHY Transmission Buffer Chip", IEICE Transaction on Fundamentals, Vol. E102-A, No. 6, pp. 783-787, Jun. 2019.

[https://doi.org/10.1587/transfun.E102.A.783]

-

P.-H. Lee and Y.-C. Jang, "A 6.84 Gbps/lane MIPI C-PHY Transceiver Bridge Chip With Level-Dependent Equalization", IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 67, No. 11, pp. 2672-2676, Nov. 2020.

[https://doi.org/10.1109/TCSII.2019.2962839]

-

K.-M. Kim, S. Hwang, J. Song, and C. Kim, "An 11.2-Gb/s LVDS Receiver With a Wide Input Range Comparator", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 10, pp. 2156-2163, Oct. 2014.

[https://doi.org/10.1109/TVLSI.2013.2288420]

-

Y. Chen, P.-I. Mak, and Y. Wang, "A Highly-Scalable Analog Equalizer Using a Tunable and Current-Reusable Active Inductor for 10-Gb/s I/O Links", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 23, No. 5, pp. 978-982, May 2015.

[https://doi.org/10.1109/TVLSI.2014.2318733]

-

S. Gondi and B. Razavi, "Equalization and clock and data recovery techniques for 10-Gb/s CMOS serial-link receivers", IEEE Journal of Solid-State Circuits, Vol. 42, No. 9, pp. 1999-2011, Sep. 2007.

[https://doi.org/10.1109/JSSC.2007.903076]

-

S. Parikh, T. Kao, Y. Hidaka, J. Jiang, A. Toda, S. Mcleod, W. Walker, Y. Koyanagi, T. Shibuya, and J. Yamada, "A 32Gb/s wireline receiver with a low-frequency equalizer, CTLE and 2-tap DFE in 28nm CMOS", IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, Feb. 2013.

[https://doi.org/10.1109/ISSCC.2013.6487622]

-

J. Bae, M. Song, B. Kim, J. Lee, W. Park, and J.-H. Chun, "A 11.4-Gbps/lane MIPI 32-bit C-PHY and D-PHY combo transmitter with 3-tap FFE", IEEE Asian Solid-State Circuits Conference, Taipei, Taiwan, pp. 1-3, Dec. 2022.

[https://doi.org/10.1109/A-SSCC56115.2022.9980792]

-

K.-S. Kwak, J.-H. Ra, H.-S. Moon, S.-K. Hong, O.-K. Kwon, "A Low-Power Two-Tap Voltage-Mode Transmitter With Precisely Matched Output Impedance Using an Embedded Calibration Circuit", IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 63, No. 6, pp. 573-577, Jun. 2016.

[https://doi.org/10.1109/TCSII.2016.2530818]

2022년 2월 : 국립금오공과대학교 전자공학과(공학사)

2024년 2월 : 국립금오공과대학교 전자공학과(공학석사)

2024년 7월 ~ 현재 : (유) Synopsys korea 연구원

관심분야 : CDR 포함 고속 인터페이스 송수신기 회로

2023년 2월 : 국립금오공과대학교 전자공학과(공학사)

2023년 2월 ~ 현재 : 국립금오공과대학교 반도체시스템공학과 석사과정

관심분야 : 고속 인터페이스를 위한 송수신기 회로

1997년 3월 : 대전폴리텍 전자공학과(공학사)

2001년 10월 ~ 2011년 7월 : ㈜아원 기술연구소 연구원

2011년 7월 ~ 현재 : ㈜에스엠디에스피 연구소 HW 파트 수석연구원

관심분야 : 고속 인터페이스를 위한 송수신기 회로

1999년 2월 : 경북대학교 전자전기공학부(공학사)

2001년 2월 : 포항공과대학교 전자공학과(공학석사)

2005년 2월 : 포항공과대학교 전자공학과(공학박사)

2005년 3월 ~ 2009년 8월 : 삼성전자 반도체총괄 책임연구원

2009년 9월 ~ 현재 : 국립금오공과대학교 전자공학부 교수

관심분야 : 아날로그-디지털 변환기 및 고속 인터페이스를 위한 클록발생기와 송수신기 포함 아날로그집적회로