주파수 변환 방식을 이용한 양 3차회선 스케일러의 하드웨어 설계

초록

디스플레이 산업의 발전으로 디지털 기기에서는 많은 화소를 표현할 수 있는 이미지 표준을 요구하고 있다. 이와 같은 요구조건을 만족하기 위해 고해상도의 이미지를 생성하는 다양한 업스케일링 기술들이 연구되고 있다. 업스케일링을 위한 기술로는 딥러닝 모델을 사용하는 방식과 전통적인 보간을 사용하는 방식이 존재한다. 그 중 전통적인 보간 방식은 컴퓨터 비전, 의료 영상처리 그리고 영상 복원 등의 분야에서 사용되고 있다. 본 논문에서는 대표적인 3가지 보간 방식 중 가장 많이 활용되는 양 3차회선 보간 알고리즘을 이용한 스케일러의 하드웨어를 제안한다. 제안하는 하드웨어는 주파수 변환 방식을 사용하여 이미지 처리 속도에 큰 영향을 미치는 수평 공백 구간을 최소화하였다. 하드웨어는 field programmable gate array 환경에서 논리 합성을 진행한 결과를 바탕으로 QHD 표준 이미지에서 실시간 처리가 가능함을 검증한다.

Abstract

The development of the display industry has led to a demand for image standards that can express a large number of pixels in digital devices. To meet this demand, various up-scaling techniques that generate high-resolution images have been studied. Two types of up-scaling techniques are commonly used: deep learning models and traditional interpolation methods. Traditional interpolation methods are used in fields such as computer vision, medical image processing, and image restoration. In this paper, we propose hardware for a scaler using the widely-used bicubic interpolation algorithm among the representative three interpolation methods. The proposed hardware minimizes the horizontal blank interval, which significantly affects image processing speed, by using a frequency conversion method. The hardware is validated for real-time processing on QHD standard images based on logic synthesis in a field programmable gate array environment.

Keywords:

scaler, up-scaling, down-scaling, real-time processing, FPGAⅠ. 서 론

현재 많은 디스플레이 기기에서 사용되는 이미지는 표현되는 픽셀(또는 화소)의 수가 많은 고해상도 이미지를 요구한다. 따라서 고해상도 이미지의 수요가 증가하였고 저해상도 이미지를 고해상도로 변환하는 업스케일링 기술의 연구가 활발히 진행되고 있다. 그러나 고해상도 이미지의 경우 이미지를 구성하는 픽셀의 수가 많으므로 분석에 필요한 시간이 증가한다. 따라서 고해상도 이미지를 저해상도 이미지로 변환하는 다운스케일링 기술의 연구도 중요하다. 이러한 이미지 스케일링 기술은 크게 딥러닝 그리고 전통적인 보간 알고리즘을 사용하는 방식으로 나뉜다.

딥러닝을 사용하는 방식[1]은 전통적인 보간 알고리즘을 사용하는 경우보다 높은 품질의 이미지를 생성하지만, 스케일링을 진행할 때 많은 시간이 소요된다. 전통적인 보간 알고리즘은 딥러닝을 사용하는 경우와 비교하였을 때 생성되는 이미지의 품질은 떨어지지만, 비교적 간단한 방식으로 제한된 환경에서 효율적인 사용이 가능하다.

전통적인 보간은 대표적으로 최근접 이웃 보간(NNI, Nearest Neighbor Interpolation)[2], 양 선형 보간(BLI, Bilinear Interpolation)[3] 그리고 양 3차회선 보간(BCI, Bicubic Interpolation)[4]이 있다. 이 중 BCI 알고리즘은 다른 2가지 보간 방식보다 높은 품질의 이미지를 생성한다. 그러나 BCI 알고리즘을 디지털 기기에 적용하는 경우 소프트웨어만으로 실시간 처리를 구현하기에는 어려움이 있다. 따라서 실시간 처리를 위해서는 전용 하드웨어가 필요하다.

스케일러의 하드웨어는 이미지 확대 시 증가한 출력 데이터를 생성하기 위한 시간이 필요하다. 이와 같은 제약 조건은 입력 수평 동기 신호의 공백 구간을 증가한 출력 데이터의 크기만큼 늘려 시간을 할당하는 방식과 dual-clock을 이용한 주파수 변환 방식으로 조건을 만족할 수 있다[5]. 이때, 주파수 변환 방식은 증가한 데이터를 처리하기 위한 공백 구간을 사용하지 않기 때문에 실시간 처리에 적합한 구조라고 볼 수 있다.

본 논문에서는 BCI 알고리즘을 이용해 각 축으로 0.2~2.0배의 대칭 및 비대칭 축소와 확대가 가능한 스케일러의 하드웨어를 설계한다. 설계되는 하드웨어는 주파수 변환 방식을 사용하며, 축소의 경우 하드웨어의 크기에 큰 영향이 없지만 0.2배까지 축소가 가능하도록 설정하였다. 확대의 경우 비율에 비례하여 출력 데이터의 크기가 커져, 결과 이미지를 생성할 때 필요한 클록 사이클이 증가하므로 이미지 처리 속도가 감소한다. 따라서 최대 확대 비율은 QHD 표준 이미지를 실시간으로 처리가 가능한 2.0배로 설정하였다. 실시간 처리의 기준은 NTSC의 방송 규격인 30 FPS(Frames Per Second)를 기준으로 한다. 설계한 하드웨어는 하드웨어 기술 언어인 Verilog를 통해 설계하였으며, FPGA(Field Programmable Gate Array) 환경에서 구현한다.

Ⅱ. 관련 연구

2.1 양 3차회선 보간

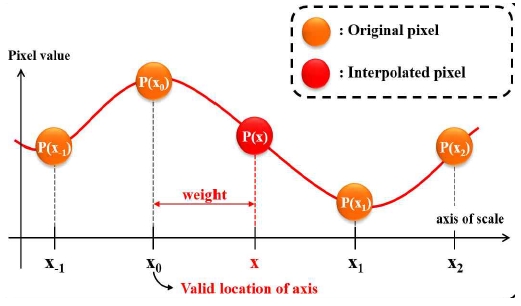

BCI 알고리즘은 보간을 진행할 때 유효한 픽셀의 위치 그리고 보간되는 위치와 유효한 픽셀의 위치 사이의 거리인 가중치 정보가 필요하다[6].

BCI 알고리즘은 그림 1의 CI(Cubic Interpolation)을 이미지의 각 축으로 진행하는 방식이다. 인접한 4개의 픽셀값을 이용해 3차 다항식을 생성하고 보간되는 위치의 픽셀값을 구한다. x위치의 픽셀이 가지는 값은 P(x)와 같이 표현된다. 보간되는 픽셀이 P(x)라면 유효한 픽셀의 위치는 x0가 되며, x와 x0 사이의 거리는 가중치를 나타낸다. 보간되는 픽셀 P(x)의 값을 구하기 위해 인접한 원본 픽셀 P(x-1), P(x0), P(x1) 그리고 P(x2)의 값을 참조한다.

보간되는 픽셀의 값을 구하는 3차 다항식은 식 (1)과 같다[6].

| (1) |

식 (1)의 x는 보간되는 픽셀의 위치를 나타낸다. a, b, c 그리고 d는 다항식의 계수이다. 다항식을 풀게 되면 식 (2)를 얻을 수 있다[6].

| (2) |

식 (2)에서 구한 3차 다항식의 계수와 가중치를 이용하면, 보간되는 픽셀 P(x)의 값을 구할 수 있다. Y축의 보간을 진행한 후 X축의 보간을 진행하는 경우라면, Y축으로 보간된 4개의 픽셀을 이용해 X축으로 보간되는 픽셀의 값을 구한다. 즉, BCI 알고리즘은 인접한 16개의 픽셀을 이용해 이미지 보간을 진행하는 것을 알 수 있다. NNI, BLI 그리고 BCI는 각각 인접한 1개, 4개 그리고 16개의 픽셀을 참조해 보간을 진행한다[2]-[4]. 따라서 BCI는 3가지 보간 방식 중 가장 많은 픽셀을 참조해 가장 높은 품질의 이미지를 생성할 수 있다.

2.2 알고리즘 평가

보간 알고리즘의 평가를 위해 정량 및 정성적 평가를 진행한다. 정량적 평가에는 PSNR(Peak Signal-to-Noise Ratio)를 사용하였다[7]. PSNR은 최대 신호에 대한 잡음비로 보간을 진행한 이미지와 원본 이미지의 픽셀값을 비교하여, 정보의 손실 정도를 나타낸다. 높은 수치일수록 정보의 손실이 적음을 의미한다. PSNR 측정은 식 (3)을 이용한다.

| (3) |

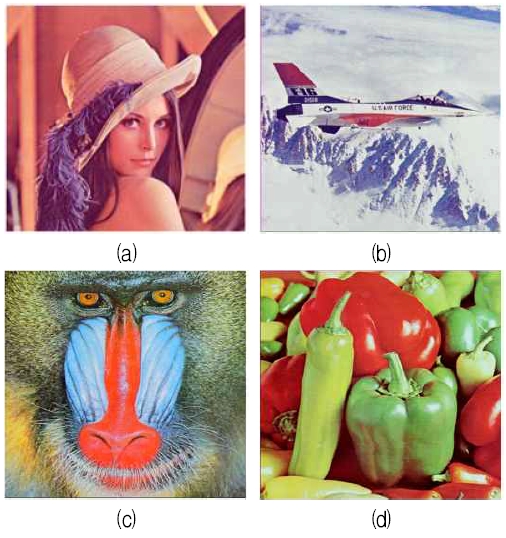

식 (3)의 MAX는 이미지의 픽셀이 갖는 최댓값을 의미한다. 8-bit 이미지를 사용한다고 가정하였을 때 255의 값을 가진다. MSE(Mean Square Error)는 원본 이미지와 보간된 이미지의 픽셀값 차이를 제곱한 후 평균을 취한 값이다[7]. 원본 이미지와 비교를 위해 평가되는 보간 방식으로 1.6배 확대 후 축소 과정을 통해 원본 이미지와 동일한 크기의 이미지를 생성한 후 수치를 측정한다. 평가에는 그림 2의 512×512 Lena, Baboon, Peppers 그리고 Airplane 이미지를 사용하였으며, 이미지의 각 채널(RGB)에 보간을 진행한 결과 이미지를 이용해 평가한다.

표 1은 그림 2의 실험 이미지를 이용해 3가지 보간 방식으로 생성된 결과 이미지의 PSNR을 측정한 결과이다. 표 1을 통해 NNI를 사용할 때 모든 실험 이미지에서 가장 낮은 PSNR 수치를 보이며, BCI의 경우 평균 PSNR 수치가 3가지 방식 중 2번째로 높은 BLI와 평균 수치를 비교하였을 때 6.72dB 더 높은 수치를 보인다.

즉, 3가지 보간 방식 중 BCI를 사용할 때 원본 이미지의 정보 손실이 가장 적은 것을 알 수 있다.

BCI는 3가지 보간 방식 중 가장 높은 PSNR 수치를 보이지만, 연산량이 많아 하드웨어로 설계 시 하드웨어의 복잡도가 증가한다. 따라서 연산량을 줄이는 방식의 연구가 진행되고 있다[8]. 그러나 이러한 방식은 BCI와 비교하였을 때 생성되는 이미지의 품질이 낮아지는 단점이 있다.

표 2는 참고문헌[8]의 보간 과정과 본 논문에서 사용되는 BCI 방식의 PSNR 수치 평가를 진행한 결과이다. 참고문헌[8]에서는 BLI 그리고 BCI를 결합한 이중 선형-3차회선 보간을 제안하며, 보간에 필요한 연산량과 설계되는 하드웨어의 크기를 줄였다. 그러나 이와 같은 방식은 BCI를 사용한 경우와 비교하였을 때 PSNR 수치가 떨어지는 것을 볼 수 있다. 즉, BCI를 사용하는 스케일러의 하드웨어와 비교하였을 때 하드웨어의 크기는 줄일 수 있지만 생성되는 결과 이미지의 품질은 떨어진다.

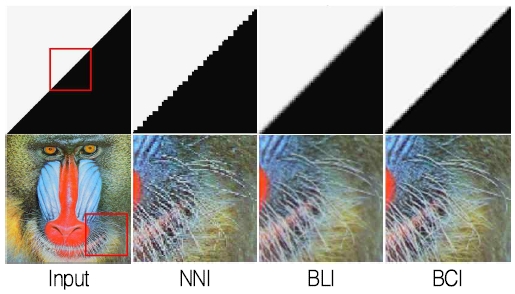

그림 3은 입력에 사용된 이미지와 정성적 평가를 위해 3가지 보간 방식으로 1.6배 축소 후 확대를 진행한 출력 이미지를 나타낸다. Diagonal 이미지의 확대된 부분(붉은 네모)을 보면, NNI를 사용한 경우 Aliasing 현상이 발생하는 것을 확인할 수 있다. BLI와 BCI를 사용한 경우는 자연스러운 이미지가 생성된 것을 볼 수 있다. 또한 Baboon의 수염 부분(붉은 네모)을 보면, NNI를 사용했을 때 이미지가 부자연스러운 것을 볼 수 있다. BLI와 BCI의 경우 유사한 이미지를 생성하지만, BCI를 사용했을 때 이미지가 더 선명함을 볼 수 있다.

정량 및 정성적 평가를 통해 전통적인 3가지 보간 방식과 연산량을 줄이기 위한 보간 방식 중 BCI를 사용할 때 가장 높은 품질의 이미지를 생성하는 것을 확인하였다. 따라서 본 논문에서는 가장 높은 성능을 보이는 BCI 알고리즘을 사용하는 스케일러의 하드웨어를 설계한다.

2.3 Dual-clock을 이용한 주파수 변환 방식

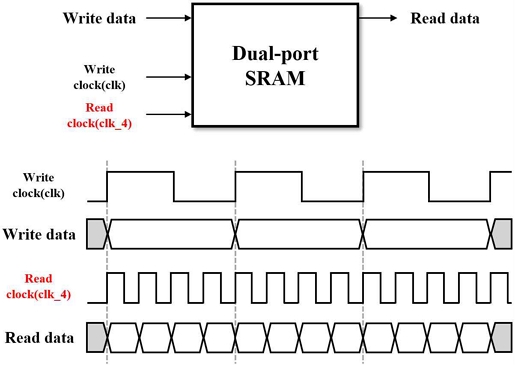

주파수 변환 방식을 사용하는 스케일러의 하드웨어는 확대 동작으로 증간된 출력 데이터를 처리하기 위해 각 축의 최대 확대 비율에 비례하는 주파수의 클록을 추가로 사용한다. 각 축으로 최대 확대 비율이 2.0배일 때, 입력 데이터를 읽어오는 클록보다 4배 높은 주파수를 가지는 클록을 사용한다.

하드웨어에서는 높은 주파수 클록과 DPRAM (Dual-Port SRAM)을 사용해 주파수 변환을 진행한다.

그림 4는 DPRAM을 이용해 주파수 변환을 진행하는 과정을 보인다. 입력 데이터를 읽어오는 클록(clk)을 이용해 데이터를 DPRAM에 저장한 후 4배 빠른 주파수 클록(clk_4)으로 저장된 데이터를 읽어온다. 이러한 방식으로 하나의 데이터가 입력될 때 4개의 데이터를 처리할 수 있다.

Ⅲ. 제안하는 하드웨어 구조

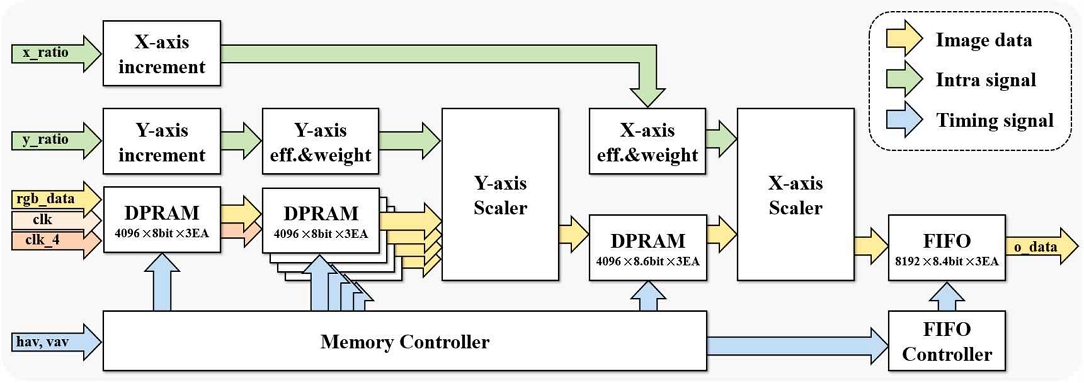

그림 5는 제안하는 스케일러 하드웨어의 세부 구조를 나타낸다. 하드웨어는 DCI 4K 표준 이미지(4096×2160)를 지원할 수 있도록 설계하였다. 입력 데이터는 DPRAM을 이용해 주파수 변환을 진행한다. 변환된 데이터는 Y축 보간에 필요한 인접한 라인의 값을 저장하기 위해 4개의 라인메모리에 저장된다. 저장된 데이터는 계산된 유효한 픽셀 위치와 가중치를 이용해 보간에 사용되며, Y축 보간이 진행된 라인 데이터는 다시 DPRAM에 저장된다. 보간된 데이터를 메모리에 저장하는 이유는 X축의 보간을 진행할 때 인접한 픽셀의 값을 참조하기 위함이다. 이미지 데이터는 실시간으로 입력되고 연산되기 때문에 지나간 데이터는 사용하지 못한다. 따라서 Y축으로 보간된 라인 데이터를 메모리에 저장한 후 사용한다. X축의 보간도 Y축과 마찬가지로 계산된 X축의 유효한 픽셀 위치와 가중치 정보를 이용하며, DPRAM에 저장된 라인 데이터를 사용해 X축 보간을 진행한다. 보간된 데이터는 first-in-first-out (FIFO)에 저장되는데, FIFO는 축소의 경우 보간된 라인 데이터가 불연속적으로 생성될 때 연속적인 출력을 만들어주며, 사용자가 손쉽게 데이터를 활용할 수 있도록 한다.

제안하는 스케일러의 하드웨어는 DPRAM을 추가로 사용해 주파수 변환을 진행하기 때문에 메모리를 추가로 사용하는 단점이 있다. 그러나 스케일러의 확대 동작을 위해 증가된 출력 데이터를 생성하기 위한 시간을 할당하지 않아, 이미지 처리 속도를 높일 수 있다.

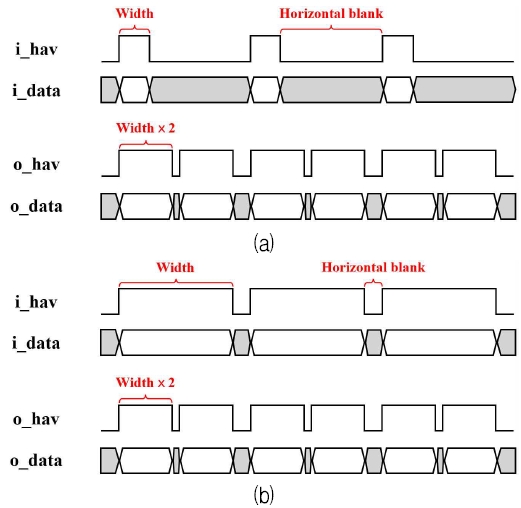

그림 6은 각 축으로 2.0배 확대 경우 단일 클록을 사용하는 방식과 주파수 변환 방식을 사용하는 하드웨어의 타이밍 다이어그램을 나타낸다. i_hav는 입력 horizontal active video 신호를 나타낸다.

그림 6에서 단일 클록을 사용하는 하드웨어의 경우 입력 데이터가 들어오는 시간 동안 증가한 출력 데이터를 생성할 수 없기 때문에 증가한 데이터만큼 공백 구간을 늘려준 것을 볼 수 있다.

이러한 공백 구간은 이미지 처리에 필요한 시간을 증가시키므로 이미지 처리 속도가 감소하는 단점이 있다. 그러나 주파수 변환 방식은 공백 구간을 늘리는 것이 아닌 높은 주파수 클록을 이용해 입력 이미지 데이터가 들어오는 시간 동안 출력 데이터를 생성할 수 있다. 따라서 스케일러의 하드웨어가 이미지를 처리하는 데 필요한 시간을 줄일 수 있다.

Ⅳ. 하드웨어 구현 결과

스케일러의 하드웨어는 Xilinx Vivado v2023.1을 이용해 FPGA 환경에서 논리 합성을 진행한다.

표 3의 합성 결과를 보면 CLB Register는 8,563만큼, CLB LUT는 9,645만큼 그리고 Block RAM의 경우 30의 자원을 사용하는 것을 알 수 있다. 하드웨어의 최대 동작 주파수는 447.828MHz이다. 이때 최대 동작 주파수는 주파수 변환을 진행해 출력단에서 사용되는 클록의 주파수를 나타낸다. 최대 동작 주파수는 이미지 처리 속도를 구할 때 사용되며, 이미지 처리 속도를 나타내는 maximum processing speed (MPS)는 식 (4)를 이용해 구할 수 있다[9].

| (4) |

식 (4)의 fmax는 최대 동작 주파수를 나타내며, 분모의 H, W, BV 그리고 BH는 수직 라인의 수, 수평 구간의 픽셀 수, 프레임 사이의 공백 구간 그리고 수평 라인의 공백 구간을 의미한다. 하드웨어의 최대 동작 주파수는 출력단의 클록을 기준으로 측정되어 클록 사이클도 출력을 기준으로 측정된다. 따라서 4배 높은 주파수를 사용하므로 입력 클록 사이클의 4배 크기를 가진다. QHD(2560×1440) 표준 이미지를 기준으로 식 (4)에서 사용되는 세부 크기를 구하면 다음과 같다. fmax는 447.828MHz이고 H, W, BV 그리고 BH는 10,240, 5760, 4 그리고 4이다. 즉, 클록 사이클은 14,761,604가 된다. 클록 사이클을 동작 주파수에 나눈 값인, 이미지 처리 속도를 측정하면 30.34fps로 설계되는 스케일러의 하드웨어는 QHD 표준 이미지에서 실시간 처리를 만족하는 것을 알 수 있다.

Ⅴ. 결 론

본 논문에서는 주파수 변환 방식을 통해 실시간 처리가 가능한 양 3차회선 스케일러의 하드웨어를 설계하였다. 알고리즘의 정량 및 정성적 평가로 연산량을 줄인 보간 방식, NNI 그리고 BLI 알고리즘과 비교해 설계하는 하드웨어에서 사용되는 BCI 알고리즘의 성능이 가장 우수함을 보였다. 또한 설계된 하드웨어는 dual-clock을 이용한 주파수 변환 방식으로 이미지 처리 속도에 영향을 주는 수평 공백 구간을 추가로 사용하지 않고 입력 이미지가 들어오는 시간동안 출력 데이터를 생성할 수 있도록 설계하였다. 이와 같은 방식으로 이미지 처리 속도를 높일 수 있었으며, 실제 FPGA 환경에서 논리 합성을 진행한 결과를 바탕으로 이미지 처리 속도를 분석하였을 때, QHD 표준 이미지에서 30.34fps의 속도로 실시간 처리를 만족함을 보였다.

Acknowledgments

This paper was supported by research funds from Dong-A University

References

-

G. Song, H. Yi, C. H. Son, and H. Choo, "Super Resolution with Sparse Gradient-Guided Attention and Wavelet Loss for Suppressing Image Structural Distortion", Journal of KIIT, Vol. 20, No. 4, pp. 107-122, Apr. 2022.

[https://doi.org/10.14801/jkiit.2022.20.4.107]

-

J. Aizan, E. C. Ezin, and C. Motamed, "A Face Recognition Approach Based on Nearest Neighbor Interpolation and Local Binary Pattern", 2016 12th International Conference on SITIS, Naples, Italy, pp. 76-81, Dec. 2016.

[https://doi.org/10.1109/SITIS.2016.21]

- W. Kim and J. Kim, "An object image quality and computation complexity comparison according to implementation method and extension scale of bilinear interpolation", 2010 Autumn Annual Conference of IEIE, pp. 435-436, Nov. 2010.

-

Y. Li, F. Qi, and Y. Wan, "Improvements on bicubic image interpolation", 2019 IEEE 4th Advanced Information Technology, Electronic and Automation Control Conference (IAEAC), Chengdu, China, pp. 1316-1320, Dec. 2019.

[https://doi.org/10.1109/IAEAC47372.2019.8997600]

- S. Han, S. Jung, and B. Kang, "Analysis of the Image Processing Speed by Line-Memory Type", Journal of IKEEE, Vol. 27, No. 4, pp. 127-133, Dec. 2023.

- S. Y. Han and B. Kang, "A Study of the Combinatorial Interpolation Algorithm for Scaler Hardware Design", Journal of IKEEE, Vol. 27, No. 3, pp. 296-302, Sep. 2023.

-

U. Sara, M. Akter, and M. S. Uddin, "Image Quality Assessment through FSIM, SSIM, MSE and PSNR—A Comparative Study", Journal of Computer and Communications, Vol. 7, No. 3, pp. 8-18, Mar. 2019.

[https://doi.org/10.4236/jcc.2019.73002]

-

H. Moon and S. Ban, "VLSI Architecture of Digital Image Scaler Combining Linear Interpolation and Cubic Convolution Interpolation", Journal of Korea Multimedia Society, Vol. 51, No. 3, pp. 112-118, Mar. 2014.

[https://doi.org/10.5573/ieie.2014.51.3.112]

-

D. Ngo, S. Lee, U. J. Kang, T. M. Ngo, G. D. Lee, and B. Kang, "Adapting a Dehazing System to Haze Conditions by Piece-Wisely Linearizing a Depth Estimator", Sensors, Vol. 22, No. 5, pp. 1957-1981, Mar. 2022.

[https://doi.org/10.3390/s22051957]

2023년 2월 : 동아대학교 전자공학과(공학사)

2023년 3월 ~ 현재 : 동아대학교 전자공학과 석사과정

관심분야 : 영상신호처리, SoC설계

2023년 2월 : 동아대학교 전자공학과(공학사)

2023년 3월 ~ 현재 : 동아대학교 전자공학과 석사과정

관심분야 : 영상신호처리, SoC설계

1985년 : 연세대학교 전자공학과(공학사)

1987년 : 미국 University of Pennsylvania 전기공학과(공학석사)

1990년 : 미국 Drexel University 전기 및 컴퓨터공학과(공학박사)

1989년 12월 ~ 1999년 2월 : 삼성전자 반도체 수석연구원

1999년 3월 ~ 현재 : 동아대학교 전자공학과 교수

관심분야 : 영상신호처리, SoC 설계 및 무선 통신