입·출력 시간차이를 이용한 전류 부스팅 구조를 갖는 DDI(Display Driver IC)용 저소비전력 고슬루율 CMOS 버퍼증폭기 설계에 관한 연구

초록

본 논문에서는 기존 소스 드라이버 IC에서 사용되는 출력 버퍼 연산증폭기를 대신할 수 있는 저소비전력 및 높은 슬루율을 갖는 CMOS 레일-투-레일 폴디드 캐스코드 연산증폭기를 제안하였다. 제안한 연산증폭기는 저소비전력과 높은 슬루율을 갖기 위하여 입/출력의 시간 차이를 감지하여 입력단에 바이어스 전류를 충/방전 시에만 전류를 부스팅하는 회로를 추가하였다. 제안한 회로는 레일-투-레일 입력단에 간단한 구조를 추가하여 전류 부스팅 구조를 대신할 수 있게끔 설계하였다. 제안한 연산증폭기는 TSMC 0.18um 공정을 이용하여 모의실험 하였고 그 결과 10nF의 부하커패시터를 기준으로 23V/㎲의 슬루율을 보였으며 이는 기존의 회로를 사용하였을 때에 비해 약 3배 향상된 수치를 확인할 수 있었다. 또한, 본 논문에서 제안한 회로는 기존의 전류 부스팅 회로를 가지는 증폭기와 비교하였을 때 전류부스팅에 사용되는 MOSFET의 개수가 적어 소요면적도 적을 것으로 예상된다.

Abstract

In this paper, we propose a CMOS rail-to-rail folded cascode operational amplifier with low power consumption and high slew rate to replace the output buffer operational amplifier used in conventional source driver ICs. The proposed operational amplifier detects the time difference between input and output in order to have low power consumption and high slew rate, and added a circuit that boosts the current only when the bias current is charged/discharged at the input terminal. The proposed circuit is designed to replace the current boosting structure by adding a simple structure to the rail-to-rail input stage. The proposed operational amplifier was simulated using a TSMC 0.18um process. As a result, the slew rate of 23V/㎲ based on a 10nF load capacitor was obtained, which was about three times higher than that of the conventional circuit . In addition, the proposed circuit is expected to have a small area due to the small number of MOSFETs used for current boosting when compared with the conventional amplifier with current boosting circuit.

Keywords:

high performance, low power consumption, rail-to-rail op amp, slew rate, source driverⅠ. 서 론

최근 디스플레이 제품은 고해상도 및 저전력 대형 디스플레이가 주류가 되고 있다. 이에 따라서 디스플레이의 해상도 품질을 결정하는 드라이버 IC의 역할이 더욱 중요하게 되었다. 디스플레이가 대형화되면서 드라이버 IC의 부하구동능력이 중요해짐에 따라 사용되는 출력 버퍼 연산증폭기는 큰 전압이득, 저전력 소모, 높은 슬루율, 넓은 입/출력 동작영역, 낮은 입력 오프셋의 특징을 가져야 하며, 동시에 넓은 영역의 전원전압의 변화에도 일정하고 안정적인 동작 특성이 요구되어지고 있다[1]-[3]. 출력버퍼증폭기에 요구되는 특성을 만족시키기 위해 경우에 따라 B급 출력단을 추가로 연결하여 사용하는 경우도 있지만 이 경우 원하는 만큼의 슬루율이나 소비전력을 만족할 경우 반대로 이득이 심각히 저하되는 트레이드-오프 관계가 초래된다. 또한 디스플레이가 대형화되었기 때문에 늘어난 픽셀 수만큼 드라이버 IC의 출력 또한 늘어나게 되는데 이는 생산비용 증가로 이어지게 된다[4]-[7].

따라서 본 논문에서는 전류 부스팅 구조를 사용하여 슬루율과 전압 이득, 소비전력 사이에 발생하는 트레이드-오프 문제를 동시에 해결하면서 이로 인해 추가되는 회로 면적의 최소화가 가능한 버퍼증폭기를 제안하고자 한다. 특히, 넓은 입/출력 범위와 저소비전력 특성을 가지면서 입/출력 파형의 시간차이를 감지하여 동작하는 전류 부스팅 구조를 제안하였고, 이를 사용하였다.

Ⅱ. 전류 부스팅 구조의 레일-투-레일 버퍼증폭기 설계

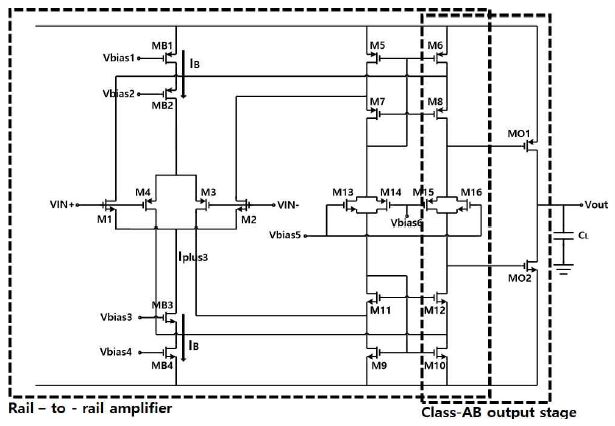

그림 1은 기존의 레일-투-레일 회로의 전체 회로도이다. 회로의 입력단은 레일-투-레일 폴디드 캐스코드 구조로 M1 ~ M16의 16개의 MOS로 구성되었다. 이 입력구조에서 nmos와 pmos로 이루어진 M1 ~ M4로 인하여 입력을 VDD ~ VSS까지 풀 스윙으로 가할 수 있다. 그 이유는 입력단의 M1 ~ M2가 nmos이기 때문에 바이어스 전압은 VDD -(VGSnmos +VDSsat) 이고, M3 ~ M4가 pmos 이므로 바이어스 전압은 VDD - (|VGSpmos +VDSsat|)로 각각 동작하면서 M5 ~ M12의 전류 미러를 통하여 출력단으로 전류를 내보내기 때문이다. 바이어스 회로는 MB1 ~ MB4로 구성하였으며, 출력단은 MO1 ~ MO2로 구성된 AB급 증폭기로 구성하였다. 하지만 이 구조는 슬루율이 너무 낮아 출력단에 큰 부하가 연결되면 제대로 동작시킬 수 없는 단점을 가지고 있다[8].

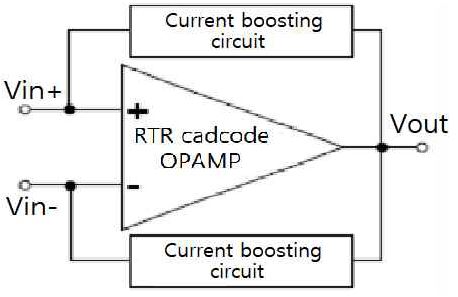

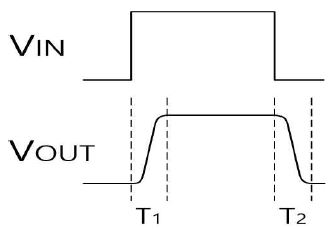

따라서 본 논문에서는 이 단점을 극복하기 위해 레일-투-레일 구조에 전류 부스팅 구조를 추가시켜 설계한 버퍼증폭기를 제안하고자 한다. 제안한 증폭기의 블록 다이어그램을 그림 2에 나타냈다. 그림 2는 입력단과 출력단 사이에 전류 부스팅 회로를 추가한 구조이다. 추가된 전류 부스팅 회로는 버퍼앰프 입력신호와 버퍼앰프 출력신호를 전류 부스팅회로 게이트 신호로 인가된다. 부하 커패시터에 충/방전되는 시간이 존재하여 출력파형은 입력파형과 시간차이가 발생하게 된다. 그 시간차이를 감지하여 상승 및 하강하는 순간에만 동작하여 전류를 발생시키게 된다. 그 결과 오직 충/방전 시간에만 전류가 증가하므로 소비전력은 최소한으로 줄이면서 상승 및 하강 슬루율이 증가되는 원리이다. 전류 부스팅 회로가 입/출력의 차이를 감지하는 원리를 그림 3에 나타냈다.

그림 3에서 보면 출력파형이 입력파형보다 늦게 충/방전 된다. 이는 출력파형이 상승 및 하강할 때 슬루율에 따라 다르기 때문에 항상 입력과 시간차이가 발생한다. 입력파형이 최대치에 도달했을 때 출력파형이 최대치까지 상승하는 구간을 T1, 입력파형이 최소치에 도달했을 때 출력파형이 최대치에서 최소치까지 하강하는 구간을 T2라고 하면 추가된 전류 부스팅 구조가 T1 -T2 시간동안 동작하면서 바이어스 전류에 추가로 전류를 발생시켜 슬루율을 증가 시키게 된다.

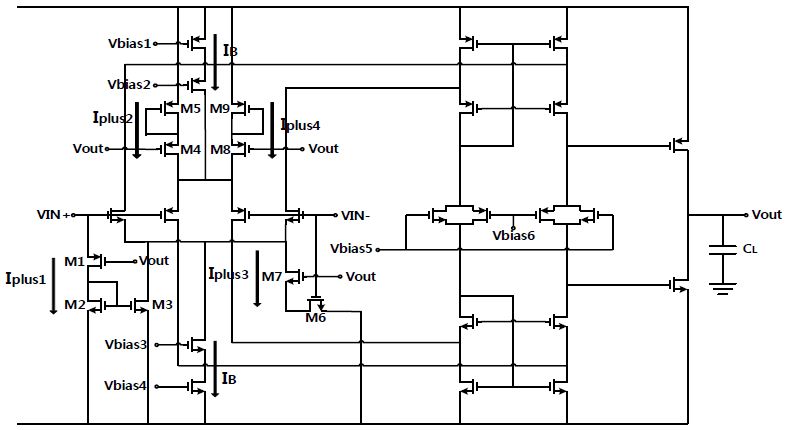

그림 4는 본 논문에서 제안한 전류 부스팅 구조를 가지는 저소비전력 및 높은 슬루율을 갖는 레일-투-레일 버퍼 증폭기의 전체 회로도이다. 슬루율을 증가시키기 위해 추가한 전류 부스팅 구조는 M1~M9로 이루어져있다. M1~M3는 비반전 입력단의 nmos가 동작할 때 상승 슬루율을 증가시키는 역할을 한다. M1은 입력파형과 출력파형 사이의 차이를 감지하여 추가적인 전류를 발생시키는 스위치 역할을 하고, M2와 M3는 전류미러 구조로 이루어져 M1이 발생시킨 전류를 바이어스 전류에 더해주는 역할을 한다. 먼저 M1의 소스와 연결되어 있는 VIN+에 입력전압이 인가되면 M1의 소스 전압은 최대값이 인가된다. 하지만 출력단과 연결된 M1의 게이트 전압은 아직 출력전압이 충전되지 못했기 때문에 최소값이 인가된다. 따라서 M1은 pmos의 포화조건인 VGS1 -VTH1 ≥ VDS1을 만족시킨다[9]. 따라서 M1이 ON 상태가 되면서 기존회로에서 흐르던 전류 IB에 M1이 발생시키는 전류 Iplus1이 전류 미러 M2, M3를 통해 nmos 입력단에 더해져 IB +Iplus1의 전류가 흐르게 되어 상승 슬루율을 향상시키게 된다. M4와 M5는 비반전 입력단의 pmos가 동작할 때 상승 슬루율을 증가시키기 위해 추가되었다. M4의 게이트는 출력단과 연결되어 출력전압에 따라 ON/OFF를 결정짓는 스위치 역할을 한다. M5는 다이오드 구조로 입력 pmos가 동작하고 M4가 ON이 되었을 때 추가 전류 Iplus2를 발생시켜 기존에 pmos 입력단으로 흐르던 전류 IB에 더해져 IB +Iplus2의 전류가 흐르게 되어 상승 슬루율을 향상시키게 된다. 추가된 전류 부스팅 구조의 동작시간은 그림 3에서 설명했던 상승구간 T1과 하강구간 T2만큼의 시간적 차이가 발생하는 동안만 동작하기 때문에 증가되는 소비전력이 아주 작다.

Ⅲ. 시뮬레이션 결과 및 검토

실험 조건은 표 1에 주어진 조건과 같다. 표 1은 본 논문에서 제안된 버퍼앰프에 인가되는 입력파형의 주파수, 전압, 공급전압, 부하 저항, 부하 커패시터의 파라메타값을 나타낸 것이다.

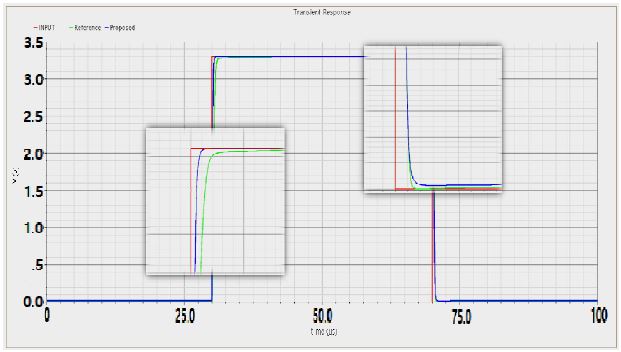

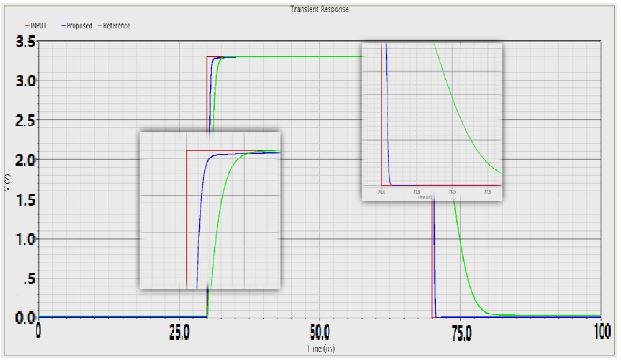

그림 5와 그림 6에 나타난 파형은 증폭기의 반전 입력에 부궤환을 걸고 입력단자에 위 표 1의 조건에 언급한 펄스 파를 인가한 경우의 시뮬레이션 결과 파형을 나타낸 것이다.

그림 5는 기존의 버퍼앰프와 제안한 버퍼앰프가 부하커패시터 10pF을 구동할 때 시뮬레이션 결과이다. 두 개의 버퍼앰프에 펄스 파형을 인가하여 입력전압 파형과 두 버퍼앰프의 시뮬레이션 출력전압파형을 비교하여 나타낸 것이다. 시뮬레이션 결과 기존의 버퍼앰프의 상승 슬루율은 12V/㎲이고, 하강 슬루율은 11V/㎲의 결과를 확인할 수 있다. 제안한 버퍼앰프는 시뮬레이션 결과 상승 슬루율은 39V/㎲이고, 하강 슬루율은 38V/㎲의 결과를 확인할 수 있다.

Transient response simulation result when the conventional buffer amplifier and the proposed buffer amplifier drive the load capacitor 10pF

그림 6은 기존의 버퍼앰프와 제안된 버퍼앰프가 부하커패시터 10nF을 구동할 때 시뮬레이션 결과이다. 두 개의 버퍼앰프에 펄스 파형을 인가하여 입력전압 파형과 두 버퍼앰프의 시뮬레이션 출력전압 파형을 나타낸 그래프이다. 시뮬레이션 결과 기존의 버퍼앰프의 상승 슬루율은 5V/㎲이고, 하강 슬루율은 4V/㎲의 결과를 확인할 수 있다. 제안한 버퍼앰프의 시뮬레이션 결과 상승 슬루율 23V/㎲이고, 하강 슬루율 21V/㎲의 결과를 확인할 수 있다.

Transient response simulation result when the conventional buffer amplifier and the proposed buffer amplifier drive the load capacitor 10nF

그림 5와 같이 부하 커패시터의 크기가 작은 경우는 기존회로가 가지고 있는 상승 및 하강 슬루율 특성만으로도 충분히 출력파형이 입력파형을 따라 갈 수 있으나, 그림 6의 경우 같이 부하 커패시터가 큰 경우에는 충/방전 슬루율이 감소하여 출력파형이 입력파형을 따라가지 못하는 것을 확인할 수 있다.

그림 5를 보면 기존의 버퍼앰프의 출력파형 그래프보다 제안된 버퍼앰프의 출력파형이 입력파형에 일치하는 모습을 확인할 수 있으며, 이는 제안된 회로가 10nF의 부하 커패시터가 접속되어도 충분히 구동할 수 있다는 것을 보여주고 있다.

표 2는 본 논문에서 제안된 버퍼앰프의 특성을 나타낸 표이다. 표 2에서 보면 제안한 회로에서는 Av, CMRR, PSRR, 슬루율, 소비전력이 모두 안정적인 특성을 갖고 있어 슬루율 및 소비전력만을 고려한 기존 회로보다 고성능 버퍼앰프로 사용이 가능하다는 것을 알 수 있다. 본 논문에서 제시한 Av, CMRR, PSRR의 특성이 기존 회로 대비 전압 이득이 약 30dB 향상된 것을 확인하였으며, CMRR과 PSRR의 특성은 100dB 이상인 것을 확인하였다. GB의 값 또한 비교한 회로들보다 향상한 것을 확인하였는데 이는 추가한 전류 부스팅 회로가 입/출력 사이에 연결되어 밀러효과를 보상하는 보상커패시터 역할을 하게 되어 향상한 것으로 생각된다. 또한 PM이 안정적이여서 버퍼로 사용하기에 적합하고, 저소비전력 특성을 가지고 있다. 특히, 부하커패시터 10nF 구동시 기존 버퍼앰프의 결과와 비교했을 때 기존 회로의 결과가 2V/㎲의 슬루율인 것에 비해 22V/㎲의 향상된 슬루율을 가진다는 것도 확인하였다. 입/출력 동작영역 범위도 VSS~VDD 까지로 입/출력이 풀 스윙하는 것도 확인하였다. 또한, 작은 입력 오프셋을 가지고 있어 전원 전압의 변화에도 안정적인 버퍼동작을 할 수 있다. 또한 추가되는 MOSFET 개수가 9개 밖에 되지 않아 면적 감소 효과도 기대해 볼 수 있다.

표 3에서는 다른 논문에서 제시한 방법과 본 논문이 제시한 방법의 슬루율 및 앰프 특성을 비교한 결과이다. 다른 논문에서 제시한 전류 부스팅 방식과 본 논문에서 제시한 방법을 비교하였을 때 슬루율을 포함하여 전체적인 앰프의 특성은 비슷하였다. 그러나 기존 전류 부스팅 방식은 전류 부스팅에 사용되는 MOSFET 개수가 42개이었으나 본 논문이 제시한 방법은 9개로 기존 방법보다 면적감소 효과가 두드러지게 클 것으로 예상된다. 또한 기존 전류 부스팅 회로의 경우 회로안의 En/Enb를 동작시키는 디지털 클럭이 필요한데 반해 본 논문이 제시한 방식은 입/출력 파형의 시간 차이로 동작하기 때문에 디지털 클락이 필요 없어 훨씬 실용적인 방법이라 할 수 있다.

Ⅳ. 결 론

본 논문에서는 기존의 사용되던 레일-투-레일 버퍼증폭기 회로보다 높은 슬루율 및 저소비전력을 갖는 전류 부스팅 방식의 버퍼증폭기를 설계하였다. 제안된 방식의 증폭기는 10pF ~ 10nF의 부하커패시터를 빠르게 구동하기 위해 입/출력단 사이에 입/출력 파형의 시간차이를 감지하여 동작하는 전류 부스팅 회로를 추가하여 설계하였다. 입/출력 파형의 시간 차이를 감지하여 충/방전 시간에만 추가된 회로가 동작하기 때문에 저소비전력 특성을 가진다. 제안한 버퍼증폭기는 TSMC 0.18um 공정을 사용하여 시뮬레이션 하였고 시뮬레이션 결과 부하 커패시터 10pF를 기준으로 하였을 때 상승 슬루율는 39V/㎲, 하강 슬루율 38V/㎲이고 이 값은 기존 레일-투-레일 버퍼증폭기의 슬루율 보다 약 3~4배 이상의 슬루율 향상이 확인되었다. 또한, 부하커패시터 10nF를 기준으로 하였을 때도 상승 슬루율은 23V/㎲, 하강 슬루율은 21V/㎲이며 이 역시 기존의 레일-투-레일 버퍼증폭기의 슬루율 보다 약 4배 이상의 슬루율을 가짐을 알 수 있었다. 또한 기존 전류 부스팅 방식과 비교했을 때 슬루율 특성을은 유사한 반면에 전류 부스팅에 사용된 MOSFET의 개수는 아주 작아 면적 감소를 예상할 수 있어 실용적인 방법임을 확인하였다. CMRR 및 PSRR등의 특성도 100dB 이상의 값을 가지며 따라서 작은 오프셋 및 전원 전압의 변화에 따른 잡음 처리 능력도 가지고 있음을 알 수 있었다.

Acknowledgments

이 논문은 2016년도 청주대학교 연구장학 지원과 IDEC에서 EDA Tool을 지원받아 수행한 것임.

References

-

D. Marano, G. Palumbo, and S. Pennisi, "A high-speed low-power output buffer amplifier for large-size LCD applications", 2009 16th IEEE International Conference on Electronics, Circuits and Systems, p132-135, Dec), (2009.

[https://doi.org/10.1109/icecs.2009.5410957]

-

D. Marano, G. Palumbo, and S. Pennisi, "A Novel Low-Power High-Speed Rail-to-Rail Class-B Buffer Amplifier for LCD Output Drivers", Proceedings of 2010 IEEE International Symposium on Circuits and Systems, p2816-2819, Jun), (2010.

[https://doi.org/10.1109/iscas.2010.5536982]

-

M. H. Zarifi, M. Yousefi, A. Rostami, Z. KuzeKanani, and J. Sobhi, "Very high-gain and fast-settling opamp for switched-capacitor applications", 2007 Internatonal Conference on Microelectronics, p385-388, Dec), (2007.

[https://doi.org/10.1109/icm.2007.4497735]

-

B. H. Kassiri, and M. Jamal Deen, "Slew-rate enhancement for a single-ended low-power twostage amplifier", Circuits and Systems (ISCAS), 2013 IEEE International Symposium on, p1829-1832, May), (2013.

[https://doi.org/10.1109/iscas.2013.6572221]

-

B. Panda, S. K. Dash, and S. N. Mishra, "High slew Rate op-amp design for low power applications", ICCICCT, p1096-1100, 10-11), Jul, (2014.

[https://doi.org/10.1109/iccicct.2014.6993124]

- M. Neag, and O. McCarthy, "High speed, low-power CMOS voltage buffers", Semiconductor Conference, 1, p175-180, Oct), (1998.

-

S. Qureshi, and P. Rawat, "A Rail-to-Rail Class AB Amplifier Design with an Offset Cancellation for LCD Source Drivers", 2016 IEEE Students’ Conference on Electrical, Electronics and Computer Science(SCEECS), p1-4, Mar), (2016.

[https://doi.org/10.1109/sceecs.2016.7509300]

-

R. Hogervorst, J. P. Tero, R. G. H. Eschauzier, and J. H. Huijsing, "A Compact Power-Efficient 3V CMOS Rail-to-Rail InputOutput Operational Amplifier for VLSI Cell Libraries", IEEE Journal of Solid-State Circuits, 29(12), p1505-1513, Dec), (1994.

[https://doi.org/10.1109/4.340424]

- B. Razavi, "Design of Analog CMOS integrated Circuits", Mc Graw Hill, (2011).

-

M. Lee, and S-H. Son, "Dual output Rail to Rail CMOS Buffer Amplifier with Low Power and High Slew Rate for LCD Source Driver IC", JKIIT, 12(10), p1-9, Oct), (2014.

[https://doi.org/10.14801/kitr.2014.12.10.1]

2009년 3월 : 청주대학교 반도체설계 공학과(공학사)

2016년 3월 ~ 현재 : 청주대학교 반도체설계 공학과 석사과정 (공학석사).

관심분야 : CMOS Analog IC 설계, Digital IC 설계, Display driver ic 설계

1983년 2월 : 한양대학교 전자공학과(공학사)

1985년 2월 : 한양대학교 전자공학과(석사)

1988년 8월 : 한양대학교 전자공학과(박사)

1988년 9월 ~ 1991년 2월 : 순천향대학교 전산학과 전임강사

1991년 3월 ~ 현재 : 청주대학교 반도체 설계공학과 교수

2009년 3월 ~ 2010년 2월 : Univ. of Texas at Dallas 방문교수

관심분야 : CMOS Analog IC 설계 및 센서 신호 처리 회로 설계