Journal of KIIT. Vol. 19, No. 2, pp. 47-52, Feb. 28, 2021, pISSN 1598-8619, eISSN 2093-7571 **47** http://dx.doi.org/10.14801/jkiit.2021.19.2.47

# AC PDP에서 효율 향상을 위한 음의 유지 전압을 가지는 수정된 구동방법

조병권\*

# Modified Driving Method with Negative Sustain Voltage to Improve Efficiency in AC PDP

Byung-Gwon Cho\*

이 논문은 부경대학교 자율창의학술연구비(2019)에 의하여 연구되었음

#### 요 약

AC PDP에서 효율을 향상시키기 위하여 유지 기간에 음의 전압이 인가되도록 수정된 구동방법이 제안되었다. 종래의 구동방법에서 유지 시간 동안에는 양의 전압 파형이 교대로 인가되었기 때문에 플라즈마 방전의 발생이 상판의 두 전극 사이에서 발생할 뿐만 아니라 상판의 한 전극과 하판의 기입전극 사이에서 불필요한 방전이 발생하였다. 전체적인 방전의 세기는 크기 때문에 휘도는 향상되지만, 불필요한 방전에 의해 전류의 상승을 유발하여 효율은 감소한다. 그러므로 본 연구에서는 유지 시간동안 상판과 하판의 전극사이의 방전을 방지하기 위하여 상판 전극에는 음의 전압을 인가하였고 전체적인 구동 파형도 수정되었다. 그 결과 효율은 전압에 따라 약 5~15 % 향상시킬 수 있었다.

#### Abstract

In order to improve efficiency in AC PDP, a modified driving method has been proposed so that a negative voltage is applied during the sustain period. In the conventional driving method, since positive voltage waveforms are alternately applied during the sustain period, plasma discharge occurs not only between the two electrodes on the upper plate, but also unnecessary discharge between one electrode on the upper plate and the write electrode on the lower plate. Since the intensity of the overall discharge is large, the luminance is improved, but the efficiency decreases by causing an increase in current due to unnecessary discharge. Therefore, in this study, a negative voltage was applied to the upper electrode and the overall driving waveform was modified to prevent discharge between the upper and lower electrodes during the holding time. As a result, the efficiency could be improved by about 4~15%.

#### Keywords

negative sustain, efficiency, driving method, sustain period, AC PDP

<sup>\*</sup> 부경대학교 융합디스플레이공학과 교수

<sup>-</sup> ORCID: htp:/orcid.org/0-002-0563-3494

<sup>·</sup> Received: Jan. 16, 2021, Revised: Feb. 15, 2021, Accepted: Feb. 18, 2021

<sup>·</sup> Corresponding Author: Byung-Gwon Cho

Dept. of Display Engineering, Pukyong National University, Korea. Tel.: +82-51-629-6417, Email: bgcho@pknu.ac.kr

# 1. 서 론

AC PDP는 현재 디스플레이 제조사의 사정에 의 해 더 이상 제품을 만들고 있지 않으나 대화면 구 현에 유리하고, 빠른 응답속도, 자연스러운 색상 등 의 많은 장점을 가진 소자이다[1][2]. 제조사가 제품 을 더 이상 개발하고 만들지 않은 여러 가지 이유 중에서 낮은 효율는 큰 문제점이었다[3]. 이전의 연 구는 효율을 상승시키기 위하여 재료를 개선하거나, 방전 가스를 최적화하거나, 패널 구조를 변화시키는 등의 재료 및 구조 개선 위주로 진행되어 왔다 [4][5]. 한편, AC PDP의 구동 방법의 변화에 의해 효율을 향상시키기 위한 방법으로는 새로운 에너지 회수 회로를 구현하고, 유지 기간에 또 다른 펄스를 인가하여 방전의 효율을 높이는 방법이 제시되었다 [6][7]. 그러나 새로운 에너지 회수 회로와 다른 펄 스를 만드는 방법은 구동회로의 복잡화와 부품수의 상승을 유발하였다. 그러므로 새롭게 연구되는 AC PDP의 구동방법에서 종래의 구동파형에서 큰 변화 없이 플라즈마 방전의 모드만 바꾸어서 불필요한 방전의 발생을 방지하는 것이 효율의 향상에 기여 할 것이다.

하나의 TV 프레임 시간 내에서 AC PDP의 구동 방법은 유지 기간의 펄스가 다른 다수의 부-프레임 의 선택적 조합으로 패널의 밝기를 구현한다. 하나 의 부-프레임은 초기화, 기입, 유지 기간으로 다시 나누어진다. 초기화 기간은 이전 부-프레임 시간에 서 셀마다 다르게 만들고 지워진 벽전하들을 제거 하고 모든 셀들을 똑같은 벽전하 상태로 만들어준 다. 벽전하란 AC PDP의 셀 내부에서 플라즈마 방 전에 의해 분리된 양전하와 음전하가 벽에 붙어 있 는 상태를 의미한다. AC PDP에서는 셀 내부에서 형성된 벽전하를 이용하여 비교적 낮은 전압으로 구동한다. 초기화 기간에서의 구동 파형은 모든 셀 내부의 벽전하를 다음 단계를 위해서 셀 내부에 적 절히 배열시키는 역할을 한다. 그러므로 초기화 기 간에서는 벽전하가 소거될 수 있는 강한 방전보다 는 약한 방전을 발생시키는 경사 파형을 주로 사용 한다. 그 다음의 기입 기간에는 상판의 가로와 하판 의 세로 방향의 전극 사이에서 시간에 따른 순차적 으로 선택된 셀에서만 방전을 발생시키는 기능을 수행한다. 부-프레임의 마지막 단계인 유지 기간에서는 상판에 있는 두 개의 전극에 각각 교대로 사각 파형이 인가되어 기입 기간에서 선택된 셀에서만 방전을 발생시킨다. 유지 기간에서는 사각 파형이 인가되기 때문에 강한 방전이 발생하므로 방전의 수가 밝기에 비례한다. 각각의 부-프레임에서는서로 사각 펄스의 개수를 다르게 인가하고 부-프레임의 조합에 의해 원하는 밝기를 표현한다.

유지 기간에서는 상판의 두 전극에서는 양의 사 각 파형이 교대로 인가되고, 하판의 기입 전극은 접 지 상태로 유지된다. 즉, 상판에 있는 하나의 전극 에 양의 전압이 인가되면 나머지 두 전극은 접지 상태가 된다. 그러므로 하나의 양의 전압은 세 전극 사이의 전압차에 의해 다른 상판 전극간의 방전과 하판과의 방전을 동시에 발생시킨다. 상판 사이에서 의 방전은 넓은 영역에서 고르게 방전이 발생하는 반면에, 상판과 하판 사이에서 발생하는 방전은 수 직적으로 발생하므로 방전이 발생한 부분에서만 빛 이 강하게 발생하고 방전이 전극에 의해 가려지기 때문에 전력만 소모하는 불필요한 방전이다. 본 연 구에서는 상판과 하판사이에서 방전이 발생하지 않 도록 음의 사각 전압을 인가하는 구동 방법을 구현 하였고 효율을 측정하여 양의 전압을 인가하였을 때와 비교하였다.

# Ⅱ. 실험 구성

그림 1에서는 AC PDP에서 세 전극을 갖는 하나의 셀의 단면도를 나타낸다. 상판에서는 유지(X) 및 주사(Y) 전극이 수평으로 나열되어 있고 하판에는 기입(W) 전극이 상판의 전극과 수직방향으로 배치되어 있다.

그림 1. AC PDP에서 세 전극을 갖는 한 셀의 단면도 Fig. 1. Cross-sectional diagram of one cell in AC PDP with three electrodes

하판에서 전극들 사이에 있는 격벽은 이 그림에서 생략되었다. 유지 기간에서는 사각 파형에 의한 플라즈마 방전이 강하기 때문에 상판의 전극이 손상될 수 있다. 유전체 층은 그림과 같이 전극이 직접 노출되지 않도록 보호하고 있다. 플라즈마 방전에 의해 발생된 진공 적외선이 하판에 도포되어 있는 형광체를 여기시켜 빛이 발생시키고 다시 유전체를 통과한 빛이 외부로 나타나게 된다.

표 1에서는 실험에 사용된 패널의 사양을 보이고 있다. 상판에서는 버스전극의 폭, ITO 전극의 폭, 두 ITO전극 사이의 간격이 기록되어있다. 상판에서의 버스 전극은 유지 및 주사 전극을 나타내고, ITO는 버스 전극위에 있는 투명 전극이다. 하판에는 기입 전극의 폭, 격벽의 높이, 격벽의 폭이 나타내었다. 하판에서 격벽은 각 셀마다 나누어지는 경계를 의미한다. 패널 내부에서는 Ne(93%)-Xe(7%)의함량을 갖는 혼합 가스가 사용되었다.

표 1. 본 연구에 사용된 패널의 사양 Table 1. Specification of panel in this study

| Front plate (µm)           |     | Rear plate (µm)       |     |  |

|----------------------------|-----|-----------------------|-----|--|

| Bus electrode width        | 110 | Write electrode width | 150 |  |

| ITO width                  | 360 | Barrier rib height    | 120 |  |

| ITO gap                    | 85  | Barrier rib width     | 60  |  |

| Ne(93%)-Xe(7%) gas mixture |     |                       |     |  |

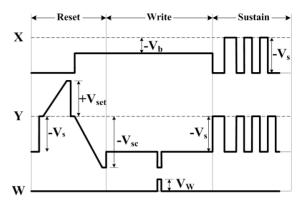

그림 2는 하나의 부-프레임 시간 동안 그림 1에 서 보여진 세 개의 전극에 각각 인가된 구동 파형 이다. 표 2는 그림 2에서 표시된 전압 기호의 명칭 과 실험에 사용된 전압 레벨을 나타낸다. X와 Y 구 동 파형은 상판에 인가되고 W 구동 파형은 하판에 각각 인가된다. 하나의 부-프레임 에서는 초기화 (Reset), 기입(Write), 유지(Sustain) 기간으로 나누어 진다. 종래의 구동파형과 다른 점은 X와 Y 전극에 음의 유지전압을 인가하기 위해서 전압이 - Vs 만 큼 낮아졌다. W 전극에서의 전압은 종래와 동일하 다. 초기화 기간에서는 경사파를 사용하여 약한 방 전을 발생시켜서 이전 셀에 쌓였던 벽전하들을 소 멸해주는 역할을 한다. 앞선 부-프레임 시간에서의 벽전하가 주로 발생하였기 때문에 X와 Y 전극 사 이에서 높은 전압차에 의해 벽전하를 원활히 소거 시킬 수 있기 때문이다.

그림 2. 하나의 부-프레임 시간 동안에 AC PDP의 세 전극에 인가되는 구동파형

Fig. 2. Driving waveform applied to three electrodes of AC PDP during one sub-frame time

표 2. 기호의 명칭과 전압 레벨 Table 2. Name and voltage level of symbols

| Symbol           | Name            | Voltage level [V] |  |

|------------------|-----------------|-------------------|--|

| $V_{set}$        | Reset voltage   | 180               |  |

| -V <sub>s</sub>  | Sustain voltage | -180              |  |

| -V <sub>b</sub>  | Bias voltage    | -20               |  |

| -V <sub>sc</sub> | Scan voltage    | -230              |  |

| V <sub>w</sub>   | Write voltage   | 60                |  |

기입 기간에서는 Y 전극에 주사 펄스가 시간에 따라 순차적으로 인가되고 A 전극에서는 해당되는 셀에서 선택적으로 펄스가 인가될 때, 기입 방전이 발생하고 벽전하가 전극에 쌓인다. 즉, 기입 방전이 발생하지 않은 셀에서는 유지 기간에서도 방전이 발생하지 않지만, 기입 방전이 발생하면 셀 내부의 벽전하의 배치가 달라지기 때문에 유지 기간에서는 X와 Y 전극에 교대로 음의 사각 펄스가 인가되기 때문에 기입 기간 중에 선택된 셀에서만 형성된 벽전하에 의해 방전이 발생하여 빛이 나타날 수 있다.

## Ⅲ. 유지 파형과 벽전하 비교

그림 3(a)는 AC PDP의 구동파형에서 종래에 양의 전압이 인가되었을 때 유지 기간을 확대한 구동파형과 그의 광 파형을 나타내고, 그림 3(b)는 한쌍의 펄스 시간 동안 시간의 변화에 따른 셀 내부에서 방전의 발생 현상과 벽전화의 분포의 그림이다. 기존에 컴퓨터에 의한 플라즈마 방전 시뮬레이

선 프로그램이 개발되었고 활용되고 있지만, 여전히실제 방전현상에서 세세한 변화는 반영하지 못하기때문에 이론적인 벽전하 모델링으로 대신하였다[8]. AC PDP의 유지 기간에서는 X와 Y 전극에 사각 파형이 교대로 인가되기 때문에, 그림 3(a)와 (b)에서(i) 시간은 이전 유지 방전이 끝난 시간으로서 X 전극에는 음의 벽전하가 쌓이고 Y와W 전극에는 양의벽전하가 쌓여 있다고 가정한다. (ii) 단계에서 Y전극에 양의 전압이 인가될 때, 이전에 쌓였던 벽전하들을 이용하여 방전이 발생한다. 이때 W 전극에 쌓여있는 양전하들도 같이 방전에 이용된다.

왜냐하면 Y 전극에 양의 전압이 인가되면 Y와 W 전극 사이에 방전이 발생할 만큼의 전위차가 되기 때문이다. Y와 W 사이의 방전은 전체 방전의세기에는 도움을 주지만, 불필요한 전류를 더 많이흐르게 하므로 효율은 좋지 않을 것이다. Y 전극에양의 펄스가 인가되고 방전이 발생한 이후에 셀 내부에는 (iii) 단계처럼 Y 전극에는 음의 벽전하가 쌓이고 X와 W 전극에는 양의 벽전하가 쌓이게 된다.다시 (iv) 단계와 같이 X 전극에 양의 전압이 인가되면 이전에 쌓인 벽전하들을 이용하여 방전이 발생한다.

그림 3. 유지 기간에서 X와 Y 전극에 양의 전압이 인가 되었을 때의 구동 파형과 광 파형(a), 셀 내부에서 시간의 변화에 따른 방전의 발생과 벽전하 변화의 모식도 Fig. 3. Driving waveform and light waveform when positive voltages are applied to the X and Y electrodes in the sustain period (a), and a schematic diagram of the occurrence of discharge and wall charge changes according to time changes inside the cell

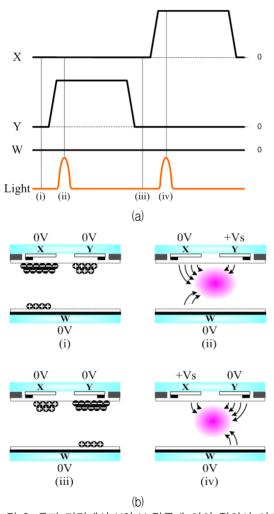

그림 4. 유지 기간에서 X와 Y 전극에 양의 전압이 인가 되었을 때의 구동 파형과 광 파형(a), 셀 내부에서 시간의 변화에 따른 방전의 발생과 벽전하 변화의 모식도 Fig. 4. Driving waveform and light waveform when negative voltages are applied to the X and Y electrodes in the sustain period (a), and a schematic diagram of the occurrence of discharge and wall charge changes according to time changes inside the cell

그림 4(a)는 AC PDP의 수정된 구동파형에서 유지 기간에 음의 전압이 인가되었을 때 유지 기간을 확대한 구동 파형과 그의 광 파형을 나타내고, 그림 4(b)는 한 쌍의 펄스 시간 동안 시간의 변화에 따른셀 내부에서 방전의 발생 현상과 벽전화의 분포의그림이다. (i) 시간이전에는 Y 전극에 음의 전압이인가되어서 방전이 발생했기 때문에 X와 W 전극에는 음의 벽전하가 쌓이고 Y 전극에는 양의 벽전하가 쌓여 있을 것이다. (ii) 단계에서 X전극에 음의전압이인가되기 때문에, X와 Y 전극사이에서 방전이 발생하고 X와 W 전극 사이에서는 방전이 발생하지 않는다.

왜냐하면 X와 W 전극에는 같은 극성의 벽전하가 쌓여 있기 때문이고 외부 인가전압과 벽전하의합이 방전이 발생할 만큼의 전압차가 되지 않기 때문이다. 그러므로 W 전극의 음의 전하는 유지 방전에 도움을 주지 않기 때문에 계속 그대로 있을 것이고 종래와 비교해서 밝기도 약할 수밖에 없다. 그러나 대향형 방전에 의한 불필요한 전류를 줄일 수있기 때문에 효율은 상승할 것이다.

X 전극에 음의 펄스가 인가되고 방전이 발생한 이후에 셀 내부에는 (iii) 단계처럼 X 전극에는 양의 벽전하가 쌓이고 Y와 W 전극에는 음의 벽전하가 쌓이게 된다. 다시 (iv) 단계와 같이 Y 전극에 음의 전압이 인가되면 X와 Y 전극에 쌓인 벽전하만을 이용하여 방전이 발생한다.

#### IV. 실험 결과

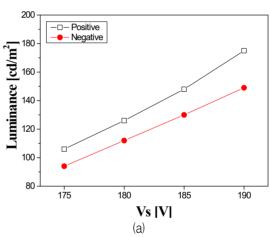

유지 기간에서 양과 음의 전압을 인가하였을 때전압에 높이에 따른 휘도와 효율의 변화가 그림 5에 나타나있다. 가로축의 Vs는 유지 전압의 크기를 의미하며 절대값을 의미한다. 그림 5(a)에서 양의유지 전압을 인가할 때 음의 전압을 인가할 때보다전체적으로 휘도가 더 높다. 앞서 언급하였듯이 W전극과의 방전도 동시에 발생하기 때문이다. 유지전압의 크기가 높아질수록 양과 음의 유지전압을 인가할 때 휘도는 둘 다 당연히 높아진다. 그러나양의 전압을 인가할 때 하판의 W 전극과의 방전도 같이 세지기 때문에 음의 전압과 비교해서 높은 전

압에서 더 많이 올라가서 휘도의 격차가 더 벌어 진다.

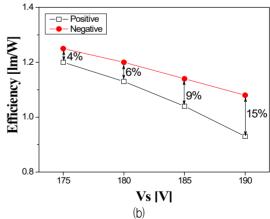

반면에 그림 5(b)에서와 같이 효율은 양의 유지 전압을 인가할 때보다 음의 전압을 인가할 때가 전 체적으로 더 높다. 왜냐하면 불필요한 W 전극과의 방전이 줄어들어서 전류가 감소했기 때문이다. 양과 음의 전압을 인가하는 유지 전압의 크기가 높아질 수록 효율은 둘 다 낮아진다. 유지 전압이 높을수록 효율이 감소하는 것은 일반적인 AC PDP의 현상이 다. 그러나 음의 전압을 인가할 때는 하판의 W 전 극과의 방전이 없기 때문에 효율 하강은 양의 전압 을 인가할 때보다 덜 내려가므로 높은 전압에서는 효율의 차이가 더 크다. 그 결과, 유지 전압의 크기 따라서 음의 전압을 인가할 때의 효율은 양의 전압 을 인가할 때보다 약 4~15% 정도 상승하였다.

그림 5. 유지 기간에서 양과 음의 전압 높이에 따른 휘도 (a)와 효율 (b)의 변화

Fig. 5. Changes in luminance (a) and efficiency (b) according to the height of positive and negative voltages in the sustain period

두 그림을 비교할 때, 전압을 올릴수록 두 가지 경우에 있어서 휘도는 동시에 상승하지만, 음의 전압이 인가될 경우에는 대향형 방전이 없으므로 양의 전압의 경우보다 휘도는 낮다. 이 휘도는 앞서언급하였던 유지 펄스의 개수를 조절하면 되기 원하는 휘도를 표시할 수 있기 때문에 휘도의 상승은 큰 의미가 없다. 그러나 통상적으로 그림 5(b)와 같이 전압이 높아지면 효율은 낮아지는데, 음의 전압이 인가될 때는 방전이 줄어들었기 때문에 효율은 양의 전압의 경우보다 높다.

### V. 결 론

교류형 플라즈마 디스플레이에서의 유지 기간 동안에 음의 전압을 인가하기 위하여 전체적인 구동방법을 수정하였다. 종래의 구동 방법에서는 유지기간에 양의 전압이 인가되었기 때문에 상판뿐만아니라 하판의 벽전하도 같이 사용하여서 방전이발생했기 때문에 불필요한 전류가 생성되었다. 그러나 음의 전압을 인가하였을 때는 상판의 전극 사이에서만 방전이발생하였고 하판의 전극과는 방전이발생하지 않았기 때문에 휘도는 양의 전압보다 낮아졌으나 효율은 향상되었다. 특히 전압이 높아질수록 효율의 차이는 더 커지게 되었고, 효율은 전압에따라 4~15% 향상되었다.

#### References

- [1] L. F. Weber, "Status and Trends of Plasma Display Device Research", Proc. of EuroDisplay, Berlin Germany, pp. 1-6, Sep. 1999.

- [2] H. Tolner, "The Bright Future of PDP Technology", Proc. of IMID, Daegu, Korea, pp. 277-314, Aug. 2004.

- [3] M. Uchidoi, "Fourth-generation PDPs: High image quality and low power consumption", Society for Information Display, Vol. 35, No. 1, pp. 202-205, May 2004.

- [4] G. Oversluizen, M. Klein, S. de Zwart, S. van Heusden, and T. Dekker, "Improvement of the

- discharge efficiency in plasma displays", J. Appl. Phys., Vol. 91, No. 4, pp. 2403-2408, Apr. 2002.

- [5] S. S. Park and B. G. Cho, "Improvement of Luminous Eficiency in AC Plasma Display Panel with Long Distance betwen Top Plate Electrodes", Journal of KIIT, Vol. 15, No. 2, pp. 41-46, Feb. 2017.

- [6] J. H. Yang, J. K. Kim, and K. W. Whang, An energy recovery circuit for AC plasma display panel with series CLC resonance-SER1", IEEE Trans. Consumer Electronics, Vol. 51, No. 2, pp. 718-724, May 2005.

- [7] C. S. Park, H. S. Tae, E. Y. Jung, and J. C. Ahn, "Effects of self-erasing discharge on panel-aging characteristics in AC plasma display panel", Thin Solid Films, Vol. 518, No. 22, pp. 6153-6159, May 2010.

- [8] S. B. Song and N. S. Yoon, "Three-dimensional heating model of inductively coupled plasma with rectangular geometry", Surface and Coatings Technology, Vol. 171, No. 1-3. pp. 183-186, Jul. 2003.

# 저자소개

조 병 권 (Byung-Gwon Cho)

2001년 2월 : 경북대학교 전자전기공학부(공학사) 2003년 2월 : 경북대학교 전자공학과(공학석사) 2006년 8월 : 경북대학교 전자공학과(공학박사) 2008년 3월 ~ 현재 : 부경대학교

융합디스플레이공학과 교수 관심분야: 디스플레이 시스템, 고전압 회로, 영상정보시스템