위상 배열 안테나 빔 오차 개선을 위한 반도체송수신모듈 크기/위상 보정 알고리즘 설계

초록

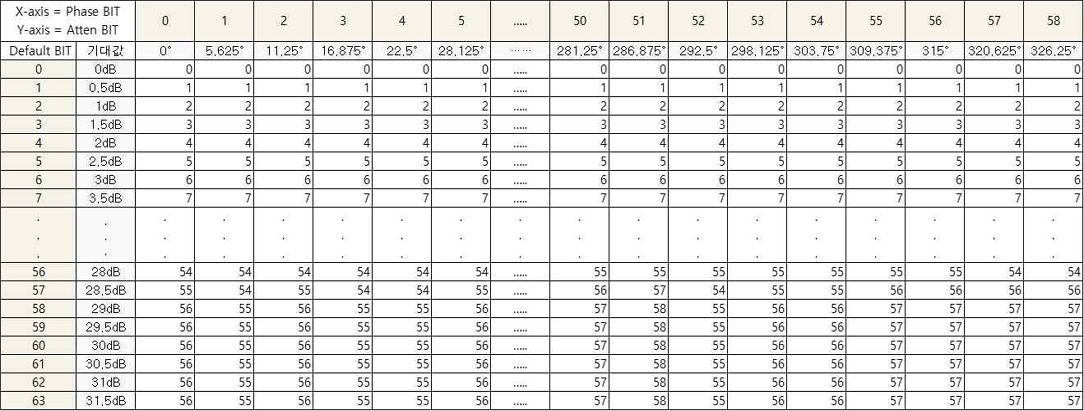

다기능 레이더용 반도체송수신모듈은 안테나의 송신 신호 증폭, 저 잡음 수신신호 증폭, 위상 천이, 크기 감쇄 기능 등 많은 기능을 가지고 있다. 본 논문에서는 해당 기능 중 위상 천이와 크기감쇄 오차를 보정하는 연구를 진행하였다. 위상/크기 가변을 위한 사용된 반도체송수신모듈의 다기능 칩(Multi function chip)은 디지털 위상 천이 단위는 5.625°, 크기 가변 단위는 0.5dB를 가지고 있으며, 최대범위는 크기는 31.5dB, 위상은 360°까지 가변이 가능하다. 하지만 칩이 가지고 있는 하드웨어적 오차 및 기생성분으로 인해 정확히 1LSB 만큼 가면되지 않는다. 이를 보정 알고리즘을 통해 1LSB에 가장 가깝게 움직일 수 있다. 본 논문에서는 보정 알고리즘에 대해 논할 예정이다. 보정 전 크기/위상에 대한 오차는 3dB/16°이고 알고리즘을 통한 보정된 크기/위상에 대한 오차는 0.8dB/4° 이내로 측정되었다.

Abstract

In multi function radar systems, Transmit/receive module provides amplifying transmit rf signal and receive low noise rf signal, phase shifting, amplitude attenuation, etc. In this paper, among the functions amplitude/phase correction algorithm is described with the process of generating control data to correct amplitude/phase for antenna unit. A MFC(Multi Function Chip) used for phase shifting and amplitude attenuation has 0.5dB(1lsb) attenuation resolution, 5.625°(1lsb) phase shifting resolution. Also, attenuation can be controlled to 31.5dB and phase shifting can be controlled to 360°. But the mfc doesn’t have an accurate 1lsb characterization because of parasitic effect. In this paper correction algorithm will be discussed. With the correction algorithm, It can be corrected to 1lsb. Before the correction algorithm, the mfc error had 3dB/16°. After the correction, An error was measured less than 0.8dB/4°.

Keywords:

mfc, phase, amplitude, correction algorithmⅠ. 서 론

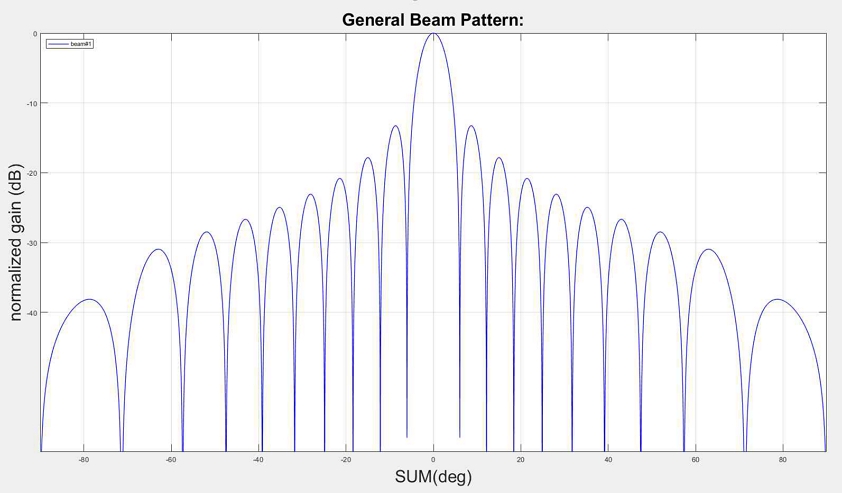

오늘날 방위 산업의 기술이 발전함에 따라 AESA(Active Electronically Scanned Array) 레이더 기술이 각광받고 있다. 레이더는 전파를 사용하여 목표물의 거리, 방향, 속도 및 각도를 측정하는 감지 시스템이다. 강한 전자기파를 발사하여 그것이 물체에 맞고 반사되어 되돌아오는 전자파를 분석하여 대상물과의 거리를 측정한다. 이 레이더는 과거 송수신 소자가 1개씩 있고, 기계적 움직임으로 조향을 하는 기계식 레이더에서 출발하여 송수신 소자 1개에 전자적 빔 조향을 하는 PESA(Passive Electronically Scanned Array), 이후 송수신부(T/R)가 여러 개 있는 성능이 우수한 AESA 레이더가 있다. AESA 레이더는 수백~수천 개의 송수신 채널로 이루어져 RF신호를 방사하고 물체를 맞고 되돌아오는 신호를 저잡음 증폭한다. RF신호를 방사하고 수신하는 빔 조향시, 수백~수천 개의 채널에서 나오는 RF신호에 대해 크기/위상을 합성하여 그림 1과 같이 안테나 빔 패턴을 형성한다[1].

그림 1은 500채널의 원형 모양의 위상배열 안테나의 Taylor weighting이 없는 상태의 일반적인 빈 패턴이다. 빔 형성 시, 주엽과 부엽으로 나뉘게 되는데 반도체송수신모듈의 채널 별 크기 가변 기능으로 주엽과 부엽의 차이를 만들게 되고 반도체송수신모듈의 채널 별 위상 천이 기능으로 주엽의 빔 방향을 결정하게 반도체송수신모듈내의 다기능 칩(MFC)을 이용해 제어한다[2][3]. 이때 이상적이지 않은 안테나의 측정된 주엽과 부엽의 차이 및 빔 방향은 차이가 발생 할 수 있다. 이는 다기능 칩과 반도체송수신모듈이 가지고 있는 비선형성에 의한 결과이다. 이는 AESA 레이더의 성능을 저하시키는 원인이 된다. 이를 개선하기 위해서는 PCB(Printed Circuit Board) 설계 단계에서부터 기생 성분 최소화 및 RF 신호 손실을 줄이며 개선 할 수 있다. 하지만 하드웨어적 오차는 존재하게 되며 이는 시스템 단계에서 보정이 필요한 이유이다. 반도체 MMIC(Monolithic Microwave IC)는 온도에 따라 특성이 변화하는 특징이 있다. 증폭기는 대표적인 비선형소자이다. 온도가 올라감에 따라 증폭 이득이 줄어들고 온도가 내려가면 증폭이득이 증가한다. 따라서 온도에 따른 증폭 이득 변화를 안테나 설계 단계 시 충분히 마진이 확보되어야한다. 추가로 다기능 칩은 Cross coupling 오차를 가지고 있으며, 이는 위상 가변 시 크기 값이 변화하고 크기 가변 시 위상 값이 변하는 오차이다.

본 논문에서는 Cross coupling 오차를 개선하고자 하였다. 반도체송수신모듈 단위로 제작하여 테스트하였고, 다기능 칩에 원하는 크기/위상 값을 공급하기 위해 FPGA(Field Programmable Gate Array)를 사용하였고 비휘발성 메모리를 이용해 계산한 보정 값을 저장하고 사용하는 방식을 이용하였다[4].

Ⅱ. 관련 연구

2.1 반도체송수신모듈 크기/위상 오차 측정

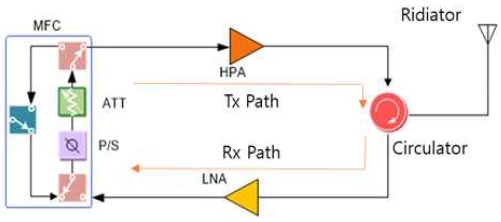

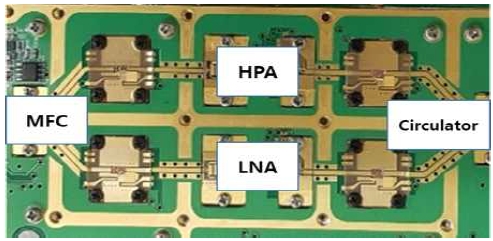

반도체송수신모듈의 송수신 경로에 대한 크기/위상 오차를 측정하기 위해 그림 2와 같이 회로를 구성하였다. 송신 경로의 크기/위상을 제어하기 위해 HPA(High Power Amplifier) 전단에 배치하였고, 수신 경로의 크기/위상을 제어하기 위해 LNA 후단에 배치하여 측정하였다. 송신경로에서도 HPA 후단에 다기능 칩을 배치하는 것이 선형성 측면에서 우수하다. 하지만 본 논문에 사용된 다기능 칩은 입력 RF 신호 버짓을 고려하여 전단에 배치하였다. 송신경로와 수신경로를 구분시키기 위해 안테나 방향에 순환기를 배치하였고 다기능 칩 자체 격리도를 활용하여 분리하였다.

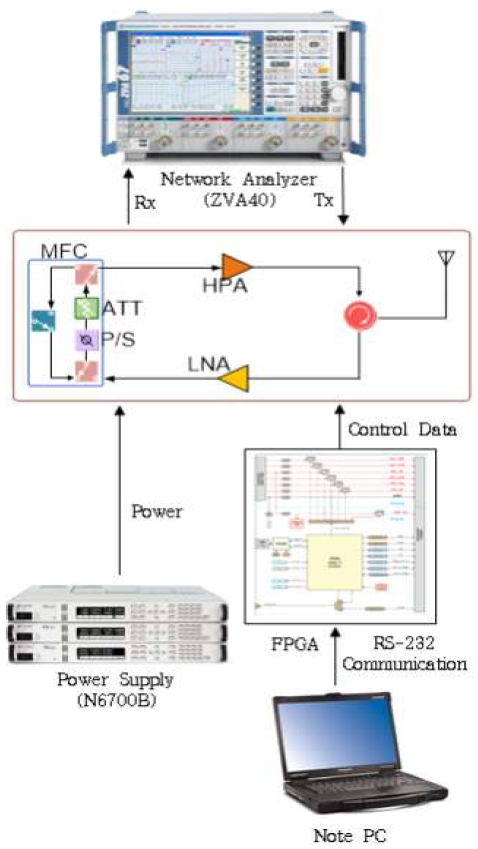

반도체송수신모듈 크기/위상 측정을 위해 그림 3과 같이 구성하였다. 반도체송수신모듈의 전원 전압으로 전원공급기(N6700B)를 이용하여 공급하였고, 증폭기 및 다기능 칩을 동작시키기 위해 FPGA를 활용해 제어보드를 제작하였고 Note PC와 RS-232통신으로 증폭기를 동작시키며 다기능 칩도 동작시켰다[5]. 동작된 반도체송수신모듈은 신호분석기를 통해 S-parameter를 측정하고 위상을 측정하였다. 본 논문에 사용된 다기능 칩의 크기/위상별 1LSB(Least Significant Bit)는 크기가 0.5dB, 위상이 5.625° 이다.

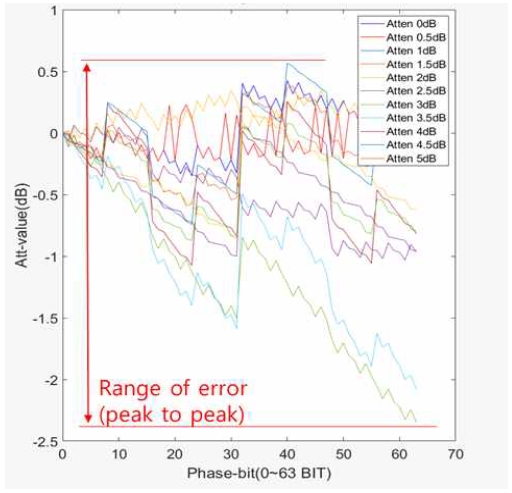

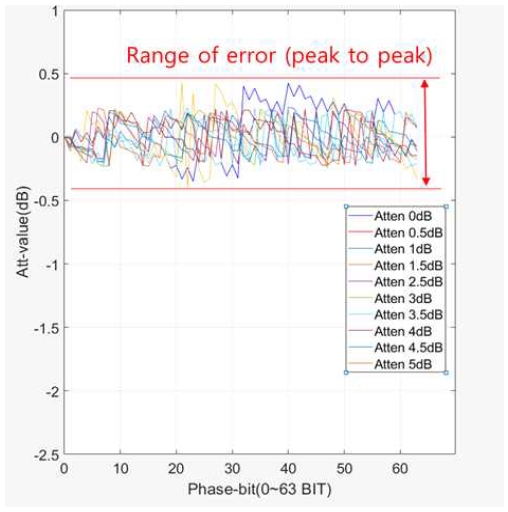

그림 4는 신호분석기에서 측정하여 추출한 데이터는 MATLAB에서 분석한 결과이다. 데이터에서 볼 수 있듯이 크기별 위상 비트를 변화 시켰을 때 나타나는 최대 크기 오차 량은 Peak to Peak가 약 3dB로 측정되었다.

Cross Coupling 효과와 송/수신 경로 상에 존재하는 비선형 소자로 인해 크기를 0dB로 고정 시킨 후, 위상을 0°~360° 변화 시켰을 때와 크기를 0.5dB로 고정 시켰을 때 위상을 0°~360° 변화 시켰을 경우 다른 오차를 가진다. 이상적으로는 위상비트를 변화하더라도 크기 오차는 0dB로 고정되어있어야 하지만 Cross Coupling 효과로 인해 크기 항목에서 오차가 발생하였다.

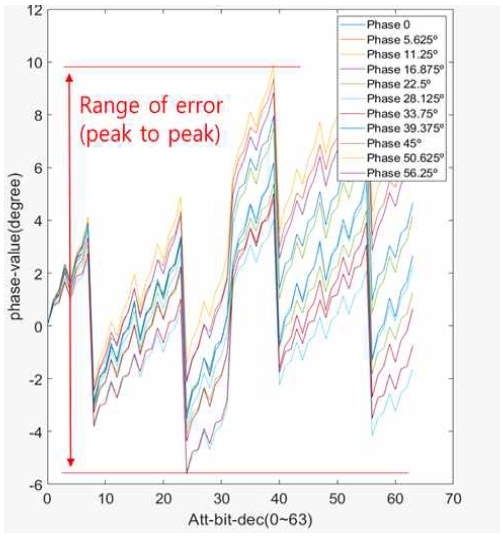

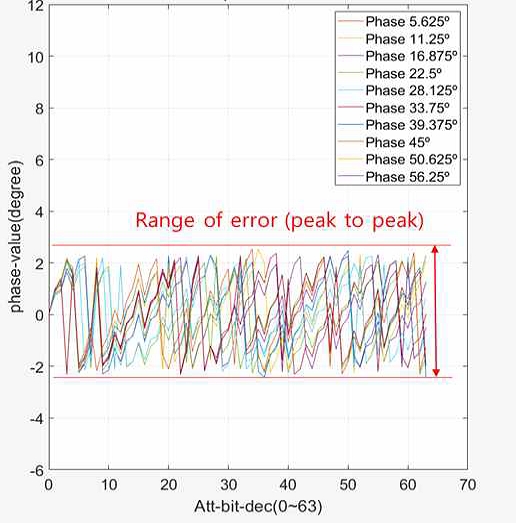

마찬가지로 그림 5는 위상별 크기 비트 변화 시 위상의 오차이다. Peak to Peak 14°로 측정 되었다. 크기 오차는 위상 값을 많이 천이 시켜 놓을수록 오차가 큰 경향을 보였고 위상 오차는 100°~200°사이에서 큰 오차를 보였다.

반도체송수신 모듈에 쓰인 다기능 칩의 감쇄는 0dB~31.5dB, 위상은 0°~360°이기 떄문에 그래프에 1LSB 개수만큼 총 64개의 막대기가 나와야 하지만 본 논문에서는 대표비트를 표현하였다. 이러게 오차를 발생시키는 원인은 반도체송수신모듈이 사용된 비선형성 소자들 때문이며 오차 발생원은 표 1에 정리 하였다.

2.2 크기/위상 보정 알고리즘 구현

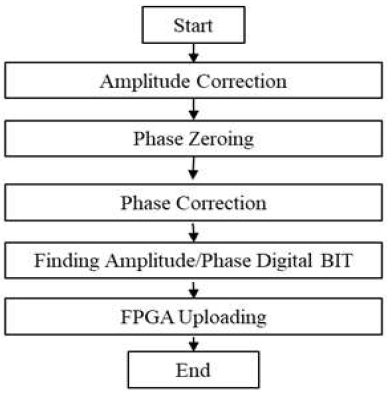

그림 6은 전체 보정 순서도이다. 크기 보정을 먼저 완료하고 난 후, 위상 정렬을 위한 Zeroing 다음 위상 보정을 하고나서 크기/위상 보정에 대한 디지털 비트를 찾는 순서이다.

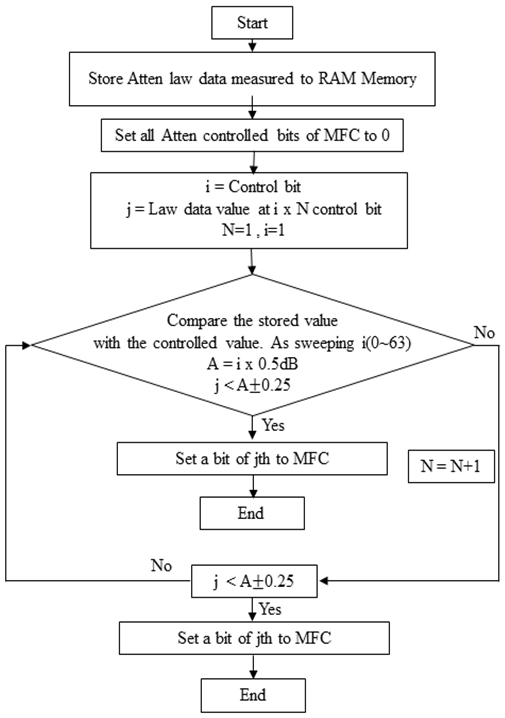

그림 7은 크기/위상 중 크기 보정을 위한 알고리즘이다. Cross Coupling 현상으로 인해 크기에 대한 보정 값을 우선적으로 찾고, 이후 위상에 대한 보정 값을 찾을 때 크기 값의 오차가 ±0.25dB 이상으로 커지지 않는 선에서 위상 보정 값을 찾아야 한다. 해당 값을 찾기 위해 본 논문에서는 크기에 대한 보정 값을 먼저 계산을 하고 이후 크기 보정 값을 반영하여 위상에 대한 알맞은 보정 값을 찾는다. 알고리즘의 차이 값을 ±0.25dB로 설정한 근거는 1LSB에 해당하는 값이 0.5dB이고 예를 들어 목표 감쇄 값이 2.5dB이면 이전 값이 3dB이고 다음 값은 2dB가 된다. 실측값이 2.75dB~2.25dB 일 때 2.5dB에 해당하는 보정 값으로 설정하기에 ±0.25dB로 설정하였다.

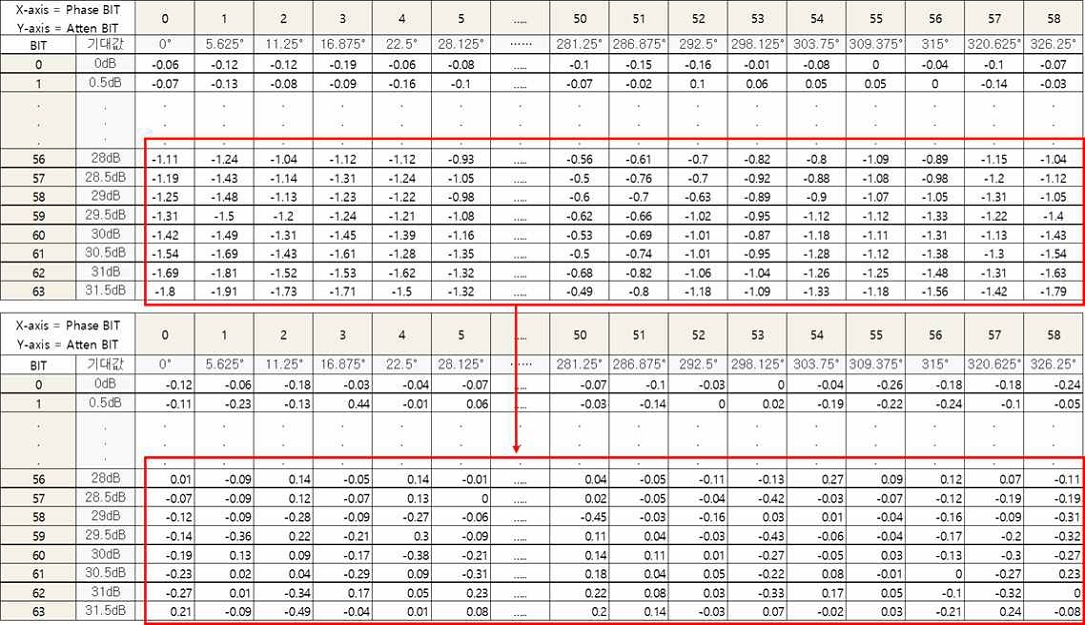

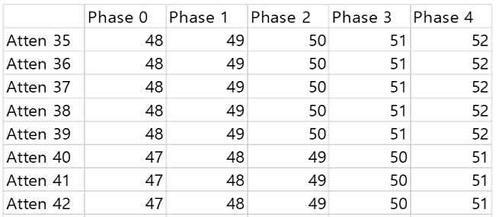

실측값이 2.9dB이면 여기에 해당하는 보정 값은 목표 값이 3dB에 해당하는 보정 값이다. 그림 8에 표현되어있듯이 크기 64bit, 위상 64bit에 해당하는 64×64 행렬을 만들고 이에 해당하는 크기 값을 FPGA 비휘발성 메모리에 저장을 한다. 예를 들어 GUI를 통해 위상 값 2(11.25°)와 감쇄 값 8(4dB)을 입력하게 되면 비휘발성 메모리에 있는 기본 데이터 64×64 행렬을 불러오고 위상 값 11.25°에 해당하는 행을 찾고 이때 감쇄 값을 0~31.5dB까지 1LSB 단위로 차례대로 비교를 하며 그 차이가 ±0.25dB 이하가 되면 그때 해당하는 감쇄 비트 값을 다기능 칩 입력 값으로 전달한다. 해당 알고리즘은 레이더 실시간으로 계산하는 것도 한 가지 방법이 되고 이미 보정 된 64×64 행렬 테이블을 저장하여 레이더 운용 시 바로 적용시키는 것도 가능하다.

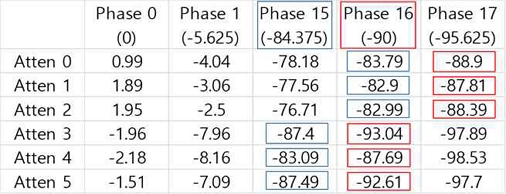

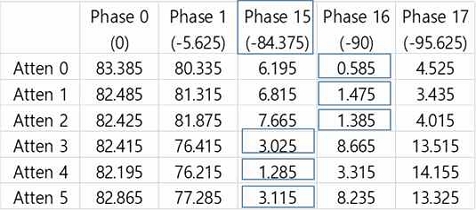

그림 8은 보정 전/후 측정한 크기/위상별 감쇄 값이다. 그림 4와 마찬가지로 감쇄를 많이 할수록 오차가 커지는 경항을 보인다. 보정알고리즘을 거치고 난 후의 오차 값을 보게 되면 감쇄를 많이 하더라도 보정 전 대비 0dB에 가까운 값을 보인다. 그림 9는 보정 후 계산된 디지털 비트 값이다.

위상 보정 단계이다. 위상 보정은 위상 초기 값이 반도체송수신모듈 채널별로 상이하기 때문에, 우선적으로 Zeroing이라 부르는 각 크기별 위상별 값이 0°에 가장 가까운 값을 찾아 셋팅 하여 초기 값이 0°가 되도록 한다.

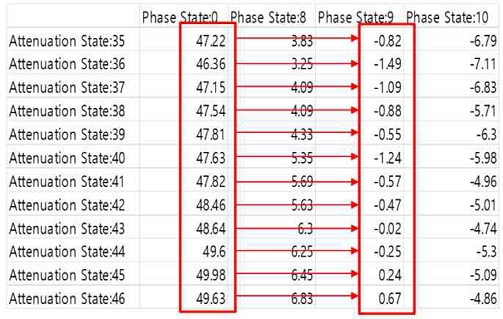

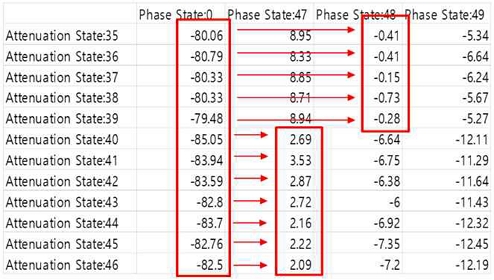

그림 10과 11을 통해 위상 초기 값이 위상 제어 값 0일 때 완전히 다른 값을 보이는 것을 알 수 있다. 그림 12와 같이 반도체송수신모듈 1번 채널 같은 경우 각 감쇄 값 별 위상 비트 9일 때 0°에 가장 가까운 값이며 그림 11은 반도체송수신모듈 2번 채널 에 대한 위상 0°에 가장 가까운 값을 찾는 것이다. 감쇄 값별로 다른 위상 제어하는 것을 알 수 있다. Zeroing 후 위상이 위상 비트 0비트 일 때 측정된 위상 값이 0°에 가장 근사한 값이며 이는 그림 12에 표현하였다. 이때 해당하는 위상 보정 값은 그림 13에 표현하였다.

이후 각 위상 비트별 기댓값과 실제 값의 차이를 그려보면 그림 5와 같이 나타난다. 이후 오차 보정 단계이다. 시스템 연산으로 찾아내기 위해서는 수식이 필요하고 계산을 하여 찾아내기 위한 수식이 식 (1) 이다. Phasesetvalue는 해당 비트별 기대 값, Phaserealvalue는 실측값이며 해당 수식을 감쇄 별 위상 기대 값 비트를 0~63까지 가변 하여 64번의 연산을 수행한 결과를 그림 14에 나타내었다.

| (1) |

그림 14의 첫째 행 가로축 괄호 안에 적혀는 값이 Phasesetvalue이고 2번째 행 첫째 열을 제외한 값은 Phaserealvalue이다. 위상 비트 15를 입력하였을 때, 기대하는 위상 값은 -84.375°이지만 실제 측정되는 값은 -78.18°이고 기대하는 값인 -84.375°에 가장 가까운 값은 위상 비트 16을 제어하였을 때 실측되는 -83.79°값이다. 즉 감쇄 0 위상 15비트에 해당하는 위상 보정 값은 16비트가 되는 것이다. 마찬가지로 각 감쇄 값 단계별로 원하는 기대 값에 가장 가까운 실측값을 갖는 위상 비트 값을 찾아 셋팅 함으로서 보정이 된다. 그림 14를 통해 감쇄 비트 0, 위상비트 15일 때 기댓값에서 가장 가까운 보정 값을 위상 16비트로 확인이 된다.

그림 15를 통해 위상 비트 16일 때 가장 작은 오차를 보이는 것을 확인할 수 있다. 이와 같이 각각의 크기, 위상 값을 보정하고 그래프로 표현하게 되면 그림 16, 17과 같이 크기/위상별 오차 값이 크게 줄어든 것을 확인 할 수 있다. 크기 보정 전인 그림 4에서는 피크-피크 오차 값이 약 3dB 이지만 보정 후인 그림 17에서는 피크-피크 오차 값이 약 0.8dB로 낮아졌다.

마찬가지로 위상 보정 전인 그림 5에서는 피크-피크 오차 값이 약 16° 이지만 보정 후에서는 그림 18처럼 약 4°도 줄어들었다.

2.3 결과 분석 및 설계 유의사항

그림 18은 본 논문의 알고리즘을 테스트하기 위해 제작된 반도체송수신모듈이다. 송신 수신 경로의 격리도를 확보하기 위해 각각의 실장 되는 MMIC마다 접지패턴을 이용해 보호를 하였고 기구적으로 격벽을 구성하여 격리도를 더욱 상승 시켰다[6]. 또한 공간 발진을 막기 위해 기구 상부에 흡수체를 부착하였다[7].

표 2는 보정 전후 크기/위상에 대한 오차 값이다. 크기 오차는 3dB에서 0.8dB로 줄어들었고 위상 오차는 16°에서 4°로 감소하였다.

표 3은 제작된 반도체송수신모듈의 RF 성능을 보여준다. 주파수는 S-band이고 출력은 35dBm 이상이다. 신호 전달을 최대화하기 위한 VSWR은 1.5 : 1 이하이며 불요파는 -40dBc 이하로 측정되었다.

보정 시, 유의해야할 사항은 다음과 같다. 첫째로 RF/Analog 회로의 기생성분에 의한 오차가 매우 크더라도 디지털 시스템 단계에서 보정을 하는 알고리즘이기에 오차를 크게 개선할 수 있다. 하지만 레이더 운용중간에 보정을 위한 계산을 할 시간이 있는지 확인을 해야 한다. 본 논문의 알고리즘은 50ns Clock을 이용하여 6bit를 연산하는데 64×64 행렬을 계산해야 함으로 1.22ms가 필요하다. 이는 레이더의 자원관리 측면에서 시간을 확보해야 한다[8]. 알고리즘을 구현함에 있어 시간은 FPGA 사용 Clock을 더 줄임으로 서 시간을 단축하는 것이 가능하다[9]. 만약 시간이 부족하다면 외부에서 계산된 최종데이터를 입력하여 운용 중에는 해당 값만 적용 가능하다. 둘째로 해당 오차는 채널별 다른 오차 보정 값이 필요함으로 디지털 하드웨어에 비휘발성 메모리가 필요하다. 디지털 부 보드의 기능과 공간 확보를 상호 조율해야 한다.

Ⅲ. 결론 및 향후 과제

본 논문에서는 AESA의 반도체송수신모듈에 대한 크기/위상 값 보정에 대해 알고리즘 설계 및 측정결과까지 기술 하였다. 레이더에서 반도체송수신모듈의 크기/위상 보정이 중요한 이유는 안테나 빔 조향 시 정확한 빔 조향 방향과, 빔폭, 주엽과 부엽의 차이에 대한 성능에 영향을 끼치기 때문이다. 해당 성능이 저하 될 시, 목표에 대한 탐지율이 떨어지게 된다. 빔 조향 방향과 주엽과 부엽의 크기 차이를 만들기 위해 반도체송수신모듈내의 다기능 칩에 크기/위상 가변 기능을 이용하게 되는데 안테나 빔 패턴 시뮬레이션 결과와 근접하게 나오기 위해서는 안테나시스템 설계자가 원하는 크기/위상 값이 반도체송수신모듈의 각 채널별로 적용이 되어야 한다. 본 연구의 결과를 요약하면 다음과 같다.

반도체송수신모듈내의 비선형성을 가진 소자를 이용해 RF회로를 구성하고, 다기능 칩을 이용해 알고리즘을 구현 후, 크기/위상 가변에 대한 선형성을 상승 시켜 확인하였다. 보정 전 크기/위상 값에 대한 오차는 약 피크-피크 3dB, 16°로 측정되었고, 보정 후 오차 값은 0.8dB, 4°로 측정되어 알고리즘의 효과를 확인하였다. 본 논문에서 적용한 반도체송수신모듈 보정 알고리즘은 여러 레이더 시스템에 널리 이용될 수 있을 것으로 사료된다.

References

- A.K. Agrawal et al., "Active Phased Array Antenna Development for Modern Shipboard Radar System", Johns Hopkins APL Tech. Dig., Vol. 22, No. 4, pp. 600-613, Oct. 2001.

-

Venkata Kishore Kothapudi, and Vijay Kumar, "Compact 1x2 and 2x2 Dual Polarized Series-Fed Antenna Array for X-Band Airborne Synthetic Aperture Radar Applications", Journal of Electromagnetic Engineering And Science, Vol. 18 No. 2, pp. 117-128, 2018.

[https://doi.org/10.26866/jees.2018.18.2.117]

-

Jeom Hun Lee and Seung hyeub Oh, "Multi-beam Antenna Analysis", International Journal of Aeronautical and Space Sciences, Vol. 5, No. 2, pp. 71-76, Dec. 2004.

[https://doi.org/10.5139/IJASS.2004.5.2.071]

- Richards, M. A., "Fundamentals of Radar Signal Processing", McGraw-Hill Book Company, New york, 2005.

-

S. Y. Choi, B. H. Lee, and B. J. Park, "Design of Multi Function Chip Correction Algorithm for Radar", The Journal of KIIT, Vol. 18, No. 6, pp. 81-88, Jun. 2020.

[https://doi.org/10.14801/jkiit.2020.18.6.81]

-

In-Ho Choi and Hee-Jung Roh, "Design of J-class Broadband Amplifier", The Journal of KIIT, Vol. 18, No. 3, pp. 59-65, Mar. 2020.

[https://doi.org/10.14801/jkiit.2020.18.3.59]

-

J. C. Pedro and S.A. Maas, "A Comparative Overview of Microwave and Wireless Power-Amplifier Behavioral Modeling Approaches", IEEE Tran. MTT, Vol. 53, No. 4, pp. 1150-1163, Apr. 2005.

[https://doi.org/10.1109/TMTT.2005.845723]

- In-Pyung Jeun, Jae Hoon Bae, Kwang Yun Hwang, and Young Kil Kwag, "Pulse Doppler Airborne Radar Signal Measurement and Detection Performance Analysis Using High Speed Real-Time Data Acquisition System", International Technical Conference on Dircuits Systems, Computers and Communications, Vol. 3, pp. 869-870, Jul. 2005.

-

Byoung-Woo Oh, "Parallel Algorithm for Spatial Data Mining Using CUDA", JAITC, Vol. 9, No. 2, pp. 89-97, Dec. 2019.

[https://doi.org/10.14801/JAITC.2019.9.2.89]

2013년 2월 : 전북대학교 전자공학과(공학사)

2016년 8월 : 경북대학교 전자공학부(공학석사)

2016년 9월 ~ 현재 : 한화시스템 HW팀(레이다) 연구원

관심분야 : RF 증폭기, RF 다기능칩, MMIC, Radar Hardware

1999년 2월 : 동국대학교 전자공학과(공학사)

2001년 2월 : 동국대학교 전자공학부(공학석사)

2006년 2월 : 동국대학교 전자공학부(공학박사)

2006년 2월 ~ 현재 : 한화시스템 HW팀(레이다) 연구원

관심분야 : 능동 위상 배열 시스템, RFIC, RF 고출력 증폭기 설계, 송수신 Front-End 설계

2018년 2월 : 동국대학교 전자공학과(공학사)

2020년 2월 : 동국대학교 전자공학부(공학석사)

2021년 5월 ~ 현재 : 한화시스템 HW팀(레이다) 연구원

관심분야 : 위성통신 설계, RF