입력 전압 크기와 무관한 일정 트랜스컨덕턴스 구현을 위한 폴디드 캐스코드 연산 증폭기 설계

초록

레일 투 레일 구조는 NMOS와 PMOS를 같이 사용하여 입력 범위를 VSS부터 VDD까지 전 범위로 확장시켰다. 하지만 두 트랜지스터의 동작이 겹치게 되면서 트랜스컨덕턴스의 변화를 야기하였다. 트랜스컨덕턴스가 일정하지 않다는 것은 전 범위를 입력으로 사용하는 레일 투 레일 구조에서 비선형 왜곡 문제를 초래하게 되고 주파수 보상을 방해하여 안정성에 문제를 일으킨다. 본 논문에서는 전류 미러 구조를 응용하여 트랜스컨덕턴스 변화량을 획기적으로 낮추는 방법을 제안하였다. 제안한 회로는 TSMC 0.18μm CMOS 공정을 사용하여 구현하였으며 Cadence Virtuoso를 사용하여 검증하였다. 검증 결과 93dB의 이득과 437MHz의 단위 이득 대역폭, 1.8%의 트랜스컨덕턴스 변화율을 확인하였다.

Abstract

The rail-to-rail structure using NMOS and PMOS together widened the input range from VSS to VDD. However, the operation of the two transistors overlapped and caused the change in transconductance. Non-uniform transconductance caused nonlinear distortion problems in rail-to-rail structures that use the full range as input. Also, it interfered with frequency compensation, causing stability problems. In this paper, we propose a method to dramatically reduce the amount of transconductance change by applying the current mirror structure. The proposed circuit was designed using TSMC 0.18μm CMOS process and verified using Cadence Virtuoso. As a result of verification, it was confirmed that it had a gain of 93 dB, a bandwidth of 437MHz of unit gain and a transconductance change rate of 1.8%.

Keywords:

constant transconductance, folded cascode op amp, rail-to-rail input stage, fully differential amplifierⅠ. 서 론

가장 대표적인 증폭기 중 하나인 공통 소스 증폭기는 단채널 효과로 인해 충분히 높은 전압 이득을 가질 수 없고 이를 보완하기 위해 캐스코드 증폭기가 등장하였다. 캐스코드 증폭기는 공통 소스 증폭기 위에 공통 게이트 증폭기를 쌓음으로써 이전보다 높은 전압 이득을 갖는 장점이 있지만 출력 전압의 폭이 좁아지는 단점이 있다. 이러한 단점은 회로를 접는 폴디드 캐스코드 증폭기로서 해결이 가능하게 되었다. 비록 전력은 이전보다 약 두 배 더 소모하게 되지만, 단채널 소자를 사용하더라도 높은 전압 이득과 넓은 출력 전압의 폭을 가지게 되었다.[1]

소자의 크기가 작아짐에 따라 공급 전압 또한 감소하게 되었고 이는 저전압 어플리케이션에서 넓은 입력 전압 범위를 가질 수 없다는 단점으로 작용하게 되었다. 이의 해결책으로 n-type MOSFET뿐만 아니라 p-type MOSFET도 동시에 입력단으로 사용하여 높은 전압일 때 NMOS가, 낮은 전압일 때 PMOS가 동작하는 레일 투 레일 구조가 등장하게 되었다. 그러나 레일 투 레일 구조는 NMOS와 PMOS를 같이 사용하기 때문에 트랜스컨덕턴스가 입력 전압에 따라 변하는 문제점이 존재한다. 이러한 단점을 해결하기 위해 여러 연구가 선행되었다[2]-[5]. 대표적으로는 트랜지스터를 다이오드 구조를 사용하는 방법[6][7], 소스 팔로워를 응용한 레벨 쉬프터를 사용하는 방법 등이 있다[8][9].

본 논문에서는 입력 전압 크기에 따라 불균일한 트랜스컨덕턴스를 해결하는 새로운 방법을 제안하였고, 트레이드 오프로 인해 낮아진 전압 이득을 보상하기 위한 게인 부스팅 회로를 추가하였다. 기존 회로들과 결과를 비교해 보았을 때 높은 전압이득과 낮은 트랜스컨덕턴스 변동률을 가지며, 스케일링을 통해 낮은 전력 소모의 구현이 가능한 회로를 제시하고자 한다.

Ⅱ. 레일 투 레일 입력단

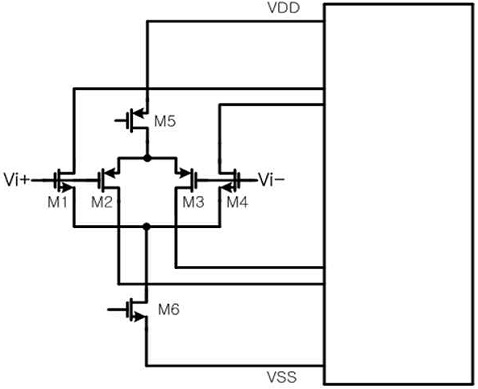

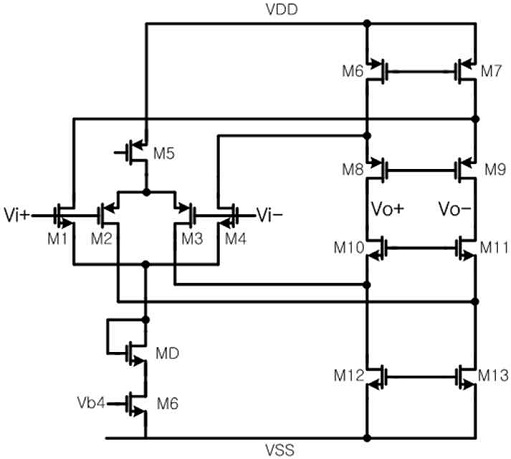

레일 투 레일 구조의 입력단을 그림 1에 나타내었다. 공통모드 동작을 생각해 볼 때 NMOS 쌍과 PMOS쌍의 공통모드 동작범위는 다음과 같다.

| (1) |

| (2) |

식 (1)과 식 (2)를 이용하여 최소 공급 전압을 구하면 다음과 같다.

| (3) |

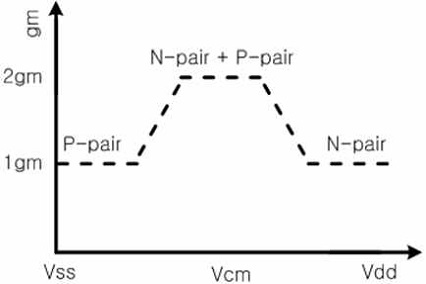

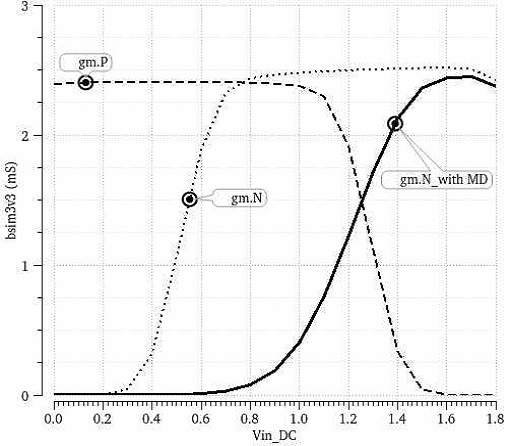

식 (3)에서 알 수 있듯이 NMOS와 PMOS를 같이 사용했을 경우 공통모드 입력전압의 범위를 VDD부터 VSS까지 사용 가능함을 알 수 있다. 하지만 이와 같은 레일 투 레일 구조는 공통모드 입력전압이 변함에 따라 입력단의 트랜스컨덕턴스인 gm이 변한다는 단점이 있다. 공통모드 입력전압의 변화에 대한 트랜스컨덕턴스의 변화를 그림 2에 나타내었다.

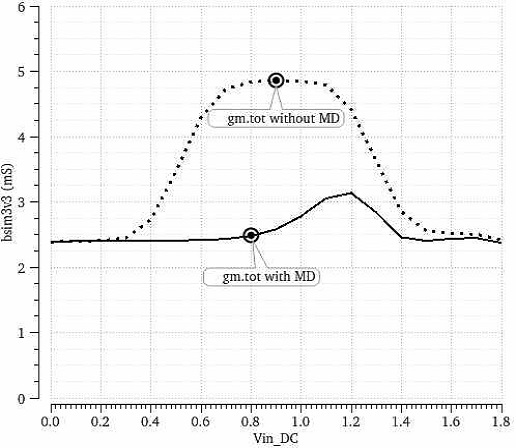

NMOS와 PMOS가 포화되었을 경우 같은 값을 가진다고 가정하였다. NMOS와 PMOS를 입력단에 같이 사용하였기 때문에 입력 트랜스컨덕턴스 또한 NMOS와 PMOS가 기여하게 되고 두 트랜지스터가 동시에 작동하는 중간 영역에서의 트랜스컨덕턴스는 높아지게 된다. 트랜지스터가 포화했을 때의 트랜스컨덕턴스를 gm으로 가정하였기 때문에 중간 영역의 트랜스컨덕턴스는 2gm이 되고 나머지 영역의 트랜스컨덕턴스는 1gm이 된다. 일반적으로 증폭기의 이득은 다음과 같이 트랜스컨덕턴스와 출력 저항의 곱으로 표현할 수 있다.

| (4) |

식 (4)를 통해서 공통모드 입력전압에 따른 트랜스컨덕턴스의 변동은 직접적으로 이득의 변동을 초래한다는 것을 알 수 있다. 또한 증폭기의 단위 이득 대역폭은 다음과 같다.

| (5) |

이때 CC는 주파수 보상용 커패시터이다. 트랜스컨덕턴스가 변함에 따라 단위 이득 대역폭 또한 변하는 것을 식 (5)를 통해서 알 수 있다. 단위 이득 대역폭의 변동을 막기 위해서는 보상용 커패시터가 트랜스컨덕턴스의 변화에 비례하게 변화해야 한다. 즉 트랜스컨덕턴스가 기존의 값보다 두 배가 되는 범위에서는 보상용 커패시터가 기존의 두 배의 값을 가져야 한다.

하지만 이와 같이 실시간으로 트랜스컨덕턴스의 변화에 대응하여 커패시터값을 변화시키는 것은 불가능하다. 따라서 레일 투 레일 구조의 입력단을 사용할 경우 이와 같은 비선형 왜곡을 방지하고 최적의 주파수 보상에 대한 방해를 보호하기 위해서는 동작 전압과 관계없이 일정한 트랜스컨덕턴스를 유지하는 것이 매우 중요하다.

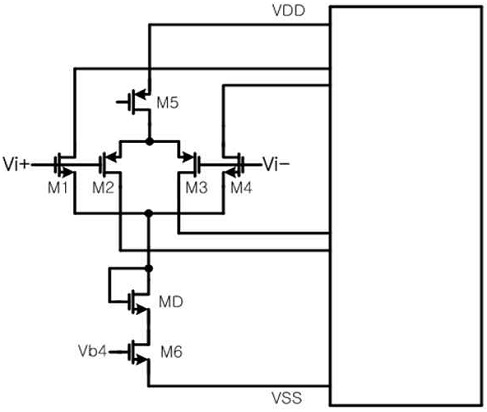

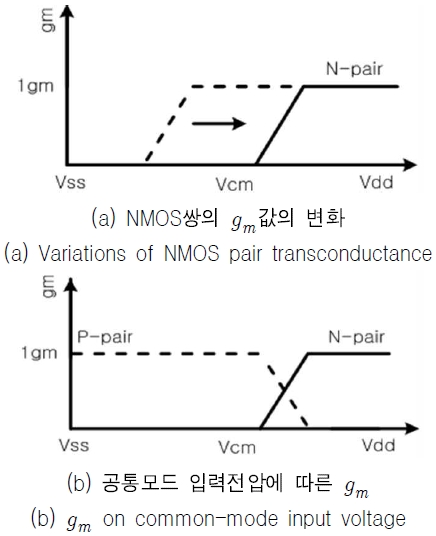

Ⅲ. 일정한 트랜스컨덕턴스를 갖는 기존 회로

일정한 트랜스컨덕턴스를 갖는 기존의 간단한 회로를 그림 3에 나타냈다[6]. 기존 NMOS 입력 차동쌍을 바이어스 하기 위한 트랜지스터 M6의 위에 트랜지스터 MD를 추가하여 다이오드 구조로 사용하였다. 위와 같은 간단한 방법으로 NMOS가 동작하기 위해 필요한 전압의 크기를 높일 수 있게 된다. 이는 그림 4(a)에 나타내었다. 그림 4(b)에서 알 수 있듯이 입력단의 NMOS와 PMOS가 포화했을 때 트랜스컨덕턴스 값이 같다면 대부분의 영역에서 일정한 트랜스컨덕턴스 값을 유지할 수 있다. 이를 테스트하기 위한 회로는 그림 5와 같다.

그림 5는 기본적인 레일 투 레일 폴디드 캐스코드 증폭기에서 일정한 트랜스컨덕턴스를 구현하기 위해 MD가 추가된 회로이다. 회로의 입력과 출력이 모두 차동모드인 완전 차동 증폭기이기 때문에 안정성을 위한 공통모드 피드백 회로가 필요하지만 그림 5에서는 생략하였다.

공급전압을 1.8V로 설정한 상태에서 입력 전압에 따른 트랜스컨덕턴스의 변화를 트랜지스터 MD의 유무에 따라 비교해 놓은 결과를 그림 6과 그림 7에 나타내었다. 그림 4의 예상과 같이 NMOS 입력단 아래에 다이오드 구조를 가진 트랜지스터 MD를 추가할 경우 NMOS의 동작 영역이 우측으로 밀리는 것을 그림 6을 통해 확인 할 수 있었다. 일반적인 증폭기는 트랜스컨덕턴스가 1gm~2gm 범위에서 변하게 되지만 MD를 추가하여 NMOS의 동작을 밀음으로서 트랜스컨덕턴스의 변화를 줄일 수 있음을 그림 7을 통해 확인하였다. 그림 7에서 변화량을 측정해 보았을 때 일반적인 회로는 1gm에서 2gm으로 약 100%의 변화량을 보이지만 트랜지스터 MD를 추가함으로써 약 23% 정도로 변화량을 줄일 수 있다.

본 논문에서는 그림 5의 회로를 기반으로 트랜스컨덕턴스를 획기적으로 줄이는 방법을 제안하였다. 또한 낮아진 트랜스컨덕턴스로 인해 약 반으로 줄어든 이득을 보상하기 위해 이득 증폭회로를 추가한 회로를 사용하였고 이를 측정하였다.

Ⅳ. 제안하는 회로의 동작 원리

4.1 일정 트랜스컨덕턴스를 갖는 회로 제안

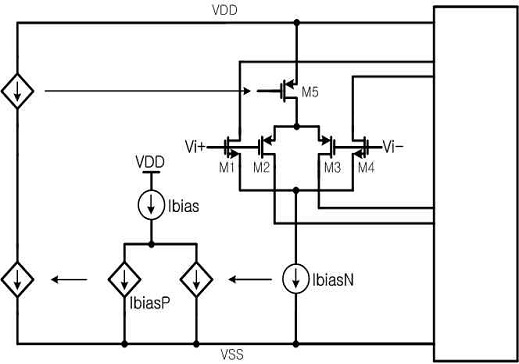

일정한 트랜스컨덕턴스를 갖기 위해 새롭게 제안하는 회로를 그림 8에 나타내었다. 두 트랜지스터가 동시에 작동할 때의 트랜스컨덕턴스를 일정하게 하기 위한 회로의 원리는 다음과 같다. 그림 5에서 MD와 M6에 흐르는 전류를 IbiasN로 가정하여 그림 8에 구현해 놓았다.

전류 미러 구조를 통해 IbiasN에 해당하는 전류를 외부의 회로에서 흘리게 된다. 이때 추가적인 회로가 정전류원에서 Ibias만큼의 전류를 공급받고 있다고 한다면 전류 IbiasP는 다음과 같이 표현할 수 있다.

| (6) |

외부에 추가된 회로에서 생성된 전류 IbiasP를 전류 미러 구조로 복사를 하고 싱크 전류원을 소스 전류원으로 바꾸었다. 생성된 소스 전류원에서도 전류 미러 구조를 이용하여 트랜지스터 M5에 전류를 복사해 준다면 트랜지스터 M5에도 IbiasP 전류가 흐르게 된다. 따라서 NMOS 입력쌍은 전류 IbiasN으로서 바이어스되고 PMOS 입력쌍은 전류 IbiasP로서 바이어스가 된다. 이때의 레일 투 레일 입력단의 트랜스컨덕턴스의 총 변화량은 다음과 같다.

| (7) |

트랜스컨덕턴스 gm은 MOSFET의 게이트 단자에 걸리는 전압을 드레인 전류로 나누어 준 것과 같다. 즉, NMOS 입력단의 트랜스컨덕턴스와 PMOS 입력단의 트랜스컨덕턴스는 식 (8)과 식 (9)와 같이 나타낼 수 있으며 두 식을 이용하여 식 (7)을 정리하면 식 (10)과 같다.

| (8) |

| (9) |

| (10) |

여기서, 식 (6)을 이용하여 식 (10)을 정리한 결과는 다음과 같다.

| (11) |

| (12) |

그림 8에서 Ibias는 새롭게 추가된 회로에서 전류를 공급해 주고 있는 정전류원이므로 전류는 변하지 않는다. 따라서 위 식에서 ΔIbias = 0 이 되고, 이를 이용하여 식 (12)를 정리해보면 Δgm.tot = 0 이 된다. 즉, 입력단의 전체 트랜스컨덕턴스의 변화량이 없음을 알 수 있고 따라서 제안한 구조의 원리를 사용할 경우 일정한 트랜스컨덕턴스를 가지는 회로의 구현이 가능하다. 하지만 기존의 회로의 경우 트랜스컨덕턴스가 최대 2gm의 값을 가지면서 증폭기의 이득이 2gm✕rout으로 표현할 수 있었으나, 제안한 회로의 경우 비록 일정한 트랜스컨덕턴스를 가지지만 1gm의 값을 가지기 때문에 증폭기의 이득이 1gm✕rout으로 기존보다 반으로 줄어든 것을 알 수 있다. 따라서 입력단은 트랜스컨덕턴스를 일정하게 구현하면서 증폭단은 기존보다 높은 출력 저항을 가지게 하여 제안하는 구조로 인한 성능 저하를 최소화 시켜야 한다.

4.2 이득 부스팅을 위한 회로

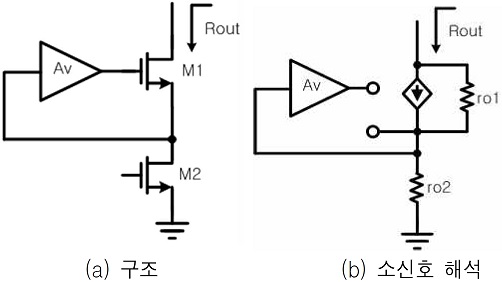

이득 부스팅을 설명하기 위한 회로를 그림 9에 나타냈다. M1과 M2로 구성된 일반적인 캐스코드 구조의 경우에 각각의 내부저항을 ro1, ro2라고 할 때 출력 저항은 다음과 같다.

| (13) |

그림 9(a)는 캐스코드 구조에서 M1의 소스 단자의 전압을 입력으로 받아 M1의 게이트 단자에 출력 전압을 인가하는 증폭기가 연결된 구조이다. 그림 9(a)의 회로를 소신호 모델로 표현한 것을 그림 9(b)에 나타내었다. 출력 저항 Rout은 출력단자의 전압을 전류로 나누어 계산 할 수 있다. 이때의 전압과 전류를 각각 Vt, it라고 할 때, ro2에 흐르는 전류는 it가 된다. 즉, ro1 하단의 전압을 Vx 라고 표현 할 때 그 전압은 Vx = it × ro2라고 표현 할 수 있다. Vx전압은 AV만큼 증폭하는 증폭기의 입력으로 들어가게 되며 출력은 AV × Vx가 된다. 능동 전류원이 흘려주는 전류의 값은 다음과 같다.

| (14) |

출력 저항을 측정하기 위한 전압 Vt을 계산해보면 다음과 같다.

| (15) |

| (16) |

| (17) |

이때에 전압이득 AV가 음의 값을 가진 반전증폭기라면 출력 저항은 다음과 같이 근사할 수 있다.

| (18) |

즉, 이득 부스팅 기법을 활용한다면 기존 회로의 출력 저항보다 보조증폭기의 이득만큼 출력 저항을 높일 수 있다. 따라서 제시된 레일 투 레일 입력단에서 일정한 트랜스컨덕턴스를 유지하기 위해 반으로 낮아진 이득을 이득 부스팅을 사용하여 충분히 보상할 수 있다.

Ⅴ. 제안하는 회로의 최종 구현 및 결과 검토

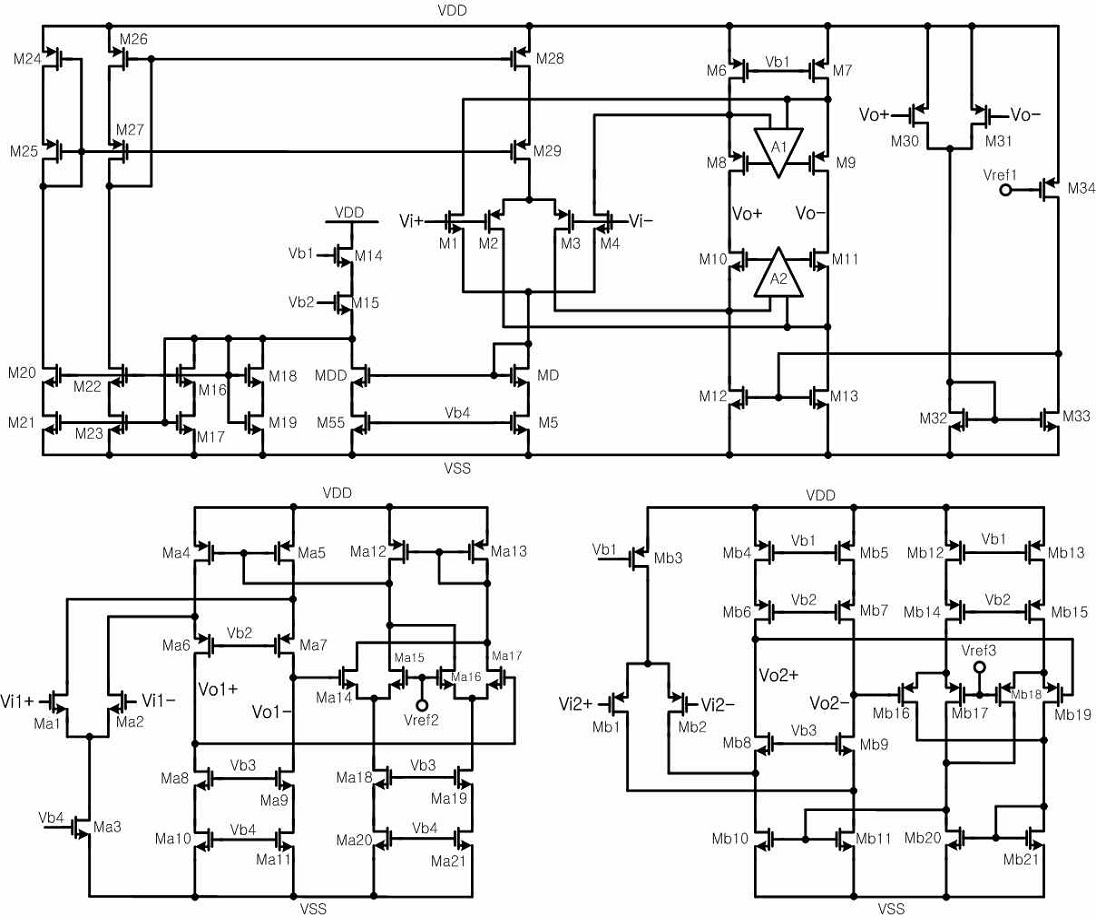

일정한 트랜스컨덕턴스와 높은 이득을 가진 회로를 그림 10에 제안하였다. 상단은 메인증폭기이고 하단은 게인 부스팅을 위한 보조증폭기이며 각각 A1, A2로 표현하였다. 메인 증폭기의 입력단은 그림 8에서 제시한 일정한 트랜스컨덕턴스를 가지는 구조를 사용하였다. 일정한 전류를 공급하기 위한 정전류원 역할을 M14, M15로서 구현하였으며 전류는 Ibias가 흐르게 된다. M16~19로 Ibias-IbiasN인 전류 IbiasP만큼 흐르게 되고 이를 M20~23이 전류 미러 구조로 복사해온다. 복사된 싱크 전류원은 M24~27으로 소스 전류원으로 바꾸었다.

마찬가지로 소스 전류원에서 전류 미러 구조를 통해 M28, M29에 전류를 복사해 주며 따라서 PMOS 입력단인 M2와 M3에 일정한 트랜스컨덕턴스를 위한 적절한 바이어스를 해주게 된다. 메인 증폭기 뒷단은 폴디드 캐스코드 증폭단의 구조에 보조증폭기 A1, A2를 이용한 게인 부스팅 구조로 이루어져있다.

A1은 M8, M9의 소스 전압을 입력으로 받으며 출력은 게이트 전압에 인가하게 된다. M8과 M9의 소스 단자는 주로 높은 전압이기 때문에 A1의 입력단은 레일 투 레일이 아닌 NMOS로 구현하였다. A2는 M10, M11의 소스 전압을 입력으로 받으며 출력은 게이트 전압에 인가하게 된다. M10과 M11의 소스 단자는 주로 낮은 전압이기 때문에 A2의 입력단은 PMOS로 구현하였다. 게인 부스팅 구조가 추가된 전체 회로의 전압 이득은 식 (19)와 같다.

| (19) |

이때 보조 증폭기의 전압 이득 Aaux1과 Aaux2의 전압 이득은 다음과 같다.

| (20) |

| (21) |

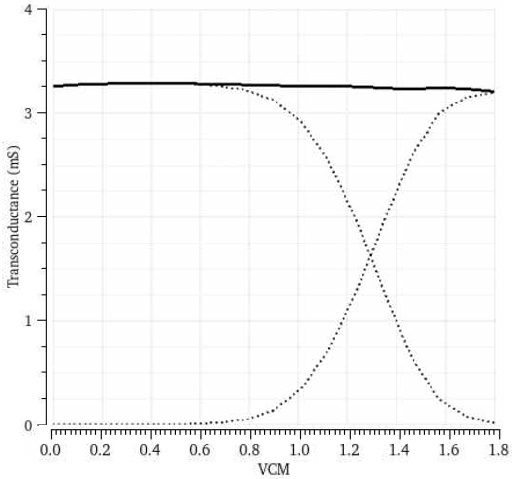

제안한 회로에서 메인 증폭기와 보조 증폭기 A1과 A2 모두 입력과 출력이 차동모드인 완전차동 증폭기 구조이다. 차동 증폭기에서 공통모드에 대한 안정성을 갖기 위해 필요한 공통모드 피드백 회로는 M30~34, Ma12~21, Mb12~21에 구성되어 있다. 공통모드 피드백 회로를 통하여 입력전압의 공통모드 동작을 제한하여 출력전압을 온전히 차동모드로서 동작시킬 수 있다. 그림 10의 회로에 대하여 입력 트랜스컨덕턴스를 측정해 본 결과는 그림 11에 나타나있다. 식 (12)에서 계산을 했을 때 트랜스컨덕턴스의 변화량은 0이였지만 실제 회로에서 측정하였을 때 1.8%의 변화량을 보였다.

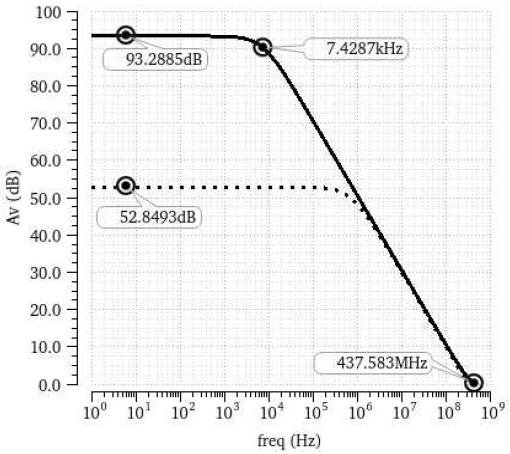

주파수에 따른 이득은 그림 12에 나타내었다. 게인 부스팅 기법을 사용하기 전에는 약 53dB의 이득을 보였으나 게인 부스팅 기법을 사용하여 약 93dB의 높은 이득을 보인다. 차단 주파수는 7.4kHz이며, 단위 이득 주파수는 437MHz이다.

제안한 회로의 자세한 파라미터들을 표 1에 나타내었다. 기존의 논문들과 비교해 보았을 때 높은 이득과 낮은 트랜스컨덕턴스 변화량을 가지는 것을 알 수 있다.

Ⅵ. 결 론

본 논문에서는 게인 부스팅 회로가 추가된 일정한 트랜스컨덕턴스를 가지는 폴디드 캐스코드 연산 증폭기를 제안하였다. 기존의 논문은 트랜스컨덕턴스의 변화율을 100%에서 약 20% 정도로 낮추는 것에 그쳤으나 본 논문에서는 그 회로를 응용하여 1.8%의 변화율을 갖는 회로를 구현하였다. 또한 추가된 게인 부스팅 회로로 인하여 93dB의 전압 이득을 가지게 되었다. 이는 기존 논문들이 최소 2.3%의 트랜스컨덕턴스 변화율을 갖고, 최대 89dB의 이득을 갖는 것과 비교해 보았을 때 본 논문의 회로가 더 우수하다는 것을 표 1을 통해 알 수 있다.

제안된 회로는 범용성을 위해 300uA의 높은 전류로 바이어스 되어 약 25V/μs의 높은 슬루율과 1.22mW의 전력 소모라는 특징을 가진다. 비록 기존의 회로보다 많은 수의 트랜지스터가 추가되었으나 일정한 트랜스컨덕턴스를 구현하는 원리는 전류 미러를 기본 원리로서 사용하므로 비율에 맞춰 사이즈를 줄이는 것이 가능하며 전력 소모와 면적 또한 낮출 수 있을 것으로 예상된다. 식 (12)에서 알 수 있듯이 제안하는 구조는 저전력을 위하여 바이어스 전류를 낮추어도 트랜스컨덕턴스에는 변화를 주지 않는다. 이론상 트랜스컨덕턴스의 변화량을 0으로 예상하였으나 M!4와 M15를 이용해 구현한 전류원이 이상적인 전류원이 아니며 M16~29로 이루어진 전류 미러 구조 또한 이상적이지 않기 때문에 약간의 전류 변화를 포함한 오차가 생기게 되고 이러한 결과가 1.8%의 트랜스컨덕턴스의 흔들림으로 나타나게 되었다고 판단된다.

트랜스컨덕턴스의 변화량에 영향을 최소화하기 위해서는 M14, M15로 구현한 기본적인 캐스코드 전류원 구조를 더 높은 출력 저항을 가지는 적절한 전류원 구조로 대체해야 하고 마찬가지로 전류 미러 구조 또한 이상적인 특성을 가진 구조를 사용해야한다. 전류원 구조와 전류 미러 구조가 이상적일수록 트랜스컨덕턴스의 변화율은 낮아지게 되고 전력 소모 또한 낮출 수 있을 것으로 보인다.

Acknowledgments

본 연구는 IDEC에서 EDA Tool를 지원받아 수행하였습니다.

References

-

M. W. Lee and S. H. Son, "Dual output Rail to Rail CMOS Buffer Amplifier with Low Power and High Slew Rate for LCD Source Driver IC", Journal of JKIIT, Vol. 12, No. 10, pp. 1-9, Oct. 2014.

[https://doi.org/10.14801/kitr.2014.12.10.1]

- E. K. F. Lee, A. Lam, and T. Li, "A 0.65V rail-to-rail constant gm opamp for biomedical applications", IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, pp. 2721-2724, May 2008.

- G. D. Dai, P. Huang, L. Yang, and B. Wang, "A Constant Gm CMOS Op-Amp with Rail-to-Rail input/output stage", 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, Nov. 2010.

-

A. K. Dubey, R. K. Nagaria, P. K. Pal, and R. K. Singh, "Enhanced Slew Rate, Constant-gm Rail-to-Rail OpAmp using 1:2 Current Mirror Biasing Technique", International Conference on Computing, Communication and Automation (ICCCA), Greater Noida, India, pp. 1612-1618, Apr. 2016.

[https://doi.org/10.1109/CCAA.2016.7813982]

-

A. Masoom and Kh. Hadidi, "A 1.5-V, Constant-Gm, Rail-to-Rail Input Stage Operational Amplifier", 13th IEEE International Conference on Electronics, Circuits and Systems, Nice, France, pp. 632-635, Dec. 2006.

[https://doi.org/10.1109/ICECS.2006.379868]

-

B. Lee and T. Higman, "Extremely Simple Constant-gm Technique for Low Voltage Rail-to-Rail Amplifier Input Stage", 18th IEEE International Conference on Electronics, Circuits, and Systems, Beirut, Lebanon, pp. 314-317, Dec. 2011.

[https://doi.org/10.1109/ICECS.2011.6122276]

-

L. L. Malavolta, R. L. Moreno, and T. C. Pimenta, "A Self-Biased Operational Amplifier of Constant gm for 1.5V rail-to-rail operation in 130nm CMOS", 28th International Conference on Microelectronics(ICM), Giza, Egypt, pp. 45-48, Dec. 2016.

[https://doi.org/10.1109/ICM.2016.7847904]

-

M. Wang, T. L. Mayhugh, S. H. K. Embabi, and E. Sanchez-Sinencio, "Constant-gm rail-to-rail CMOS op-amp input stage with overlapped transition regions", IEEE Journal of Solid-State Circuits, Vol. 34, No. 2, pp. 148-156, Mar. 1999.

[https://doi.org/10.1109/4.743758]

-

A. Reda, M. F. Ibrahim, and F. Farag, "Input-output Rail-to-Rail CMOS CCII for low voltage-low power applications", Microelectronics Journal, Vol. 48, pp. 60-75, Feb. 2016.

[https://doi.org/10.1016/j.mejo.2015.12.001]

2020년 2월 : 청주대학교 반도체공학과(공학사)

2020년 3월 ~ 현재 : 청주대학교 반도체공학과(공학석사)

관심분야 : CMOS Analog IC 설계

1983년 2월 : 한양대학교 전자공학과(공학사)

1985년 2월 : 한양대학교 전자공학과(공학석사)

1988년 8월 : 한양대학교 전자공학과(공학박사)

1988년 9월 ~ 1991년 2월 : 순천향대학교 전산학과 전임강사

1991년 3월 ~ 현재 : 청주대학교 반도체공학과 교수

2009년 ~ 2010년 : Univ. of Texas at Dallas 방문교수

관심분야 : CMOS Analog IC 설계 및 센서 신호 처리 회로 설계