CMOS를 이용한 저 중간 주파수 블루투스용 수신기 설계

초록

본 논문에서는 CMOS Low-IF 블루투스용 수신기를 설계하였다. 본 논문에서는 그 동안의 블루투스 수신기의 이미지 문제, 선형성 문제를 해결하기 위해 다중위상 필터, MGTR mixer를 사용하여 블루투스 스펙을 만족하였다. 수신기는 저잡음 증폭기(LNA) MGTR-mixer, 전압 가변 발진기(VCO), 다중위상필터(Poly phase filter), 프로그래머블 이득 증폭기(PGA) 그리고 수신 신호 강도 지수(RSSI)회로로 구성되어 있다. Mixer는 다중 게이트 트랜지스터(MGTR) 기법을 이용하여 선형성을 향상시켰고, charge injection 방법을 사용하여 flicker noise를 감소시켰다. 또한 저 중간주파수 구조를 사용하였기 때문에 image 문제를 해결하기 위하여 다중위상 필터(PPF)를 사용하였다. 수신기 집적회로설계는 0.18μm CMOS 공정을 사용하였고, 수신기 성능은 1.8V 전압 공급에 약 36mA 전류 소모를 하였단. 최소 수신감도는 -86dBm, 이미지 제거 비율은 63dB와 그리고 입력 인터모듈레이션 파워(iIP3)는 -13dBm을 2.4∼2.4835GHz에서 각각 얻을 수 있었다. 폐 루프시, 전압 가변 발진기(VCO)의 위상 잡음은 1MHz offset에서 -126dBc/Hz를 얻을 수 있어서 블루투스 스펙 그리고 다른 논문들과 비교해 성능면에서 월등한 결과를 얻을 수 있었다.

Abstract

This paper describes a design of a fully integrated low-IF CMOS bluetooth receiver. This paper satisfies the bluetooth receiver specification by employeeing PPF (Poly Phase Filter) and MGTR mixer to solve the image problem and linearity problem of conventional blue-tooth receiver. The receiver consists of a LNA, a MGTR (Multiple Gated Transistor)-mixer, a VCO, a PPF, a PGA and a RSSI(Received Signal Strength Indicator). MGTR technique is used for mixer to improve the linearity and charge injection method is used for mixer to decrease the flicker noise. Also, poly phase filter is used for low-IF architecture to minimize the image signal. Implemented in a 0.18μm standard CMOS process, the receiver dissipates approximately 36mA from a 1.8V supply voltage and has -86dBm minimum sensitivity, 63dB image rejection ratio and -13dBm iIP3 from 2.4GHz to 2.4835GHz. The phase noise of the closed loop voltage-controlled oscillator(VCO) is -126dBc at 1MHz offset. This paper achieves the superior performance to blue-tooth specification and other papers.

Keywords:

voltage controlled oscillator, poly phase filter, low noise amplifier, complementary metal oxide semiconductorⅠ. 서 론

블루투스란 2.4GHz 대역의 ISM(Industrial Scientific Medical)밴드에서 동작하는 근거리 무선 통신 기술, 표준, 제품이다.

첫 세대 블루투스제품은 개인용 전자 제품을 저가로 공급하는데 중점을 두었었다. 블루투스에서 사용하고 있는 주파수 밴드는 2400MHz에서 2483.5MHz의 ISM 밴드이다. 변조 방식은 가우시안 주파수 위상 키(GFSK)이고, 1Mb/s 데이터률을 동시에 갖고 있다[1]. 블루투스 표준은 IEEE 802.11a나 802.11b와 같은 다른 단거리 무선 통신 표준에 비해 상대적으로 작은 1Mb/s의 데이터률을 갖고 있지만, 저가격, 저 파워 소모와 작은 모양은 블루투스 송수신기를 만드는데 있어 필수적이다. 많은 블루투스 송수신기를 연구한 논문이나 자료가 여러 문헌에서 보고된 바 있다[2]-[8].

본 논문에서는 저 중간 주파수(Low-IF) 방식 CMOS 블루투스 수신기를 설계하였다. IF 주파수는 1.5MHz를 사용하였고, Low-IF 구조를 선택하였기 때문에 이미지(Image) 문제를 해결하기 위하여 다중 위상 필터(PPF, Poly Phase Filter)를 제시하였다. 수신기 집적 회로설계는 0.18μm CMOS 공정을 사용하였고, 각 블록별로 회로 설계에 대한 내용을 본론에 실었다. 본론에서는 각각의 회로 설계 방법과 설계한 회로의 성능 결과를 다뤘고 결론에서는 이 논문의 요약을 한 번 더 강조 하였다.

믹서(Mixer)는 다중 게이트 트랜지스터(MGTR, Multi Gate Transistor)을 이용하여 선형성을 향상시켰고, charge injection기법을 사용하여 플릭커 노이즈를 감소시켰다. 또한 Low-IF 구조를 사용하였기 때문에 image 문제를 해결하기 위하여 PPF를 사용하였다. 수신기 집적회로 설계는 TSMC 0.18μm CMOS 공정을 사용하였다. 수신기 성능은 1.8V 전압에 약 36mA 전류 소모를 타 논문들과 비교하여 상당히 적은 파워소모를 하였으며, 최저 수신감도는 -86dBm, 이미지 제거 비율은 63dB로 다른 논문들과 비교를 했을시, 탁월한 성능을 얻을 수 있었고, iip3는 -13dBm을 각각 얻을 수 있었다. 폐 루프 시, 전압 가변 발진기(VCO, Voltage Controlled Oscillator)의 위상잡음은 1Mhz 떨어진 곳에서 -126dBc/Hz를 얻을 수 있었고 이 성능 역시 타 논문들과 비교해 우수한 특성을 얻을 수 있었다.

Ⅱ. 관련 연구

2.1 수신기 구조

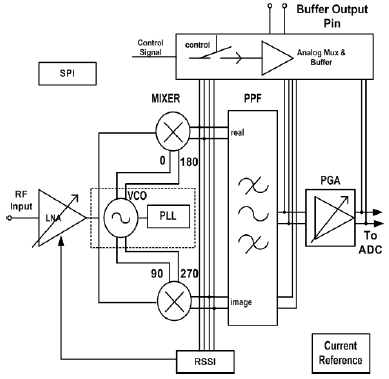

본 논문에서 사용된 수신기 구조는 그림 1과 같이 Low-IF 구조로서 PPF를 이용하여 이미지 신호을 제거하여 준다. Low-IF 구조의 장점으로는 높은 집적도를 얻을 수 있으며 Flicker 잡음이 상대적으로 직접 변환 수신기(DCR) 구조에 비하여 작으며 DC Offset문제를 피할 수 있다는 것이다. 단점으로는 이미지 신호가 발생하는 것인데 이미지 신호를 줄여 주기 위하여 고성능의 PPF를 필요로 하다는 것과 I & Q Signal 부정합 문제가 될 수 있다는 것이다. 하지만 이런 문제들은 단위 회로 설계 시 모두 고려하였다.

이득은 동작 범위를 고려하여 저 잡음 증폭기(LNA, Low Noise Amplifier)에서 높은 게인 모드와 낮은 게인 모드를 갖도록 하였으며, 수신 신호 강도 지수(RSSI, Received Signal Strength Indicator)는 수신기의 신호 및 노이즈 비율을 만족하기 위한 인자로 사용이 되었고, 이는 RSSI단의 이력현상을 통하여 자동으로 조절 할 수 있도록 하였다.

프로그래머블 이득 증폭기(PGA, Programmable Gain Amplifier)의 이득 제어를 통하여 ADC(아날로그 디지털 컨버터)에 충분한 신호진동을 넣어 줄 수 있도록 설계 하였다. 믹서, PPF, PGA의 출력을 모니터링 하기 위하여 모든 회로 출력에 완충회로(Buffer)를 사용하였다.

전체 시스템의 설계 목표는 정상동작 상태에서 신호대 노이즈 비율(SNIR)이 18dB 이상을 만족하면서 최저 수신 감도는 -86dBm과 iIP3(3rd Input Intercept Point), 즉 원신호의 출력전력과 3차 IMD (Inter Modulation Distortion)신호의 출력전력이 동일해지는 점의 입력전력을 의미한다. 즉 입력측의 선형성을 나타내는 지표. iIP3는 낮은 게인 모드시 -13dBm을 만족 하는 것을 전체 시스템 시뮬레이션 프로그램을 통하여 확인 할 수 있었다.

2.2 회로 구현

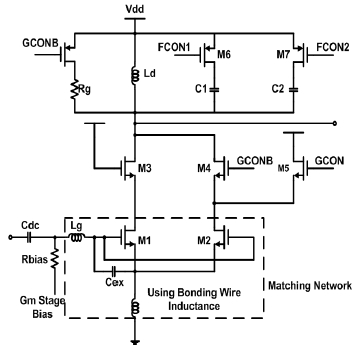

LNA는 그림 2에 보여지는 바와 같이 높은 전력이득과 역 방향 격리도 특성이 좋은 캐스코드 타입을 사용하였으며, 동작 원리는 M4와 M5가 ON, OFF혹은 OFF, ON이 되도록 게인 컨트롤 신호을 사용하였다. 이 모드에 따라 높은 게인 모드와 낮은 게인 모드로 나눠지는데, 이는 입력 신호가 클 때와 작을 때의 수신기 전체의 잡음지수(N.F), iIP3 향상을 위한 목적으로 구분하였다.

또한, FCON1과 FCON2를 조절하여 C1, C2를 출력 단에 short 로 보이는지 open으로 보이는지에 따라 4가지 상태가 주어지는데 공정, 전압, 온도(Process Voltage Temperature) 변화에 대비하여 출력 단에 밴드 선택을 할 수 있도록 하였다. Source degeneration 인덕터는 입력 단 매칭과 잡음 지수를 향상시키기 위해 사용하였는데, 넓은 칩 면적을 차지하는 온 칩 인덕터를 대신해 칩의 본딩 와이어 인덕터를 사용하였다.

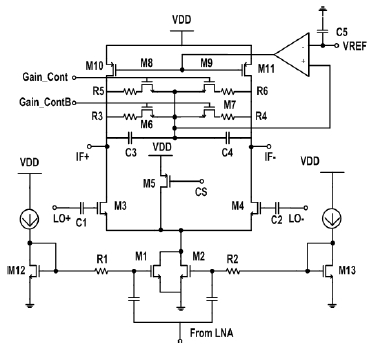

LNA의 출력은 믹서에 의해서 IF 주파수인 I와 Q 신호로 변환되어진다. 믹서의 기본 구조는 전류 소모를 줄이기 위하여 그림 3과 같이 기본적인 길버트 셀로 구성하였다. 믹서의 Gm단은 작은 전력 소모를 하면서 선형성을 만족하기 위하여 MGTR 구조를 차용 하였다[9].

믹서의 스위치단은 Charge Injection을 이용하여 잡음을 줄였으며[10], 믹서의 IF 단은 저항을 스위칭하여 변환 이득을 조절 할 수 있으며 CMFB을 이용 믹서의 중간 모드 레벨을 VDD/2로 맞추어 주었다.

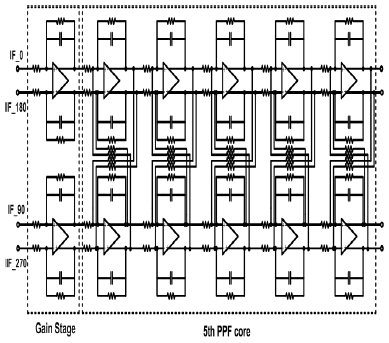

그림 4에서 PPF는 5차 버터워스 저주파 필터의 함수를 주파수 이동하여 구현하였다. 표 1에 5차 버터워스 저주파 필터의 정규치와 700kHz의 대역폭을 가지도록 pole scaling한 것, 그리고 이를 다시 1.5MHz만큼 주파수 이동한 poles의 위치를 나타내었다.

필터를 구현하기 위한 단위 적분기는 선형성이 뛰어난 Active-RC 적분기를 사용하였다. 구현된 PPF의 회로도는 그림 4와 같다.

이득 단은 입력신호를 필터링 하기 전에 신호를 2배로 증폭시켜주는 역할을 한다. 이득 단을 추가함으로써 PPF의 입력 관련 노이즈(IRN) 특성을 개선하였다. 필터의 주파수 튜닝은 5비트 캐패시터 bank를 사용하여 구현 하였다.

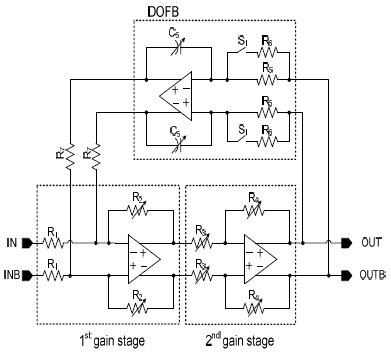

PGA의 회로도를 그림 5에 나타내었다. PGA는 크게 첫 번째 이득 단, 두 번째 이득 단, DC-offset 제거피드백회로(DOFB, DC Offset Feedback)로 구성되어 있다. PGA의 전체 이득은 APGA = (R2·R4)/ (R1·R3)로 주어진다. PGA는 정상 상태에서, 6dB단계로 0dB ~ 48dB의 범위를 가진다. 이 중 0dB ~ 18dB의 범위에서는 R2가 변하고, 24dB ~ 48dB의 범위에서는 R4가 변하여 이득이 바뀌게 된다. R3는 PGA의 이득에 차이를 주는 역할을 한다. 즉 R3의 값에 따라 -6dB ~ 42dB, 0dB ~ 48dB, 0dB ~ 54dB의 세 가지의 이득 범위를 가질 수 있다.

PGA의 동작에 있어서 또 하나 고려해야 할 사항이 안정되는 시간이다. DOFB가 DC신호의 차이를 제거하는 원리는 PGA의 출력차이의 정보를 C5에 전하의 형태로 저장하여 그 차이를 상쇄할 수 있는 전압을 만들고 이를 다시 R7을 통해 입력으로 인가하는 것이다.

PGA의 출력차이의 크기는 이득에 따라 달라지므로 이를 상쇄하기 위해 C5에 저장되어야 할 최적의 전하의 양도 달라져야 한다. 그런데 C5·R5,즉 τ의 값이 매우 커서 그 최적의 값을 찾는데 많은 시간이 소모되고, 이 동안에는 PGA는 정상동작 할 수 없으므로 전체 수신기의 성능에 심각한 영향을 준다. 이를 해결하기 위하여 이득 스위칭시 S1=1로 하여 R5보다 훨씬 작은 R6를 병렬로 연결하였다. 이렇게 하면 τ = C5·R6이 되어 안정되는 시간을 크게 줄일 수 있다.

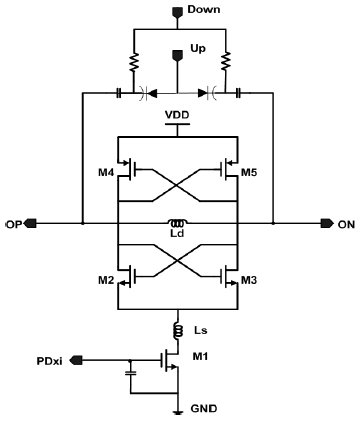

VCO 구조는 그림 6에서 보여 지는 것과 같이 NMOS, PMOS coupled구조를 갖는다. VCO는 6bit 조절 가능한 LC-tank를 가진 구조로 되어 있다. VCO의 출력은 4.8GHz가 되는데, 이를 다음 단에 있는 Divide_2 Block를 통해 주파수를 2.4GHz 로 낮춤과 동시에 4개의 90° 차이가 나는 위상을 만들게 된다. 그 이유는 송신단에서 전력 증폭기 출력과 VCO 출력 주파수가 비슷할 때에 나타날 수 있는 coupling 현상을 막기 위한 것이고 PA 출력 신호와 VCO 출력 주파수간에 나타날 수 있는 injection pulling 현상을 막기 위한 것이다.

VCO의 출력에 캐패시터 배열을 두어서 LC tank의 캐패시턴스를 바꿀 수 있도록 하였다. 이는 모두 64개의 상태를 가지고 있고, 이 상태는 6bits로 표현이 가능하다.

Ⅲ. 설계 성능 결과

3.1 LNA 설계 성능 결과

표 2에서 보여지는 것처럼 전체 LNA의 높은 이득(High Gain) 동작에서는 전압 이득(VG, Voltage Gain)은 25dB를 TT(Typical Temperature)에서 맞추어 놓았고 잡음 지수 도 2.28dB로 성능을 얻을 수 있었다. 입력 S11 매칭도 –14.5dB를 잘 맞출 수 있었다. 입력 IP3도 –13dBm을 얻을 수 있었다.

낮은 이득(Low Gain) 동작에서는 전압 이득(VG)은 4.9dB를 TT모드에서 맞추어 놓았고 잡음 지수도 4.9dB로 성능을 얻을 수 있었다. 입력 S11 매칭도 -14.5dB를 잘 맞출 수 있었다. 입력 IP3도 -17dBm을 얻을 수 있었다.

3.2 믹서 설계 성능 결과

표 3에서 보여지는 것처럼 본 MGTR 구조의 믹서에서는 전압 이득은 TT모드에서 16.7dB를 얻을 수 잇었고 입력 관련 잡음(IRN)은 3.54dB의 성능을 얻을 수 있었고 -37dB의 LO-RF 격리도를 얻을 수 있었고, 입력 IP3도 -13.76dBm을 얻을 수 있어 블루투스 스펙을 만족시키는 믹서 설계를 할 수 있었다.

3.3 PPF 설계 성능결과

저 전력 동작을 위해 opamp의 전류소모를 4단계에 걸쳐 조절 할 수 있도록 하였다.

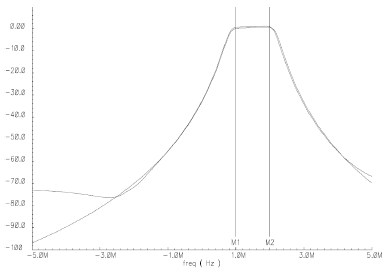

PPF의 주파수 특성은 그림 7과 같다. 설계했던 바와 같이 1.5MHz의 중심 주파수와 1.4MHz의 대역폭을 가진다. 또한 DC 이득은 0dB이다. 1.5MHz에서의 감쇠값은 63dB이다.

표 4는 PPF의 레이아웃 후의 시뮬레이션 결과를 정리한 것이다. TT모드에서 전압이득을 0.51dB를 얻을 수 있었고 입력 IP3도 10.76dBv을 얻을 수 있어 블루투스 스펙을 만족시키는 PPF 설계를 할 수 있었다.

3.4 PGA 설계 성능 결과

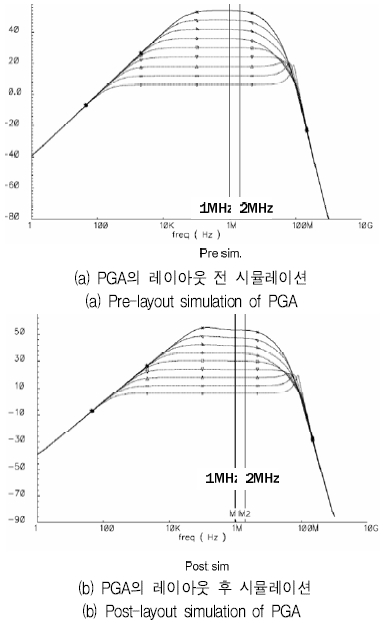

앞서 언급 하였듯이 τ가 작으면 C5·R5>APGA/ fsignal의 조건은 만족하지 않는다. 따라서 이 안정이 된 다음에는 다시 S1=0으로 하여 pole의 위치를 아래로 이동 시켜야 한다. 그림 8(a)은 PGA의 0dB ~ 54dB 이득 범위 상태에서의 PGA의 레이아웃 전 시뮬레이션 결과이다.

그림 8(b)는 PGA의 0dB ~ 50dB 이득 범위 상태에서의 PGA의 레이아웃 후 시뮬레이션 결과이다.

표 5에 PGA의 시뮬레이션 결과를 정리 하였다. 표 5에서 보여지듯이 TT모드에서 전압이득을 6~53dB의 범위로 이득을 가변 시킬 수 있도록 하였고 입력 관련 잡음은 32~41nV/√Hz 얻을 수 있었다. 입력 IP3도 –31~17dBv을 얻을 수 있어 블루투스 스펙을 만족시키는 PGA 설계를 할 수 있었다.

3.5 VCO 설계 성능 결과

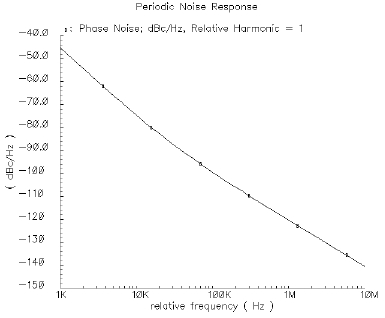

그림 9에서 보는 바와 같이 위상잡음(Phase Noise)이 -120.63dBc/Hz를 나타내고 있는데, 이는 Divide_2를 거치게 되면 위상잡음은 -6dB가 추가되어서 -126dBc/Hz정도를 나타내게 된다. 표 6에 VCO의 레이아웃후의 시뮬레이션 결과를 정리 하였다. 표 6에서 보여지듯이 TT모드에서 주파수 가변범위를 4.394 ~ 5.33GHz의 범위로 맞출 수 있도록 하였고 Kvco는 52~87.4MHz를 얻을 수 있었다. 캐패시터 뱅크 간격도 10.9 ~ 17.6MHz를 얻을 수 있어 블루투스 스펙을 만족시키는 VCO 설계를 할 수 있었다.

Ⅳ. 결 론

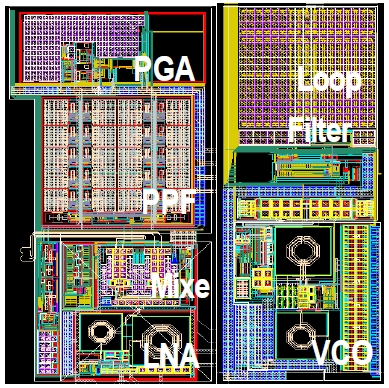

본 논문에서는 Low-IF CMOS 블루투스 수신기를 설계하였다. 믹서는 MGTR을 이용하여 선형성을 향상시켰고, charge injection기법을 사용하여 플릭커 노이즈를 감소시켰다. 또한 Low-IF 수신기구조를 사용하였기 때문에 이미지 문제를 해결하기 위하여 PPF를 사용하였다. 수신기 집적회로 설계는 그림 10에서 보여지는 것과 같이 TSMC 0.18μm CMOS 공정을 사용하였다.

수신기 성능은 표 7에서 보여지는 것과 같이 1.8V 전압에 약 36mA 전류 소모를 타 논문들과 비교하여 상당히 적은 파워소모를 하였으며, 최저 수신감도는 -86dBm, 다른 논문들과 비교를 했을시, 이미지 제거 비율은 63dB로 탁월한 성능을 얻을 수 있었고, iip3는 -13dBm을 각각 얻을 수 있었다.

폐 루프 시, VCO의 위상잡음은 1Mhz 떨어진 곳에서 그림 9에서 보는 것 과 같이 -126dBc/Hz를 얻을 수 있었고 역시 표 7에서 Ref.[2], [3] 타 논문들과 비교해 우수한 특성을 얻을 수 있었다. 또한 본 칩은 mp3스피커, 아이폰 헤드셋, 스마트폰 이어폰 제조기업 등 일반 상용 블루투스가 사용되는 기기에 응용될 수 있을 정도로 ISM밴드 또는 블루투스 스펙을 만족하도록 설계되었다.

Acknowledgments

This work has been supported by Hannam Universiy, 2018

References

- Specification of the Bluetooth System, Version 1.1, Feb.), (2001.

- Seung-Wook Lee, Kang-Yoon Lee, Eunseok Song, and Yeon-Jae Jung, "A single-chip 2.4GHz Direct Conversion CMOS Transceiver with GFSK Modem for Bluetooth Application", in Symposium on VLSI Circuits Digest of Technical papers, Kyoto, Japan, p245-246, Jun.), (2001.

- Paul van Zeijl, and Jan-Wim Th. Eikenbroek, "A Bluetooth Radio in 0.18-um CMOS", in IEEE Journal of Solid-state Circuits, p1679-1686, Feb.), (2002.

- A. Ajjkuttira, C. Leung, E. Khoo, M. Choke, R. Singh, T. Teo, B. Gheong, J. See, H. Yap, P. Leong, C. Law, Itoh, A. Yoshida, Y. Yoshida, A. Tamura, and H. Nakamura, "A fully-integrated CMOS RFIC for bluetooth applications", in Proc. IEEE Int. Solid-State Circuits Conf., p198-199, Feb.), (2001.

- F. O. Eynde, J. J Schmit, V. Charlier, R. Alexandre, C. Sturman, K. Coffin, B. Mollekens, J. Craninckx, and S. Terrijn, "A fully-integrated single-chip SOC for bluetooth", in proc. IEEE Int. Solid-State Circuits Conf., p196-197, Feb.), (2001.

- H. Darabi, S. Khorram, E. Chien, M. Pan, S. Wu, S. Moloudi, J.C. Leete, J. Rael, M. syed, R. Lee, B. Ibrahim, M. Rofuougaran, and A. Rofougaran, "A 2.4GHz CMOS transceiver for blueooth", IEEE J. Solid-State Circuits, 36, p2016-2024, Dec.), (2001.

-

N. Filiol, N. Birkett, J. Cherry, F. Balteanu, C. Gojocaru, A. Namdar, T. Pamir, K. Sheikh, G. Glndon, D. Payer, A. Swaminathan, R. Forbes, T. Riley, S. M. Alinoor, E. Macrobbie, M. Cloutier, S. Pipilos, and T. Varlelas, "A 22mW bluetooth RF transceiver with direct RF moudulation and on-chip IF filtering", in Proc. IEEE Int. Solid-State Circuits Conf., p202-203, Feb.), (2001.

[https://doi.org/10.1109/isscc.2001.912604]

-

C. Durdodt, M. Friedrich, C. Grewing, M. Hammes, A. Hanke, S. Heinen, J. Oehm, D. Pham-Stabner, D. Seippel, D. Theil, S. V. Waasen, and E. Wagner, "The first very low-IF RX, 2-point modulation TX CMOS system on chip bluetooth solution", in Proc. IEEE Radio Frequency Integrated Circuits Symp., p99-102, May), (2001.

[https://doi.org/10.1109/rfic.2001.935651]

- Bonkee Kim, Jin-Su Ko, and Kwyro Lee, "A new linearization technique for MOSFET RF amplifier using multiple gated transistors", in IEEE Microwave and Guided Wave Letters, 10(9), p371-373, Sep.), (2000.

- L. A. NacEachern, and T. Mamli, "A charge-injection method for Gillbert cell biasing", in Electrical and computer Engineering, 1998. IEEE Canadian Conference on Volume 24-28, 1, p365-368, May), (1998.

1999년 2월 : 전북대학교 정보통신공학과(공학사)

2001년 2월 : 전북대학교 정보통신공학과(공학석사)

2010년 8월 : 한양대학교 전자통신 전파공학과(공학박사)

2011년 2월 : 카이스트 박사 후 연구원

2011년 3월 ~ 2018년 12월 : 한남대학교 전자공학과 교수 재직 중