차량 레이더용 77GHz 전력 증폭기 구현

초록

본 논문은 차량 충돌 방지 레이더용 저전력 고이득 77GHz 전력 증폭기를 제안한다. 제안하는 회로는 입력과 단간의 정합을 위한 공액 정합 회로단과 전력이득 증가를 위한 2단 캐스코드 증폭단으로 구성되어 있다. 이러한 회로는 3μm의 최상위 금속 두께 층을 가진 0.18μm Bipolar/CMOS/DMOS(BCD) 1-폴리 4-금속 공정 (fT/fMAX = 100/130GHz)을 사용하였다. 이러한 증폭기는 2볼트 전원전압에서 낮은 잡음지수, 낮은 전력소모 및 높은 전력이득을 가지도록 구현되어 있다. 임피던스 정합에 주로 사용하는 넓은 면적을 가진 인덕터 대신 전송선을 이용하여 전체 회로 면적을 줄였다. 제안하는 전력 증폭기는 최근 연구결과와 비교해볼 때 26.8dB의 가장 높은 전력이득, 45mW의 가장 적은 소비전력, 0.152mm2의 가장 작은 칩 면적, 17.5%의 가장 높은 전력부가 효율 특성과 19.5dBm의 가장 높은 포화 출력 전력 특성 보였다.

Abstract

This paper presents a low-power high-gain 77GHz power amplifier for automotive collision avoidance radar. The proposed circuit consists of a conjugate matching circuit stage to match input and inter-stage, and 2-stage cascode amplification stage to increase power gain. This circuit is designed using 0.18μm Bipolar/CMOS/DMOS (BCD) 1-poly 4-metal process (fT/fMAX=100/130GHz) with the top metal thickness layer of 3μm. This amplifier is realized to have low noise figure, low power consumption, and high power gain at a supply voltage of 2V. We reduced a total circuit area by using transmission lines instead of the bulky inductor for the general impedance matching. The proposed power amplifier showed the highest power gain of 26.8dB, the lowest power consumption of 45mW, the smallest chip area of 0.152mm2, the highest power-added efficiency of 17.5% and the highest saturated output power of 19.5dBm as compared to recently research results.

Keywords:

automotive collision avoidance, radar, 77GHz, Bipolar/CMOS/DMOS(BCD), power amplifierⅠ. 서론

멤스(MEMS, Micro Electro-mechanical System) 기술은 전자 및 초미세 반도체 공정 기술과 기계 기술 등을 이용하여 마이크로 또는 나노 단위의 초미세 부품과 시스템을 설계 및 제작하고 응용하는 기술을 말한다. 이러한 기술은 소형화, 집적화, 저전력화, 고성능, 저가격화 및 고신뢰화의 장점을 가진다. 궁극적으로 멤스 기술은 시스템-온-칩(SoC, System-on-Chip)화를 위한 필수적인 기술이다[1]. 시스템-온-칩 기술은 하나의 칩 안에 일정량 이상의 복잡도를 가지는 다수의 칩의 기능(디지털 회로, 아날로그 회로 및 고주파 회로 기능)을 하나의 칩으로 구현하는 기술을 말하며, 소형화, 집적화, 저전력화, 고밀도 등의 장점을 가진다[1].

멤스 시스템-온-칩 기술은 기존의 고주파 소자에 비하여 저손실, 저전력 동작 및 높은 아이솔레이션(Isolation) 특성을 가진다. 특히 반도체 공정의 적용이 수월하고 소자의 크기 소형화가 가능하다. 두 기술의 장점으로 인해 최근 멤스 시스템-온-칩 (MEMS SoC)에 대한 연구가 활발히 진행 중이다[2]-[9].

본 논문에서는 이러한 기술을 차량 충돌 방지 77GHz 레이더 송신부의 전력 증폭기 개발에 접목하고자 한다. 개발한 전력 증폭기는 3μm의 최상위 금속 두께 층을 가진 0.18μm BCD(Bipolar/CMOS/ DMOS) 1-폴리 4-금속 공정 (fT/fMAX=100/130GHz)으로 설계되어 있다. 임피던스 정합에 주로 사용하는 넓은 면적을 가진 인덕터 대신 전송선을 이용하여 전체 칩 크기를 줄이고자 하였다. 또한 기판 손실을 줄이고 Q 값을 향상시켜 전력 증폭기의 특성을 향상시키기 위해 일부 인덕터와 커패시터를 고주파 멤스 인덕터와 튜너블 커패시터로 각각 사용하였다. 77GHz 초고주파 대역에서 기생 성분들을 최소로 하기 위해 멤스 시스템-온-칩 기술, 초고주파 회로 설계 기술, 레이아웃 기술 등을 연구하였다. 제안하는 증폭기는 최근 발표된 연구결과에 비해 45mW의 가장 적은 소비전력, 17.5%의 가장 높은 최대 전력부가 효율, 26.8dB의 가장 높은 전력이득 및 0.152mm2의 가장 작은 칩 면적 특성을 보였다.

Ⅱ. 회로 설계 및 분석

2.1 차량용 레이더 개요

자동차 레이더를 이용한 기술은 차량용 안전주행 시스템과 다양한 이동체 레이더 센서 시스템에 적용할 수 있다[5]. 특히 차량용 레이더는 움직이는 속도, 물체의 거리 등을 검지할 목적으로 대략 30미터 이내의 물체 검지용 24GHz 대역의 단거리 레이더와 대략 150미터 이내의 물체 검지용 77GHz 대역의 장거리 레이더로 분류된다[5].

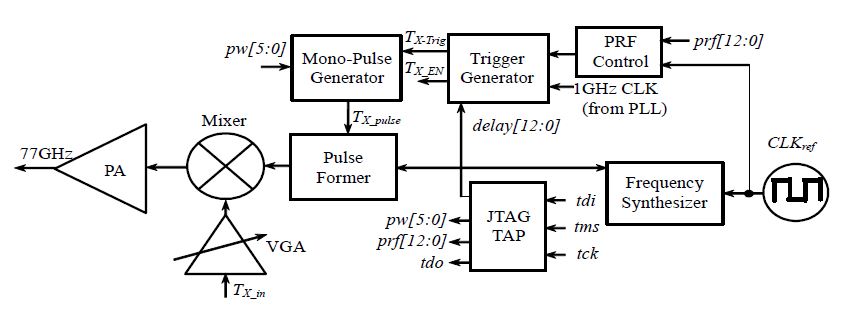

그림 1은 77GHz BCD 전력 증폭기가 적용될 차량 충돌 방지 레이더 송신기 전단부를 나타낸 것이고, 표 1은 이러한 증폭기에 대한 목표 사양을 나타낸 것이다. 이러한 레이더는 차량 전방 150m 이내의 물체를 감지할 수 있다. 이러한 전력 증폭기는 직접 변환 송신부 응용에 적합하다.

2.2 제안하는 회로 및 분석

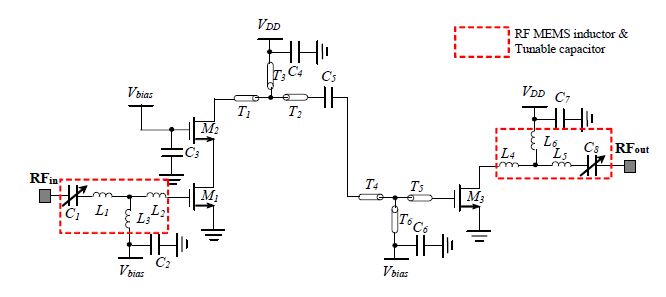

그림 2는 본 연구에서 개발한 77GHz 2단 전력 증폭기를 나타낸 것이다. 3μm의 최상위 금속 두께 층을 가진 0.18μm BCD 1-폴리 4-금속 (1P 4M) 공정 (fT/fMAX = 100/130GHz)을 사용하였다. 기존 증폭기에 일반적으로 사용하는 고주파 인덕터와 커패시터 대신 Q가 높고, 손실이 적은 고주파 멤스 인덕터 및 튜너블 커패시터로 설계하였다. 제안하는 증폭기는 클래스-A(class-A) 모드로서 단간 공액 정합 회로를 가진다. 77GHz의 동작주파수에서 높은 전력이득을 제공하기 위해 캐스코드 구조로 설계하였다. 임피던스 정합에 주로 사용하는 넓은 면적을 가진 인덕터 대신 전송선 T1~T6을 사용하여 전체 회로 면적을 줄였다. 고주파 잡음, 전원 잡음 및 전자기 간섭을 줄이기 위해 디커플링(Decoupling) 커패시터 C2~C4 및 C6~C7을 사용하였다. 전송선 T1~T3은 드레인 영역으로 안정된 직류 전원을 공급하고, 전류가 일정하게 흐를 수 있도록 전송선 길이와 폭의 최적화 설계를 구현하였다. 바이어스 전압(Vbias)에는 전류원 회로를 연결하였고, 이를 통해 MOSFET M1~M3의 게이트 바이어스 전압을 조절하였다. M2 및 M3의 드레인 영역으로 안정된 전원공급과 일정한 전류가 흐를 수 있게 설계하였다. 정량적 분석을 통해 고주파 소신호 등가회로 모델을 유도하고, 그 결과를 시뮬레이션 결과와 비교하였다. 또한 M1의 입력임피던스는 식 (1)로 표현할 수 있다[10].

| (1) |

여기서 전송선의 감쇠 저항 값은 작아서 무시하였다. Cgs1은 M1의 게이트-소스 커패시턴스, Cgd1은 M1의 게이트-드레인 커패시턴스 및 Cgb1은 M1의 게이트-벌크 커패시턴스를 각각 나타낸다.

그림 2의 회로에서 첫 번째 단의 단방향 전력이득은 식 (2)로 표현한다. 커패시터는 금속-절연체-금속 형태를 가지며, BCD 공정 기술을 이용하여 원하는 속도 및 성능을 달성하기 위해서는 기생성분이 최소가 되도록 레이아웃 기술을 적용하였다. 본 연구에서는 트랜지스터들을 빗살-접힘형(Comb-folded) 배열로 구성하여 기생성분의 최소화를 구현하였다. 인덕터 L1~L6와 커패시터 C1 및 C8은 HFSS로 3차원 모델링 후 인덕턴스 값, 손실 저항 및 커패시턴스 값들을 각각 추출하였다. 회로 시뮬레이션은 추출된 값들을 바탕으로 그림 2와 같이 구성한 후 수행하였다.

| (2) |

여기서 fT는 천이(Transition)주파수를 의미한다[8].

표 2는 그림 2에 대한 각 소자 값을 나타낸 것이다. 전력이득을 증가시키고 소비전력을 줄이기 위해 M1과 M3의 W/L=36/0.18이 되도록 최적 설계하였고, M2는 W/L=27/0.18의 값을 가지도록 설계하였다. 전송선의 특성 임피던스는 50Ω을 가지도록 구현하였다.

본 증폭기 설계에서는 임피던스 정합에 주로 사용하는 넓은 면적을 가진 인덕터 대신 전송선을 이용하여 면적 최적화 레이아웃을 하였고, 최소 면적의 전송선을 구현하였다. 표 3은 L7과 L8에 대해 실제 인덕터를 사용한 경우와 T1~T6의 전송선을 사용한 경우에 대한 전체 칩 면적을 비교한 것이다. 즉 전송선(T1~T3)을 사용한 경우와 실제 인덕터(L7)를 사용한 경우, 전송선(T4~T6)을 사용한 경우와 실제 인덕터(Ls)를 사용한 경우를 각각 비교한 것이다.

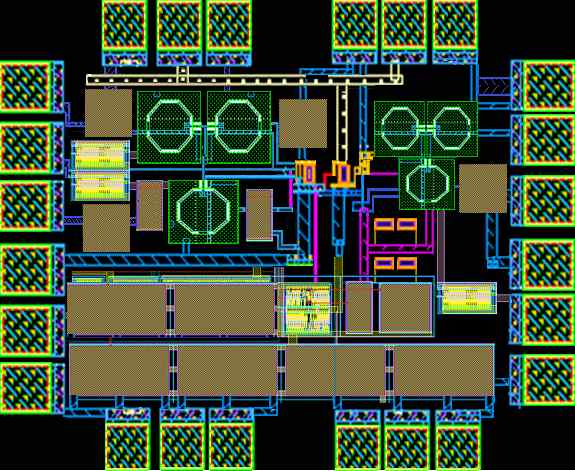

그림 3은 본 연구에서 제안하는 증폭기에 대한 레이아웃을 나타낸 것이다. 본 연구에서 제안하는 전력 증폭기는 0.152mm2의 전체 칩 면적을 보였고, 실제 인덕터를 사용한 경우 0.281mm2의 면적을 보였다. 이러한 결과로부터 알 수 있듯이 전송선을 이용한 방법은 기존 방법에 비해 약 45%의 면적 감소 효과를 보였다.

Ⅲ. 시뮬레이션 결과 및 토의

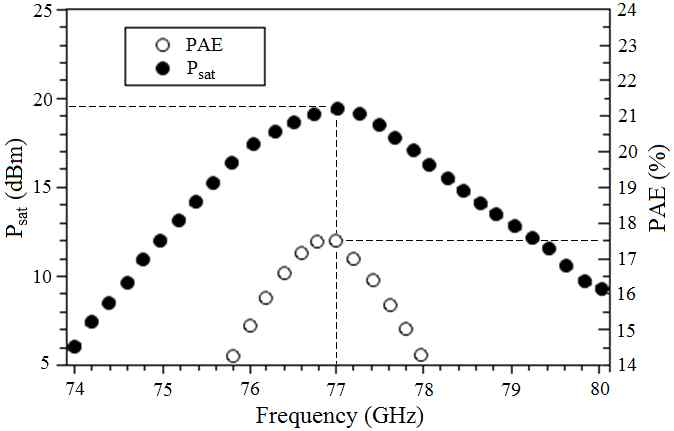

그림 4는 주파수에 따른 전력부가효율(PAE, Power Added Efficiency)과 포화출력전력(Psat) 특성을 나타낸 것이다. 전력부가효율은 전력 증폭기의 순수 전력효율 특성을 나타내는 지표로서, 교류 출력전력에서 교류 입력전력을 뺀 순수 교류 출력전력을 직류 입력전력으로 나눈 것을 의미한다. 74~80GHz에 대해 14.1~17.5%의 최대 전력부가효율 특성과 5~19.5dBm의 포화출력전력 특성을 각각 보였다. 특히 77GHz에서 19.5dBm의 높은 출력전력 특성과 17.5%의 우수한 전력부가효율을 보였다.

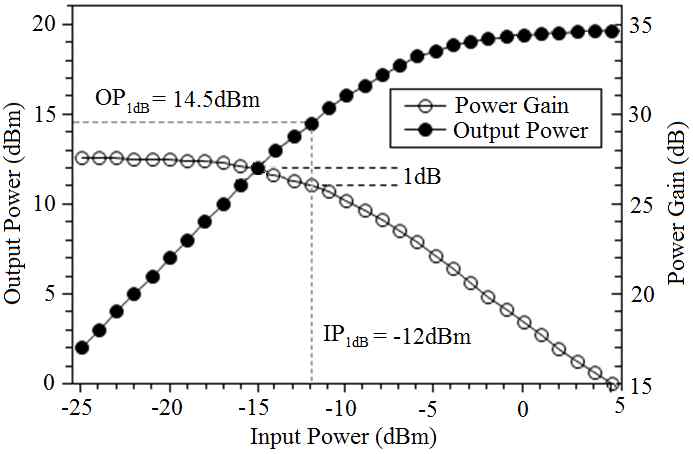

그림 5는 77GHz의 동작주파수에서 입력전력에 따른 전력이득과 출력전력을 나타낸 것이다. 전력 증폭기는 허용 가능한 동적 범위(Dynamic Range)를 가지고 있기 때문에, 입력전력에 따라 출력전력과 전력이득이 변경된다[2][3]. 그림 5로부터 알 수 있듯이 제안한 증폭기는 77GHz의 동작주파수에서 26.8dB의 우수한 전력이득을 보였고, -12dBm의 입력 1dB 압축 점(IP1dB, input 1dB compression point)에 대해 14.5dBm의 출력 1dB 압축 점(OP1dB, output 1dB compression point) 특성을 보였다. 이러한 결과는 제안한 증폭기가 다양한 입력전력 수준에 대해 우수한 전력이득과 출력전력 특성을 가짐을 증명한다.

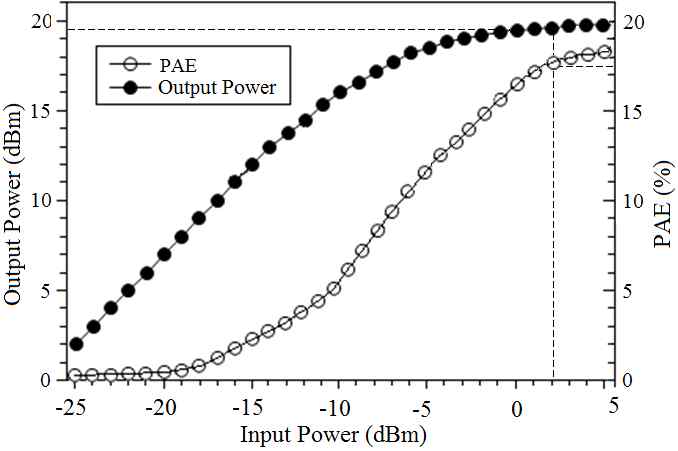

77GHz의 동작주파수에서 전력 증폭기의 입력전력에 따른 출력전력 및 전력부가효율 특성을 그림 6에 나타내었다. 그림 6의 결과로부터 알 수 있듯이 동작주파수에서 19.5dBm의 높은 출력전력과 17.5%의 우수한 전력부가효율 특성을 보였다.

본 연구에서 제안하는 전력 증폭기는 주파수 변조된 연속파(FMCW, Frequency-Modulated Continuous Wave)를 이용한 레이더 시스템에 적용되고 때문에 안테나를 통해 FMCW를 전송함에 있어 우수한 위상 선형성이 요구된다[2][3]. 높은 출력전력과 우수한 전력부가효율 특성이 필요하다.

표 4는 본 논문에서 제안한 77GHz BCD 전력증폭기와 최근 연구결과들을 비교한 것이다. 본 논문에서는 제작공정, 포화 출력 전력, 전력이득, OIP3, 직류 소비전력, 입력/출력 반사손실, 최대 전력부가 효율과 칩 면적을 각각 비교하였다. 넓은 면적을 차지하는 인덕터(L7~L8) 대신 전송선(T1~T6)을 사용하여 전체 칩 면적을 줄이고 선 위상 천이 오차를 줄였다. 또한 고주파 인덕터와 커패시터 대신 Q가 높고, 손실이 적은 고주파 멤스 인덕터 및 튜너블 커패시터를 이용하였다.

표 4의 결과로부터 알 수 있듯이 본 연구에서 제안하는 BCD 증폭기는 최근 연구결과와 비교해 볼 때 26.8dB의 가장 높은 전력이득, 45mW의 가장 적은 소비전력, 17.5%의 가장 높은 전력부가 효율 및 0.152mm2의 가장 작은 칩 면적을 보였다. 또한 19.5dBm의 높은 포화 출력 전력과 –18dB의 낮은 입력 반사손실 및 –19dB의 낮은 출력 반사손실 특성을 보였다.

Ⅳ. 결론

본 논문은 차량용 장거리 레이더를 위한 77GHz BCD 전력 증폭기를 제안하였다. 제안한 회로는 77GHz의 동작주파수와 2V의 전원에서 동작하였다. 이러한 회로는 0.18μm BCD 1-폴리 4-금속 공정 (fT/fMAX=100/130GHz)으로 설계 및 제작하였다. 개발한 회로는 최근 연구결과와 비교해 볼 때 26.8dB의 가장 높은 전력이득, 45mW의 가장 적은 소비전력, 17.5%의 가장 높은 최대 전력부가 효율과 0.152mm2의 가장 작은 칩 면적 특성을 보였다. 또한 우수한 S 파리미터 특성과 우수한 높은 포화 출력 전력을 보였다. 이러한 특성을 바탕으로 향후 장거리 레이더의 전력 증폭기 개발에 적용되리라 기대한다.

Acknowledgments

이 논문은 안동대학교 기본연구 지원사업에 의하여 연구되었음

References

-

T. L. Chen, and S. S. Park, "MEMS SoC: observer-based coplanar gyro-free inertial measurement unit", Journal of Micromechanics and Microengineering, 15, p1664-1673, Jul), (2005.

[https://doi.org/10.1088/0960-1317/15/9/008]

- J. Y. Ryu, "High-Gain Low-Area Power Amplifier for 77-GHz Automotive Radars", International Journal of Applied Engineering Research, 11(2), p934-937, Jan), (2016.

- J. Y. Ryu, "Low-Power Power Amplifier for 77-GHz Automotive Radars", International Journal of Applied Engineering Research, 11(1), p661-663, Jan), (2016.

-

T. Yao, M. Q. Gordon, K. K. W. Tang, K. H. K. Yau, M. T. Yang, P. Schvan, and S. P. Voinigescu, "Algorithmic Design of CMOS LNAs and PAs for 60-GHz Radio", IEEE Journal of Solid-State Circuits, 42(5), p1044-1057, May), (2007.

[https://doi.org/10.1109/JSSC.2007.894325]

- J. Wenger, "Automotive Radar-Status and Perspectives", IEEE Compound Semiconductor Integrated Circuit Symposium, 2(1), p21-24, Oct), (2005.

- G. H. Choi, S. K. Choi, C. H. Kim, M. U. Sung, S. G. Kim, J. H. Lim, H. Rastegar, J. Y. Ryu, and S. H. Noh, "Power Amplifier for Short Range Radar Application of Automotive Collision Avoidance", Proceedings of Conference on Information and Communication Engineering,, 18(1), p765-767, May), (2014.

-

H. H. Choi, J. H. Lim, and J. Y. Ryu, "Development of the Fully-Differential Switched-Capacitor Integrator for the Sigma-Delta Modulator", Journal of KIIT, 13(9), p1-7, Sep), (2015.

[https://doi.org/10.14801/jkiit.2015.13.9.1]

- W. H. Lee, and T. J. Chung, "A 1.485 Gbps Wireless Video Signal Transmission System at 240 GHz", Journal of IIBC, 10(4), p105-113, Aug), (2010.

- Hyun-moon Park, Byung-chan Jeon, and Daehyun Ryu, "A Study for Context-Awareness based on Multi-Sensor in the Smart-Clothing", Journal of IIBC, 13(3), p71-78, Jun), (2013.

- B. Razavi, "Design of Analog CMOS Integrated Circuits", New York, McGraw-Hill, Inc, p9-32, (2001).

- D. H. Kim, J. H. Kim, S. K. Eom, M. S. Lee, and K. S. Seo, "77 GHz Power Amplifier MMIC using 0.1μm Double-Deck Shaped(DDS) field-plate gate AlGaN/GaN HEMTs on Si Substrate", CS MANTECH Conference, p241-244, 19-22 May 2014.

-

J. T. Oh, K. B. H. Ku, and S. C. Hong, "A 77GHz CMOS medium power amplifier with transmission line transformers for multi-mode automotive radar system", 2013 Asia-Pacific Microwave Conference Proceedings, p769-771, 5-8 Nov. 2013.

[https://doi.org/10.1109/APMC.2013.6694925]

1982년 : 한양대학교 전자공학과(공학사)

1990년 : 일본 동경공업대학교 물리정보공학 졸업(공학석사)

1993년 : 일본 사이다마대학교 생산정보공학 졸업(공학박사)

1993년 ~ 1998년 2월 : 한국전자통신연구소 위성방송시스템연구실 선임연구원

1998년 3월 ~ 현재 : 안동대학교 전자공학과 교수

관심분야 : 디지털방송시스템, DSP, 반도체회로설계 및 검사

1993년 2월 : 부경대학교 전자공학과(공학사)

1997년 2월 : 부경대학교 전자공학과(공학석사)

2004년 12월 : 애리조나 주립대학교 전기공학과(공학박사)

2009년 3월 ~ 현재 : 부경대학교 정보통신공학과 교수

관심분야 : 시스템-온-칩 설계, 고주파 회로 설계, 임베디드 시스템 설계